实验室做一个逆变器平台,24V输入,交流220V输出。先前的版本前级采用全桥升压,后级全桥逆变。后来在论坛上看到了兴华能的贺岁版推挽前级,觉得布局精致,堪称工艺品。又想到前级低压输入,推挽结构确实有优势。于是决定参照布局做一款5000W推挽前级。板子采用3525控制,4个ETD49变压器,单个变压器功率最大1500W设计,4个变压器原边并联,副边串联,这样就解决了原来单个变压器实现困难的问题。具体结构见下图

做出来还是觉得没有兴华能的好看,没有人家的布局紧凑。这个就不说了,毕竟大师就是大师。下面主要说说波形。

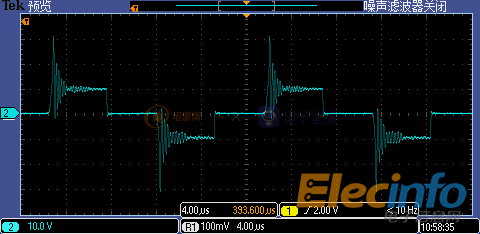

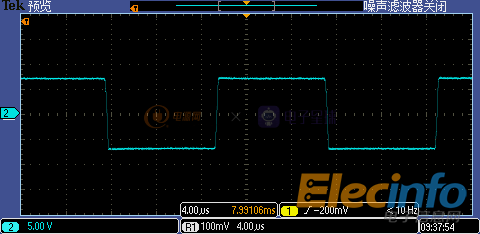

问题主要就是:在整流二极管前有着很大的尖峰。下面是没有接输出滤波电感和输出滤波电容时变压器副边输出,也就是整流二极管前的波形:

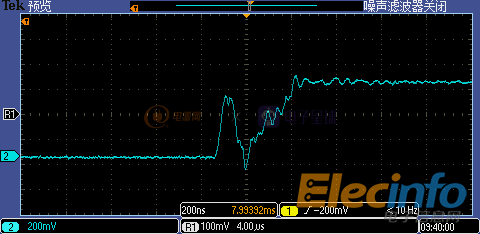

输入电压20V,占空比30%左右时,出现这样的尖峰。图中波形衰减50倍,可以看到输出500V时,有1500V电压尖峰。由于尖峰太大,将输入改为15V,尖峰为1000V左右,形状基本一样,对应mos的Vds波形如下

可以看到,在mos关断时,漏感造成的尖峰倒是不大(图中那个类似于正弦的震荡)因为前面在mos处加了RCD吸收电路,但在另外一个管子开通时,也就是上个管子电压将要到达2倍Vin时,上个管子会有电压尖峰(图中的尖峰)。

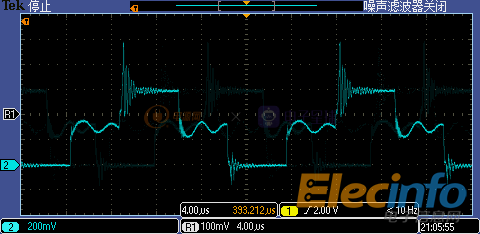

后来加上了后级的滤波电路,电感800uh,电容两个470,波形好一点,但依然很不理想如下

基本上时正常波形的两倍,1200V的管子都危险。

于是就很郁闷了,这个尖峰和论坛里大家遇到的不是一个问题,大家遇到的都是漏感处,也就是关断时的漏感引起的尖峰,而我则是下一个管子开通时对另一个管子的尖峰。

论坛里由大师们在整流前串联谐振电容的,我也试了一下。串联上图所示一大堆,9个474、630V电容,波形没有一点改善。

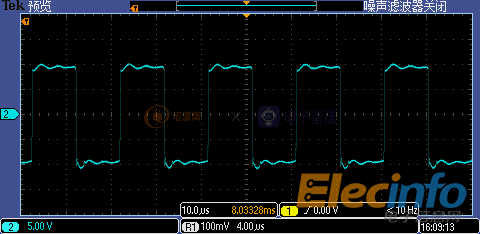

后来,偶尔在整流二极管后就近接了一个CBB小电容,在占空比等于50%时,波形很好,具体见下图:

在这里就近加一个103的电容,50%占空比时,波形:

这是mosVds波形,输入20V,可以看到很理想。下面是整流前波形,

这是mosVds波形,输入20V,可以看到很理想。下面是整流前波形,

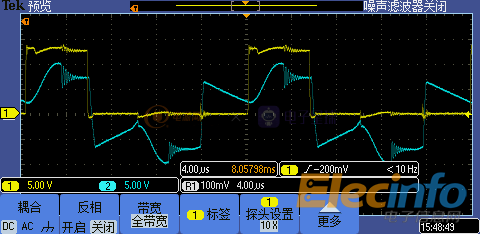

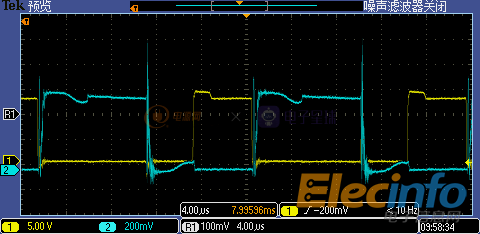

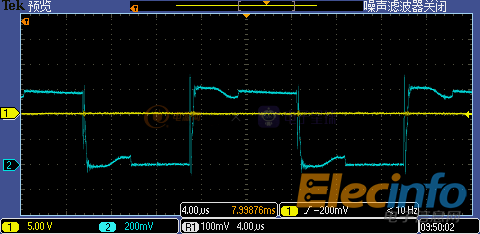

在这种情况下进行了3000W实验,效率89%,现在不怎么关注效率,先解决尖峰问题。但是这种情况下,真空比小于50%时,输出波形会出现严重畸变,还是占空比等于30%时,整流前波形如下:

如上图,黄色是PWM驱动,蓝色是变压器次级输出。可以看到,在死去时间内,变压器输出不为0.也就是说,在整流后加电容,只适合占空比等于50%(实际3525输出的49%)情况,其他情况波形畸变。

另外发现,虽然这个电容位于整流滤波电容处,但是对波形有很大影响,电容过大后直接类似于输出短路。这个问题有待解决。

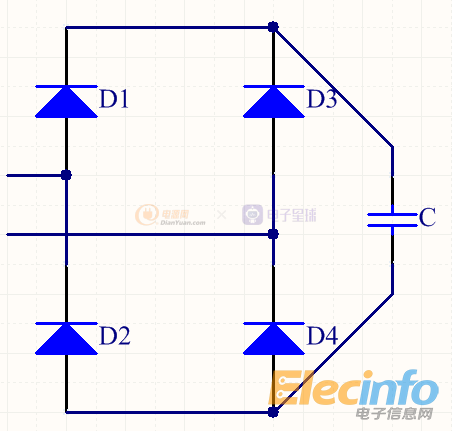

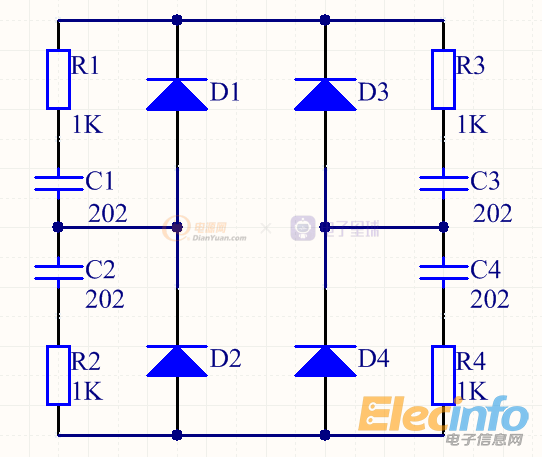

由于要做闭环,上面的解决方案就放弃了,继续抑制尖峰。再尝试了老寿先生的谐振电容失败后,只能加吸收电路。如下图:

在整流二极管处加吸收电路,输出尖峰问题如下:

上图是输出电压波形,可以看到尖峰小了很多,仍然是衰减50倍,在400V多输出时,尖峰抑制在500多V,关键是在占空比等于30%时,波形没有畸变。

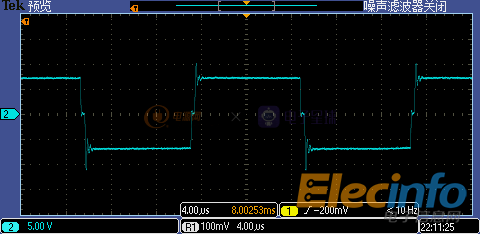

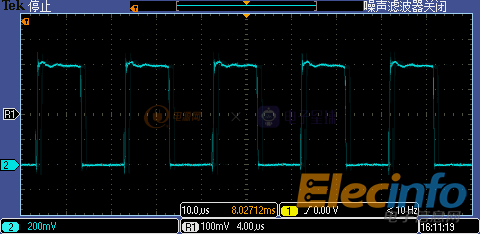

下面是占空比等于50%时整流前输出

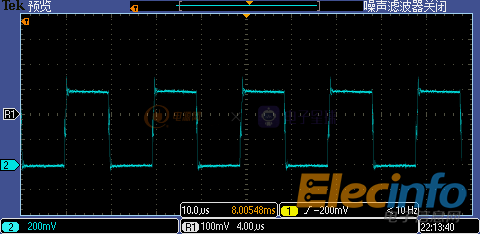

下图是对应mos波形

上图是对应mos波形。尖峰不大,(衰减50倍) 这个方法可以抑制尖峰,但是吸收电阻发热严重,我用两个5W电阻并联,依然很烫。。。。。

论坛上好多人说推挽加全桥整流不宜闭环,如果开环的话,现在基本没问题了,但是闭环就真的做不了了??大家帮忙解决下,眼看就过年了。。。。