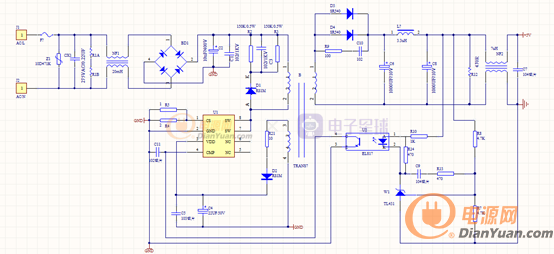

12V1.5A方案设计 芯片:PN****

1、输入:100-264V

2、输出:12V1.5A

3、效率:84%(5级能效80.2%,为便于生产故选84%)

4、Vcc:14V(选择VCC开启阀值)

5、工作频率:60K (PFM)

这里讲下PFM PFM优点空载时处于降频模式也就降低了我们的开关损耗和导通损耗及IC负载低于一定的时候进入睡眠模式就是IC规格书中写到的静态电流稳态电流,就是说降低了IC的消耗,缺点是纹波动态响应没有PWM好

6、Dmax:0.45 占空比大于0.5会带来环路不稳定的缺陷所以大家都控制在0.5以内

7、ΔB:(Bs-Br)*n=ΔB=(390-55)*0.6=0.2T Bs:390mT/100℃ Br:55mT 各家参数不同安全值取0.3Tmax

CCM连续模式,电流不为零,ΔB变小,n取60% ΔB取值个人习惯

9、Vinmin、Vinmax计算:

Vinmin=Vacmin*1.2=90*1.2=108V

Vinmax=Vac*1.414=374V

10、磁芯选择:

AP=【(Po/η+Po)*10000】/(2*ΔB*ƒ*J*Ku)

=【(18/0.84+18)*10000】/(2*0.2*60*1000*400*0.2)

=394285.7/1920000

=0.205cm4

ƒ=60*1000 (Hz)

J电流密度=400

Ku绕组系数=0.2

EF25 AP=0.2376cm4 AE=51.8 mm2

设计经验:1、Ae值小效率低温度高,磁芯面积小扇热差,罐装磁芯辐射好,长宽磁芯漏感小。

2、Ae=Po*2 本人更喜欢这个公式Ae=18*2*1.4=50.4mm2

取:EF25:AE:51.8mm2

当然以上2种都可以选择。