所有PWM转换器都有寄生元件,可导致必须适当抑制的振铃波形。不这样做,半导体元件就可能失效,噪声水平将比要求的更高。本文将介绍用于备受青睐的反激式转换器的最常用的RCD箝位电路,及其设计公式。

没有缓冲器,反激式变压器振铃的漏感会随电路中的杂散电容产生,生产大幅度高频波形,如图所示1。

许多应用笔记和设计没有解决这个问题,忽略了振铃波形和转换器的运行。有两个问题:首先,在FET漏极有过大的电压,可能导致雪崩击穿并最终导致器件故障。其次,振铃波形将成为辐射和传导到整个电源、负载和电子系统,引起噪声问题甚至逻辑错误。振铃频率还将以辐射和传导EMI是形式表现为EMI频谱的峰值。

图1. 反激式转换器漏极电压。

在大多数设计中,这是不可接受的,必须增加电路元件抑制振铃(使用一个RC缓冲器),或者箝制电压(用RCD箝位),或者两个都用。这些网络的设计是测量和分析的结合,可以确保耐用和可靠的效果。

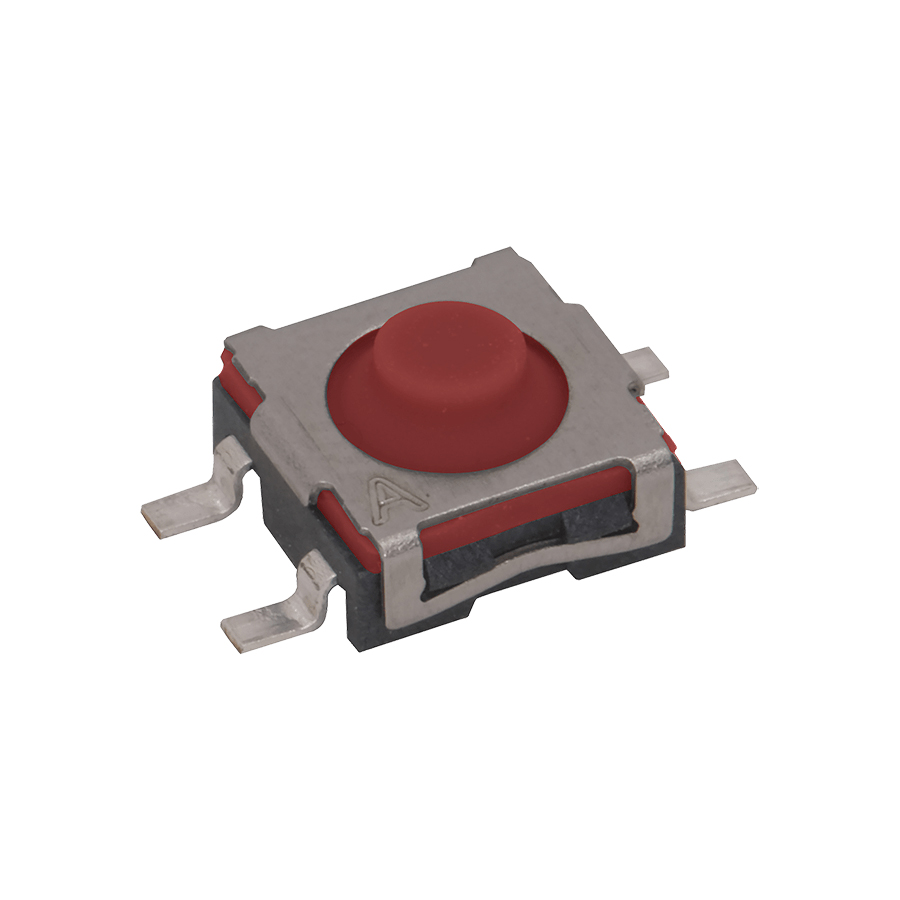

反激式转换器的初级RCD箝位

图2给出了一个RCD箝位电路,当一个RC缓冲器不足以有效防止开关过压时,它可用来限制FET漏极的峰值电压。一旦漏极电压超过箝位电容器电压,RCD箝位即靠吸收漏感电流工作。采用一个比较大的电容器可保持一个开关周期的电压恒定。

RCD箝位的电阻器总会浪费功率。即使在转换器上有很小的负载,电容器都将进行充电高达从转换器次级反射的电压,即vf。由于负载增加,更多能量将流入电容器,而电压将提高更多,即vx,它在理想的方波反激电压之上。该波形定义了这些电压,如图2所示。

图2. 带有初级RCD箝位的反激式转换器。

设计步骤1——测量漏感

重要的是测量反激式变压器的漏感,然后再设计缓冲器。不要不只猜测电感值,而是要明白磁性元件制造商的最差规格对设计来说经常不够精确。另外,漏感是频率相关的,必须在适当的频率值进行测量。

设计步骤2——确定峰值箝位电压

现在必须决定功率MOSFET可以容许多少电压,并计算在箝位电平条件下箝位将耗散的功率量。与漏感L相关的功率,及关断时的当前最差电流Ip可以表示为:

对RCD缓冲器的分析出现在论文和大量应用笔记当中。假设没有杂散电容要充电,所有泄漏能量都被传导到来自漏感的缓冲电容器。假定电容器足够大,其逻辑值在在一次开关周期期间没有显著变化。

利用这些假设,RCD箝位的功耗可以表示为存储在电感器中的能量,具体如下:

换句话说,我们让开关上的箝位电压升得越高,总功耗越低。但是当然,我们必须对此进行平衡以防止总电压出现在功率FET两端,因此我们不能任意降低功耗。

一个典型设计可用于电压vx等于1/2反激电压。在这种情况下,功耗等于存储在漏感中能量的三倍,它不是一个立即可见的结果。然而,这是一个保守的估计。它没有解释电感器的有损放电,也没有解释杂散电容。实际上,由于这些结果,该设计的箝位损失将比预期的更少。

高压离线设计这些经常限制使用一个最高电压为650或700V的FET,电压vx将将很难限制所设定的最大输入电压、最大电流和FET击穿电压。不要超过FET规定的Vds,意识到击穿可能随温度变化。一些设计人员依赖于FET的雪崩能力,让它有规律地超过击穿电压。这不是为可靠的电源设计推荐的。

设计步骤3——选择箝位电阻器

缓冲器的电容器需要足够大,以保持一个相对恒压,同时吸收泄漏能量。除了这一考虑,其逻辑值要求不高,当缓冲器正常工作时不会影响峰值电压。

电阻器在确定峰值电压vx方面是至关重要的元件,因此需要根据以下公式选择:

一个大数值电阻器将减缓箝位电容器的放电,有助于电压提升到更高值。一个小数值电阻器将导致较低的箝位电压,而功耗将增加。

设计步骤4——计算功率损耗

现在缓冲器设计已经完成,但是我们经常还需要知道上述公式中,除了最差条件电流Ip,电流的功耗是多少。使用以下公式计算某一给定峰值电流I和漏感L的已知缓冲器的电压上升。

vx是电压上升值,高于反激电压,可以表示为:

功耗可以表示为:

设计步骤5——实验验证

设计的实验验证是必不可少的,因为将出现没有计入公式的结果,你的电路将出现非理想的元件。图3所示为箝制FET漏极电压峰值电路的效益。

图3. 带有初级RCD箝位的反激式转换器漏极电压。

该数值还给出了一个RCD箝位限制。在箝制周期结束之后,电路恢复振铃。采用理想的元件,这将不会发生。不过,RCD箝位的二极管有一个有限的反向恢复时间,有助于漏感电流流入二极管的相反方向,可导致振铃。RCD缓冲器各种类型二极管选择至关重要。它必须尽可能的快,具有合适的额定电压。

这个振铃的严重程度将取决于RCD二极管两端反向施加的电压。你允许的箝位电压爬得越高,功耗就越低,电压越高且dv/dt施加在二极管上,振铃将增加。

通过采用RC缓冲器随后的振铃可以再一次被抑制。

总结

RCD箝位电路对所有反激式转换器非常有用,可以减少功率FET上的压力。要确保箝位的目的是将最差工作条件下(高电压和最大电流极限)的电压限制低于元件的额定电压。本文中的设计公式排除了来自箝位设计的猜测。

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。

| 微信关注 | ||

|

| 技术专题 | 更多>> | |

|

| 2024慕尼黑上海电子展精彩回顾 |

|

| 2024.06技术专题 |