摘要 针对滞环恒流大功率LED驱动芯片,提出一款高性能电流采样电路。该电路采用高压工艺,可承受最高达40 V的输入电压。通过分析滞环控制的特点,采用串联电阻采样技术,结合匹配电流源结构,在保证响应速度和采样精度的同时,降低了电路的复杂度。电路中加入输入电压补偿电路,进一步提高了恒流控制的精度。在Cadence下的仿真结果表明,电路可在800 kHz的频率下正常工作,采样精度达99.78%;当电压从15V变化至35V时平均负载电流误差为0.81%;输出电压范围为0~5V。

当今照明领域,LED凭借其寿命长、功耗低、无污染等优点成为未来发展趋势。然而,要针对不同的应用场合,分别设计一个独特的芯片,目前情况是不可行的。因此,能够使电源与负载相互独立的电源管理芯片被广泛应用。在这些芯片中,无论是电压还是电流控制模式,都会通过检测电感电流进行过流保护。在电流模式中,采样电流还被用作环路控制。

提出的电流采样技术用于一种滞环恒流控制大功率LED驱动电路中,除具有环路控制与过流保护的功能外,还具有电压补偿的功能及结构简单的特点。

1 采样方式的分析与选择

1.1 现有采样技术

表1中列出了现有的几种电流检测技术并列举了其优缺点。文献对其进行了详细介绍。

1.2 滞环控制原理分析

图1是滞环控制电路框图。LED驱动电流的变化反映在Rsense两端的压差变化上。滞环电流控制模块内设两个电流阈值Imax和Imin,当电路接上电源时,功率管打开,电源通过Rsense、负载LED向电感L充电,驱动电流上升。当电流>Imax时,控制电路输出低电平关闭功率开关管。此时电感通过负载LED、Rsense和肖特基二极管放电,电流下降。当驱动电流<Imin时,控制电路输出高电平打开功率开关管,重复上一个周期的动作。通过这种方式控制电路将驱动电流限制在Imax与Imin之间周期性变化,使流过LED的平均驱动电流值恒定。

可以看到,滞环控制电路使用的是串联电阻采样技术。从表1可知,串联电阻技术的功耗很大,同样具有高精度且无损耗的Sensfet似乎更胜一筹。不过,Sensfet技术只能检测功率管打开时的电流变化情况,而无法检测功率管关断期间的电流变化。因此无法在需要始终对电流进行采样检测的滞环控制电路中使用。同时,由于输入电压较高,串联电阻所消耗的功率在整个电路功率中所占比例也降低了。

2 电路设计

图2是电路采样电路结构图。Rsense为采样电阻,R1=R2=R;Mp1、Mp2、Mn1、Mn2组成的电压镜和Mp9反馈管组成匹配电流源作为电流检测电路。其中Mp1与Mp2相互匹配并被偏置在饱和区,Mn1与Mn2是两个相同且非常小的电流源,以保证流过Mp1与Mp2的电流相等从而使其具有相等的VSG。

由于Vin>Vcsn导致I1与I2不相等。采样电流Is即为这部分"多余"电流,大小为

式(1)中,实际流过Rsense的电流为IL+I2.因为I2的大小低于电感电流的10-4倍,其影响可以忽略不计。

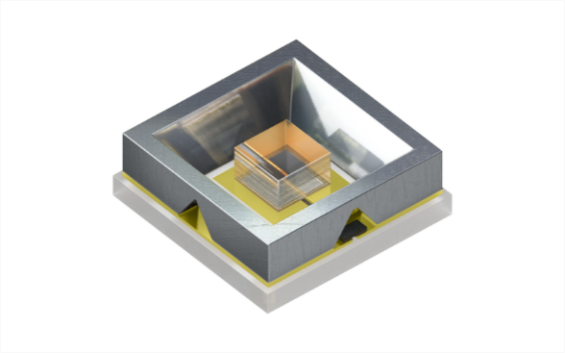

图4为实际电路图。Vin与Vcsn为精确采样电阻Rcsn两端电压,输入范围8~40 V;Vcc为芯片内部5 V稳定电源。

在实际电路中,VA对VB的匹配度直接影响采样精度。图3为简化的小信号模型。

应用KCL定理,得到

其中,ro4、ro3为 VB''、VA''处的等效输出电阻。设 gm1ro3=gm2ro4=AV,且 Mp5为电流镜,增益约为1,综合式(3)到式(5):

δ是一个分子为 的微小值。由式(6)可以看出,当gm1ro2或gm2越大,VA与VB的匹配度越高,电流采样越精确。值得注意的是,式中出现gm1ro3的平方项,这意味着可以用较小的增益达到高精度。但是,耐压5 V的低压管无法在高输入电压下正常工作,电路中必须使用大量耐压40 V的高压管。然而高压管的增益与等效输出电阻很低,无法满足电流采样电路的精度要求。

的微小值。由式(6)可以看出,当gm1ro2或gm2越大,VA与VB的匹配度越高,电流采样越精确。值得注意的是,式中出现gm1ro3的平方项,这意味着可以用较小的增益达到高精度。但是,耐压5 V的低压管无法在高输入电压下正常工作,电路中必须使用大量耐压40 V的高压管。然而高压管的增益与等效输出电阻很低,无法满足电流采样电路的精度要求。

为使低压管能在高压输入中也正常工作,电压镜采用了高低压器件混用的共源共栅结构。Mp1、Mp2、Mn1和Mn2为低压管;Mp3、Mp4、Mn3和Mn4为高压管。一方面,高压管作为共源共栅器件增大了输出电阻;另一方面,它承受了大部分压降,以保护低压管不被击穿。不过,共源共栅结构带来另一个问题。串联电阻R2令Mp2和Mp4之间的次极点更靠近原点,使系统变得不稳定。为消除该极点带来的影响,在共源共栅结构的输出端加入补偿电阻R5和电容C,引入一个零点并使主极点更低。

高压管Mp5~Mp10为匹配电流源的输出级,主要起隔离缓冲的作用,电流镜结构避免了增加新的极点。分流结构Mp7、Mp8将Mp5始终偏置在饱和区,从而允许流过Mp9与Mp10的电流最低降至0 A,使电路在空载时可以输出地电压,为芯片的进一步设计提供了方便。

P1~P12为保护管,防止低压管因漏源或栅源电压过高而被击穿。

高压管Mp11、Mp12、Mn7与R4构成了电压补偿电路。在前述的工作原理中,电路通过将电流限制在阈值Imax和Imin间周期变化达到恒流控制的目的。其中电源向电感的充、放电过程中,充电速率与输入电压成正比,放电速率和芯片的延迟则与输入电压无关。这一差异导致了在输入电压变化时,电流会因在固定的延迟时间中具有不同的上升斜率和相同的下降斜率,使实际电流峰值I''max升高,影响平均电流值。该补偿电路通过将与输入电压成正比的电压Vb2转换为与输入电压成正比的电流Ic,使流过R3的采样电流Isense对输入电压具有正相关性,从而在输入电压升高时令电流阈值Imax、Imin降低,抵消因电流上升斜率提高对平均电流带来的影响。

3 仿真结果

为验证文中提出的电流采样电路的功能,结合滞环控制电路及外部负载在Cadence中进行了仿真。图5为输入电压20 V时采样电流、电压与负载电流的关系。由图可见,采样电流与采样电压随负载电流同相周期性变化,周期约为1.2μs.

经过测试,当负载电流从0.4 A变化至1 A时,电路采样精度最低为99.78%,理想的工作电流为0.6~0.8 A,精度高达99.96%.

表2为不同输入电压下负载电流的峰-峰值。由表中数据计算,在输入电压由15V变化至35V的过程中,负载电流的最大误差仅为0.81%.

图6为外接电流源在0~1.2 A之间跳变时采样电路输出电压的波形。图中输出电压范围为0~5 V,为整颗芯片设计过流保护、开路保护等其他电路提供了方便。

4 结束语

设计了一款适用于滞环控制结构的电流采样电路。使用匹配电流源技术以很少的器件数量和简单的结构,实现了耐高压高精度的目的。端到端的输出电压范围,则使整颗芯片中其他电路的简化成为可能。电路中使用的电压补偿技术,使负载电流与输人电压的相关性大大降低。

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。

| 微信关注 | ||

|

| 技术专题 | 更多>> | |

|

| 2024慕尼黑上海电子展精彩回顾 |

|

| 2024.06技术专题 |