目前,直接模拟合成法、锁相环合成法和直接数字合成法是频率合成的主要3种方法。直接模拟合成法利用倍频(乘法)、分频(除法)、混频(加法与减法)及滤波,从单一或几个参数频率中产生多个所需的频率。该方法频率转换时间快(小于100 ns),但杂散谱太多,难以抑制。锁相环合成法通过锁相环完成频率的加、减、乘、除运算。该方法结构简化、便于集成.且频谱纯度高,目前使用比较广泛,但存在高分辨率和快转换速度之间的矛盾,一般只能用于大步进频率合成技术中。直接数字合成(DDS)是近年来迅速发展起来的一种新的频率合成方法。它的优点主要是输出频率相对带宽较宽,频率转换时间短,频率分辨率极高,相位变化连续,输出波形的灵活性,并且DDS中几乎所有部件都属于数字电路,易于集成,功耗低、重量轻、体积小、可靠性高,且易于程控,使用相当灵活,因此性价比极高。DDS也有局限性,主要表现在:输出频带范围有限,输出杂散大。

1 DDS工作原理

DDS的基本原理是利用采样定理,通过查表法产生波形。DDS的结构有很多种,其基本的电路原理可用图1来表示。

相位累加器由N位加法器与N位累加寄存器级联构成。每来一个时钟脉冲fs,加法器将频率控制字k与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。

目前DDS芯片有很多,但考虑到杂散的抑制以及频率的精度,所以选用的是AD9858芯片。AD9858的工作频率最高可达1 GHz,由于该芯片在时钟输入端提供有二分频器,因而其外部时钟最高可达2 GHz。AD9858内部集成有10位数模转换器,其频率分辨率(即频率累加器位数)为32位,可输出高达450 MHz的信号。而其内部集成的可编程快锁充电泵(CP)和150 MHz的鉴相器(PFD)使其非常适合于高速DDS和锁相环结合应用的场合;同时,它还提供有模拟混频器,可适用DDS、PLL和混频器相结合的应用场合。此外,AD9858的杂散抑制性能和谐波抑制性能也非常突出。

2 电路设计

本方案主要有振荡器、分频模块、AD9858、低通滤波器、环路滤波器、YTO驱动电路组成。利用DDS替代小数分频实现频率的微步进。

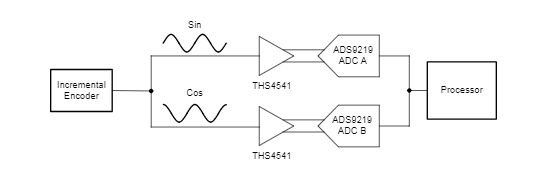

2.1 硬件原理工作原理框图如图2所示。

YTO振荡器输出作为锁相环路的反馈信号,由于AD9858的时钟最高可达2 GHz,所以反馈信号须经过四分频器后才能作为AD9858的参考时钟fsysclk,参考时钟fsysclk首先经过内置的2分频作为DDS的采用时钟。CPU根据YTO理论振荡频率计算出频率控制字,然后送给AD9858频率控制字寄存器,AD9858的输出的频率f0经过150 MHz低通滤波器后和频率参考fr进行鉴相,这里鉴相器用的是AD9858内部集成的鉴相器,鉴相器输出的是电流信息,它是由内部集成的可编程快锁充电泵(CP)来提供的,这个电流不能直接来驱动YTO,所以经过二阶的无源环路滤波器转换成误差电压,经YTO驱动电路后来控制YTO调频线圈,来锁定YTO的频率。

2.2 AD9858的控制及软件流程

AD9858有2种工作模式:点频模式和扫描模式。点频模式,只要将控制寄存器(CFR)和频率控制字(FTW)配置完毕,就可打开该功能。其中控制寄存器(CFR)是一个32位的寄存控器,有4个字节,分别对应的地址为0x00,0x01,0x02和0x03。本方案采用AD9858内置150 MHz鉴相器,初始化时配置鉴相器位和极性位,关闭模拟混频器。

频率调节字的计算公式:

频率控制字(FTW)=fox232/fsysclk (f0:输出频率fsysclk:参考时钟)

AD9858的控制芯片选用XILINX公司的XC95144PO100,由CPU通过FPGA将数据写入到AD9858的片内数字寄存器,可以对AD9858进行灵活控制,软件流程如图3所示。

3 性能分析

3.1 本方案的优点

DDS是近年来迅速发展起来的一种新的频率合成方法,它相对于以前的频率合成方法有众多优点。

1)输出分辨率小,AD9858(参考时钟频率fc=600 MHz)的相位累加器为32位,分辨率为0.14Hz。

2)输出频率变换时间小:一个模拟锁相环的频率变换时间主要是它的反馈环处理时间和压控振荡器的响应时间,通常大于1 ms。而AD98 58的频率变换时间主要是DDS的数字处理延迟,通常为几十个ns。

3)调频范围大:一个负反馈环的带宽输出参考频率决定了模拟锁相环的稳定的调频范围;整片的DDS合成器是不受稳定性的影响的,在整个Nyquist频率范围内是可调的。

4)相位噪声小:DDS优于PLL的最大优势就是它的相位噪声。由于数字正弦信号的相位与时间成线形关系,整片的DDS输出的相位噪声比它的参考时钟源的相位噪声小。而模拟锁相环的相位噪声是它的参考时钟的相位噪声的加倍。

5)设计方便:整片DDS包括了信号D/A变换器,在系统设计时易于实现,而且现在的DDS不再需要专门的射频设计,简单的数字控制减少了硬件的复杂性。

3.2 本方案杂散性能分析

杂散来源主要有DDS的杂散输出和PLL鉴相频率fr的泄漏。由于DDS的杂散输出较丰富,当杂散分布在环路带宽以内时,由于PLL的倍频效应使带内的杂散抑制比恶化:

S=20lg(N)dB其中:N为PLL的分频比;

当DDS的杂散位在PLL环路带宽以外时,受到环路的抑制,从而使杂散抑制比改善:

S=20lg(N)dB

理论上,DDS的输出杂散由下式决定:

SQR=1.76+6.02B+20Log(FFS)+10Log(Fsos/Fs)(dB)

其中:B是输出的DAC的位数

FFS是使用DAC满刻度的百分比

Fsos是过采样速率

Fs是奈奎斯特速率

例如:对与AD9858DDS,输出满刻度0.7的150 MHz,时钟为900 MHz,其杂散为

SQR=1.76+6.02x104-20log(0.7)+10log(900/300)=63.63(dB)

4 测试结果

本系统的重点和难点主要是考察AD9858输出的杂散指标。测试条件在AD9858参考时钟600 MHz,DAC输出150 MHz。实验的结果如下图4所示。近端杂散优于-80 dBc和AD9858的资料相符,满足设计要求。

5 结束语

随着数字电子技术的发展,直接数字频率合成得到了日益广泛的应用,DDS作为频率合成技术倍受青睐,但是也存在一些问题。随着数字技术的发展,相信DDS会有更为出色的表现。

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。

| 微信关注 | ||

|

| 技术专题 | 更多>> | |

|

| 2024慕尼黑上海电子展精彩回顾 |

|

| 2024.06技术专题 |