中心议题:

•PDP的显示原理、PDP为何较耗电?

•PDP电源管理方案

解决方案:

•放电需要高位能,须使用较能耐高压的功率型MOSFET开关

•须准备较多种运作电压准位

•需要更讲究散热方面的设计

PDP的显示原理、PDP为何较耗电?

在此以逐步的方式来说明PDP的显示原理,相信各位都看过打雷吧?雷电直接从云层落到地面,所经过的路径是空气,要让原本不适合导电的空气成为电流流经的导体路径,自然要有很高的电压作为引力,此即是所谓的电弧放电。

在日常生活中有许多应用即是电弧放电的应用,例如防身用的电击棒,以及照明用的日光灯管(也称萤光灯),灯管的左右端各是一个电极,管内注入水银蒸汽(或称汞蒸气、水银气体),并在灯管内壁涂佈萤光物质,之后将灯管密封(以防蒸汽外洩),一旦电极两端通上电压,就会迫使管内的水银蒸汽成为两端的导电体、导电路径(电浆状态),形成小型化的电弧放电,放电的结果会产生紫外光(UV),紫外光照射至管壁内的萤光物质,便会向管外呈现出可见的照明光。

事实上霓虹灯的作法也与此相同,只是向外发散的可见光不是白光,而是各种不同的颜色,每个光管发出一种颜色,不同颜色使用不同的萤光物质。

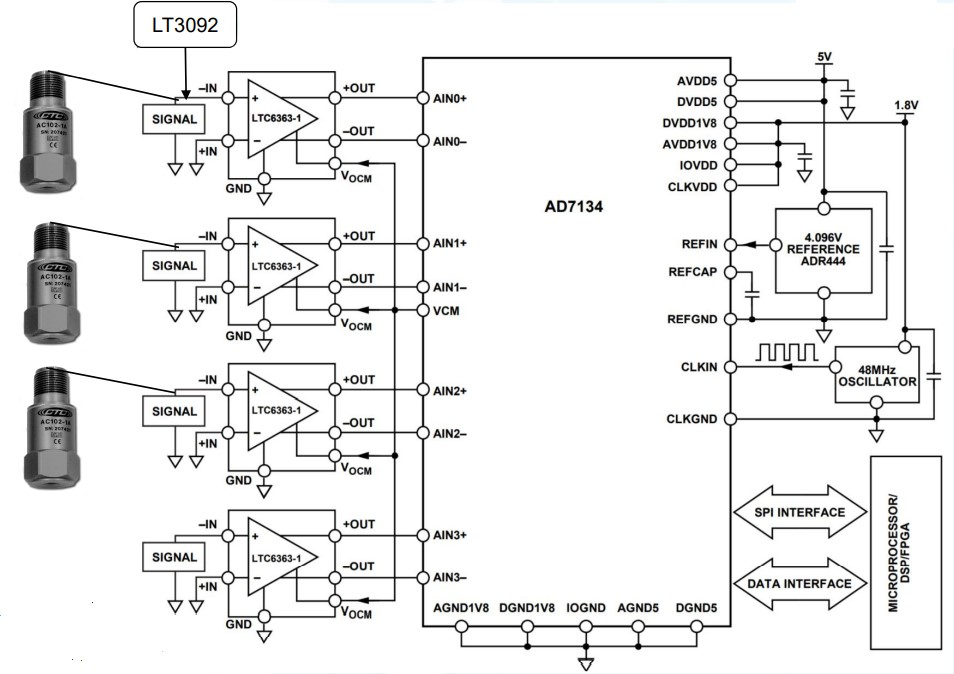

图一 Fairchild(快捷半导体)在PDP电路系统中所能提供的组件方案图(深色部位)。

瞭解日光灯的道理后就能轻易地理解PDP的显示原理,PDP其实就是将日光灯管的尺寸缩小,从长条圆管缩成极微小的立方晶格(Cell,或称放电室),但运作方式维持不变,然后在三个紧邻的晶格内涂佈不同的颜色的萤光质,分别可展现红绿蓝的三原色,如此就形成一个可全彩呈现的基本显示像素(Pixel),之后再将像素进行长宽排列的扩增,组构成1280×720、1920×1080等矩阵组态,如此就成为一套PDP的显示系统。

另外,在PDP中迫使放电的不一定非要用水银蒸汽,也可以使用由氖(Ne)氙(Xe)相混或氦(He)氙(Xe)相混的惰性气体。

更简单说,PDP即是由成千上万的微小霓虹灯所组成,然其显示原理仍旧是倚赖电弧放电,放电必须要有较高的电极电压(如同打雷),这也是PDP较耗电的一大主因。

不过,上述仅是容易理解的譬喻,但更正确、具体的技术细节还包括DC(直流)型放电或AC(交流)型放电,不同的方式使用的电极配置方式也不同,然而由于DC型的电路系统设计过于复杂,今日的销售量产型PDP几乎都採行AC型,使用X、Y、Z三组电极来操控放电,X、Y电极负责扫描驱动,Y、Z电极则负责定址驱动,其中Y电极同时肩负两种工作。

图二 PDP显示原理图(剖面结构的观看角度)

PDP电源管理方案

关于PDP的电源管理,可自两层面来谈:

(1)省电性:面对LCD的挑战,PDP必须让运作用电更精省;

(2)低廉性:以每吋成本而言PDP仍属偏贵,如何让整体系统进一步降价也是现有PDP研发的一大课题,其中精省系统电路成本也相当令人重视。

图三 PDP系统电路的主要功能区块图。

先就省电性来说,PDP的耗电与放电电压息息相关,然而为了达到能放电的能态也必然要使用较高的电压,即约160V~180V以上的电位,而且必须週期性地让电位交替(AC型PDP),即此时X电极为160V,Y电极为0V,彼时变成X电极为0V,Y电极为160V。

为了降低PDP的用电,Fujitsu-Hitachi(富士通日立,富士通也是PDP的发创业者)提出了TERES(TechnologyofReciprocalSustainer)技术,将X、Y电极的电位交替由「0V:160V、160V:0V」改成「+80V:-80V、-80V:+80V」的方式,同时为弥补驱动电压的改变而将交替频率提升一倍。

如此,将电压准位降至过往的一半可使耗电降至过往的1/4,但频率增加一倍则又使耗电增加一倍,如此仍可让整体用电降至过去的1/2。

其次是低廉性,PDP的电路系统成本高于LCD,如今LCD也开始往高吋数领域发展,迫使PDP须比过去更积极降低电路复杂度及成本。而为何PDP的电路系统较贵?原因有以下几点:

(1)放电需要高位能,也因此须使用较能耐高压的功率型MOSFET开关,导致开关元件较贵;

(2)须准备较多种运作电压准位,使电路复杂度提升,进而增加成本;

(3)MOSFET开关在高压下的导通内阻也会增加,为了让驱动效率提升,以及让放电更加安定,因此一个效用开关多半用数个MOSFET进行并联来实现,如此就增加MOSFET的用量,使成本增加;

(4)高压、高流所连带而来的就是高热,因此需要更讲究散热方面的设计,使成本增加;

(5)高压一旦有闪失,其所造成的电路系统伤害也会较大,所以有时也使用光耦合器来作为隔离性开关,使伤害不至于有更大扩散,此安全设计也要增加成本。

图四 富士通日立提出所谓的TERES技术,可让PDP的用电减少一半,电路成本也减半,图为TERES技术示意图。

关于上述种种,其实在TERES技术中也多半获得解决,由于电压从160V降至80V,所以MOSFET的耐压要求可以降低,如此可选用较低廉的MOSFET,电压降低后开关的内阻减少,也就不再需要用并联开关的设计来提升驱动效率、增加放电安定性,减少功率型MOSFET的数目也可降低成本,同时由于TERES已使整体用电减半,使得散热设计的心力、成本也得以放宽。

至于第二项,电压准位类型过多、电路过于复杂,多是指PDP的Y极电路,Y极以分时多工方式饰演两角,此时Y极要与X极一同执行放电驱动,彼时Y极又要与Z极一同执行扫描驱动(显示画面的资料刷新、更新),在放电时Y极需要使用-170V、-70V两种电压,在扫描时Y极则需要0V(接地)、+160V的电压,等于需要四种电压准位。

Y极使用的电压类型过多,运作电路上也过度复杂,使PDP电路成本居高,然TERES技术也对此进行改善,将运用的电压减至三种:+80V、0V、-80V,扫描时使用0V、-80V,放电时使用0V、+80V,再加上扫描顺序的改变,如此可有效简化整体电路,使Y极电路所需的功能模组从五个减至三个,进而降低成本。

图五 Potentia半导体的电源管理晶片:PS-2406

结论与建议

最后,必须瞭解:PDP的整体系统电路,包括显示驱动、显示控制、用电管理、保护电路等,现阶段都是与PDP原制造厂高度相依的,即便有PDP驱动、控制的应用晶片,也多是由原厂自行研制,并搭配原厂自有的设计而用,除原厂外的PDP电路设计多要高度倚赖自行的客制化设计心力,不易找到可倚赖的应用晶片。

不过,PDP整体电路中仍有些部份可直接沿用较具弹性的可组态、可程式化晶片,在电源部份可使用具弹性调设组态的电源管理晶片,以此来因应PDP所需的多种电压准位,如PotentiaSemiconductor的PS-2406晶片(具电源供应、调整、管理、保护等多重效用)即可用于PDP的电源电路设计中。又如Xilinx的CPLD、FPGA亦可运用在PDP的逻辑电路设计中。

除这些外,PDP系统中的驱动电路、扫描电路、放电电路等,都还是要倚赖大比重的客制设计,且需要依据面板规格、特性表现来设计。

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。

| 微信关注 | ||

|

| 技术专题 | 更多>> | |

|

| 2024慕尼黑上海电子展精彩回顾 |

|

| 2024.06技术专题 |