承前:电容设计问题的第一部分,我们从电源不是必须从滤波电容进入芯片管脚开始讲起,带出了电源供电网络(PDN)的阻抗。并从频域角度解释了滤波电容只是整个电源供电网络的一个组成部分。在文章结束之后,网友们提出的问题以及讨论,就带出了滤波电容的位置问题。

本节:从去耦半径出发,通过去耦半径的计算,让大家直观的看到我们常见的电容的“有效范围”问题。

启后:讨论滤波电容的位置与PDN阻抗的关系,提出“全局电容”与“局部电容”的概念。能看到当电容呈现“全局特性”的时候,电容的位置其实没有想象中那么重要。

上一个话题结束的时候,很多网友提出电容的位置问题:“滤波电容有自己的滤波半径,所以重点在于滤波电容正端与芯片电源引脚的距离”。这个互动实在是配合的太好了,高速先生和你握手哈。

传统的说法,电容有其滤波半径,低频电容滤波半径大,所以布局的时候可以放的稍微远一些。并且常规来说,单纯滤波作用的低频电容不要扎堆布局,讲究均匀摆放。而中高频电容的滤波半径较小,需要严格靠近芯片管脚放置,不能离得太远,要不然电容就“不起作用”了。

这个说法,作为我们滤波电容布局的设计指导,没有问题,依旧是正确的指导原则,这个不是我们要讨论的设计误区。不过开场白里面说了,高速先生,就是要追根究底,看看电容的滤波半径到底是怎么回事?

首先,滤波半径还是基于著名的四分之一波长理论。(四分之一波长理论在高速先生的各种文章会反复多次出现,为了方便大家理解,我们会专题讨论各种四分之一波长的问题,这里就不再赘述,如果觉得理解这篇文章有问题,可以单独和高速先生进行讨论)电容去耦半径理论认为,当电容的位置距需要滤波的器件(管脚)的距离刚好是四分之一波长的时候,电容的补偿电流和信号噪声电流相位刚好相差180度,滤波失效。所以为了保证电容的滤波作用,要求电容的位置距需要滤波的器件(管脚)的距离小于1/10的四分之一波长,当然,更严格的要求希望小于1/20的四分之一波长。

大家看到这,估计有点烦躁了,有的人说,这个我早就知道了。也有人说,不是叫“看得懂的高速设计”吗,你说的这些我看不懂。那我们就来看看常见的滤波电容的滤波半径。(这里我们为了计算的简化,假设电容的ESL为0.4NH,电容的安装电感为1.5NH。具体的电容安装电感问题,在上一个专题的第四篇文章里面讨论过了,大家可以参考)看到这里,估计很多PCB设计师会大吃一惊?我们常用的0.1 uf电容,在考虑四十分之一波长的时候,电容的有效去耦半径居然有12英寸。就算严格点考虑两百分之一波长,也有将近2英寸的去耦半径。我们在滤波电容布局的时候,这个去耦半径还是问题吗?

前面的文章讨论过,由于去耦电容只是电源供电网络的一部分,同时高频噪声会更加依赖电源地平板电容及封装内的滤波电容甚至是Die电容来滤除。10Nf或者更小的1Nf电容,在电源滤波系统中的作用会越来越小。在大部分的设计中,0.1 uf电容就是板级系统设计的时候,电源滤波系统中用到的最“高频”的电容了。

借这个机会,再和大家讨论下高速先生讨论PCB设计误区的出发点:很多理论其实没有错,只是我们在使用的时候没有真正知其所以然,所以设计中想当然的“过设计”很多。这类“过设计”有时候并没有坏处,只是当设计出现“恶劣”情况并需要“取舍”的时候,会造成一些困难。

比如电容的去耦半径问题,大家都有这个概念,然后都知道“小”电容(高频电容)的去耦半径很小,需要严格靠近芯片管脚。这个设计原则没有错误,只是当数码消费类产品由于更小的面积,更低的成本以及结构的要求(如厚度),需要我们把电容单面布局,放在和BGA的同一面的时候,很多人困惑了,电容离芯片的电源管脚这么远(有时还要考虑3mm或者5mm的返修间距,就更远了),电容还能起作用吗?

由此引申的另一个问题,和我们的这次的主题相关,先提前预告一下:我们做设计的时候,很喜欢把同种类的数字电源,对不同芯片进行供电的时候,用磁珠隔离一下,希望能避免不同芯片之间同种电源的干扰。电容的作用范围这么大,磁珠隔离了“想象中”的芯片间电源轨道的干扰的同时,会不会也阻碍了电容的作用呢?

本节的结尾,再给大家看一个图片,也是关于电容的去耦半径和作用范围的。之前讨论的谐振频率的四分之一波长,还是有局限性的,首先电容起作用的最高频率不止是谐振频率。其次,作用范围还得考虑你设定的滤波效率。理论是复杂的,任重而道远,多前进一些,真相就更清晰一点。

当然,本节的结论还是继续有效的,我们常用的0.1uf电容,滤波半径远远比我们想象的要大。

本节的问题是:

既然简单的用四分之一波长理论推算的电容去耦半径,对电容布局设计起不到指导作用,那么电容放置的离芯片电源管脚比较远,还会有哪些影响呢?

承前:从去耦半径出发,通过去耦半径的计算,让大家直观的看到我们常见的电容的“有效范围”问题。

本节:讨论滤波电容的位置与PDN阻抗的关系,提出“全局电容”与“局部电容”的概念。能看到当电容呈现“全局特性”的时候,电容的位置其实没有想象中那么重要。

启后:多层板设计的时候,电容倾向于呈现“全局特性”,“电源加磁珠”的设计方法,会影响电容在全局范围内起作用。同时电源种类太多,还会带来其他设计问题。

通过上一篇文章,我们知道平常“耳熟能详”的电容去耦半径理论,对PCB设计其实没有什么指导意义。0.1uf的电容去耦半径足够大,设计中参考这个值没有用处,工程师还是会“尽量”把0.1uf电容靠近芯片的电源管教放置。PCB设计师需要更有效的理论来指导电容的布局设计。

既然简单的用四分之一波长理论推算的电容去耦半径不起作用,那么电容放置得离芯片电源管脚比较远,还会有哪些影响呢?很多人都答对了,影响安装电感。

在上一个专题的第四篇文章里面,已经讨论过电容安装电感的估算。这一次,我们来更详细的看看安装电感。从图3能看到,安装电感可以简单分为L above和 L below。

在这里引入两个概念:Labove 、Lbelow(电容和IC下面的电流回路大小不一定一样,但在这里分析的时候,假定大小等同)

总电感:LTotal= 2Labove+Lbelow

Labove包括电容的ESL和Fan out带来的电感,我们会另外专题讨论电容的Fan out问题。至于L below就更多收到电容位置的影响。简单来说,电容离芯片电源管脚越远,L below围成的面积就越大,相应的安装电感就越大。

更具体点,Lbelow主要是两个过孔的自感和互感,当电容的位置离IC器件更近时,如图4所示,Lbelow的互感增大,因互感的作用与自感的作用相反,导致其整体电感减小,充放电速率更快

可以列出一堆公式来推导这个互感乃至L below,但这个不是高速先生的风格。

其实从图3可以简单看出,G和P之间的距离对L below影响很大,G和P之间的距离越近,L below对应的阴影区域面积就越小。而L below越小,也就意味这电容可以放得越远,换句话说,电容的有效滤波范围更大。电容也就更加倾向于呈现“全局”特性。

下一节我们还会通过一个直观的仿真,让大家看到平面距离与安装电感的关系,以及为什么说在新的设计条件下,电容会呈现全局特性。

图5是一个简单的总结,更具体的分析,请听下回分解。

本次的问题是:

“滥用”磁珠,会带来哪些坏处?什么情况下我们需要使用磁珠对电源进行隔离?什么情况下,“滥用”磁珠会带来负面影响?

承前:讨论滤波电容的位置与PDN阻抗的关系,提出“全局电容”与“局部电容”的概念。能看到当电容呈现“全局特性”的时候,电容的位置其实没有想象中那么重要。

本节:多层板设计的时候,电容倾向于呈现“全局特性”,“电源加磁珠”的设计方法,会影响电容在全局范围内起作用。同时电源种类太多,还会带来其他设计问题。

通过上一篇文章,我们知道电容在不同的使用条件,会呈现“全局特性”与“局部特性”。

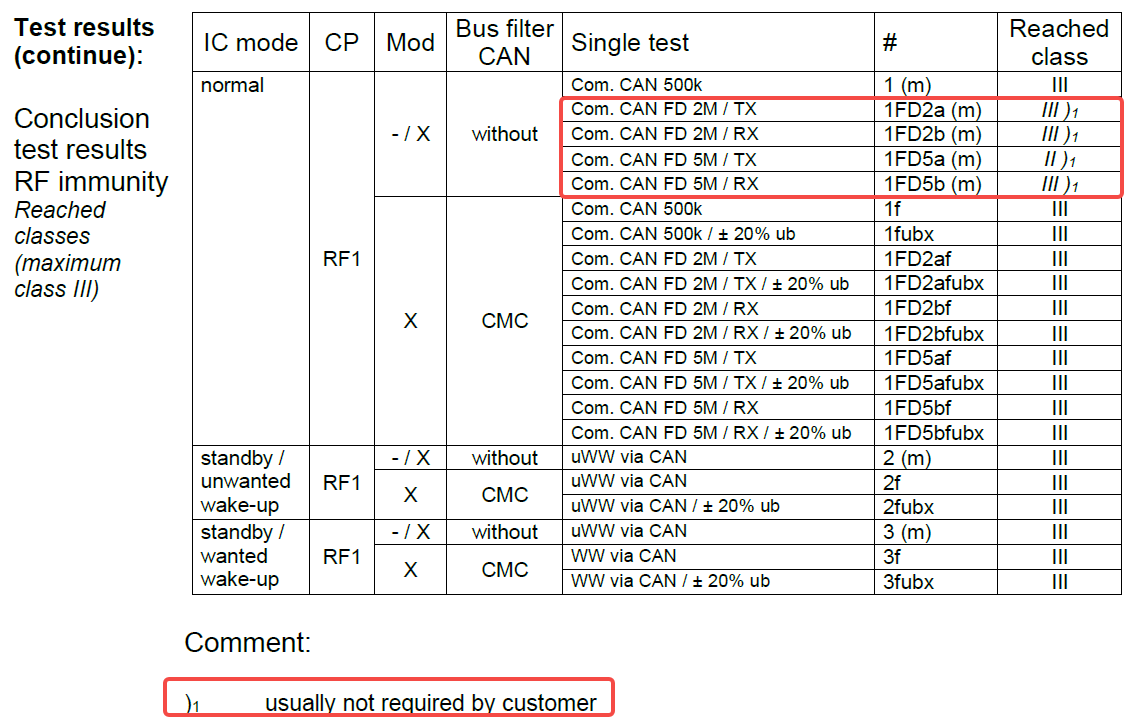

避免研究公式的繁琐,我们来看看实际仿真结果。为了便于研究,设计了一个仿真案例,如图6所示:Case1是电容放在芯片管脚附近,Case1b是电容远离芯片管脚放置。这时候Case1b比Case1多出一对电源地过孔,为了同等条件下只比较电容的位置影响,我们增加Case1a案例,在和Case1b电容Fan out同样的位置上增加一对电源地过孔。

图6的4、5两层为电源地耦合的平面。先来看看电源地距离为3mil时的情况:当电源地紧耦合时,a和b两个Case的PDN曲线基本重合,说明电容的谐振频率没有变化。也就是说,电容位置好像几乎没有任何影响,反而是Case1的谐振频率偏向于低频,说明Case1的安装电感反而更大一些。这个容易理解,主要是多出来的一对电源地过孔导致的。

电源地距离在10mil以内时,以上结论都类似。但是当电源地距离在20mil甚至50mil时,情况稍有变化。如图8所示,电源地距离变大时,a和b两个Case的PDN曲线开始偏离,Case1b的谐振频率向低频偏移,说明电容远离芯片管脚的时候,电容的安装电感明显变大。

所以,我们可以得出简单的结论:

典型的8层以上单板,或者6层板采用3个电源地平面,电源地相对紧耦合的设计,这时候板上的滤波电容呈现“全局特性”,也就是说电容的位置不是很“重要”,电容在全局起作用。双面板四层板,以及6层板电源地距离比较远,相对松耦合的时候,板上的滤波电容倾向于“局部特性”,电容的位置比较重要,最好能靠近芯片管脚放置。

当电源供电网络不使用电源地平面来设计的时候,电容更倾向于“局部特性”。如PLL电源的电容,如DDR3设计中Vref电源的电容,都希望严格把相应的电容靠近芯片的管脚,甚至最好能做到设计时指定电源必须从滤波电容进入芯片管脚。

同样的,对于常规数字电源,如3.3V,2.5V等IO电源,如果我们对每一个芯片都使用磁珠隔离之后单独供电,那么电容就失去了“全局”作用。最直接的一个负面作用就是导致设计需要增加更多的滤波电容。或者某个芯片的电容数量与种类不够,导致电源轨道噪声变大。

就算是电容的数量不是问题,电源噪声可控,“滥用”磁珠还会造成其他设计问题。图9中的方案三是现在非常流行的12层板层叠设计。大家选择这样的层叠最主要的原因就是电源的分割太破碎,这样的电源层如果作为参考平面的话,会比较难避免“跨分割”问题(单面跨电源分割问题,我们会另外有专题讨论)。方案三的层叠避免了电源分割多的问题,却带来更加恶劣的层间串扰等其他问题。

电源种类多是设计的现状,“滥用”磁珠会“雪上加霜”的让电源种类更多。加大电源地平面设计的难度。而增加的磁珠,其实并没有给电源噪声带来好处。

总结:常规的数字电源,在采用多层板设计,电源地平面紧耦合的情况下,不建议“滥用”磁珠,保持电容的“全局”特性起作用。

需要使用磁珠的场合大致分为两种

1、“特别”保护自己,如PLL电源等

2、“关爱”他人,自身的干扰性比较强,避免EMI问题,如强驱动的时钟芯片等

每次一个话题结束的时候,总觉得没什么问题可以问,因为觉得都讲清楚了。不过每次编辑都会强调“你的问题”呢?那就找一个问题,作为下一个话题的铺垫吧:

我们怎么减小上一篇文章中提到的L above?

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。

| 微信关注 | ||

|

| 技术专题 | 更多>> | |

|

| 2024慕尼黑上海电子展精彩回顾 |

|

| 2024.06技术专题 |