在上周的VHDL语言程序科普中,本文为刚刚结束程序设计的新人工程师们介绍了一种利用程序语言设计的单次触发的单稳态电路设计方案,并提供了VHDL源程序方便工程师参考。在今天的文章中,我们将会介绍一种使用VHDL程序所设计的可重触发的单稳态电路,希望通过本文的介绍,对新人工程师的工作和学习提供一定的帮助。

可重触发的单稳态电路是目前应用范围最广泛的电路结构之一,这种电路在民用建筑、照明系统等方面都是非常常见的。在本文所介绍的VHDL程序设计中,我们选择利用TTL单稳态触发器74LS123来完成这种电路的设计。

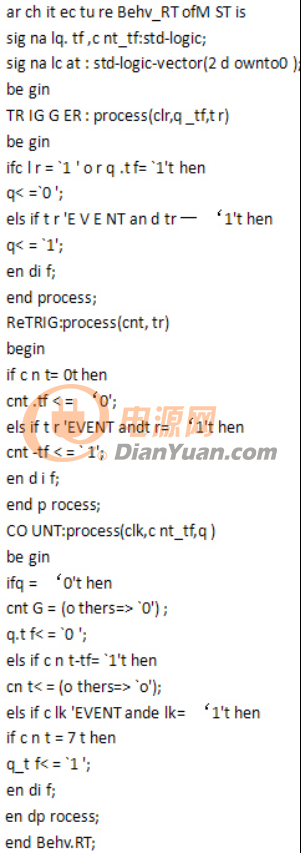

那么,与单次触发的单稳态电路相比,可重触发指的是什么意思?应当如何完成对VHDL程序的编写呢?首先来看可重触发的设计思路,这里指的可重复触发,指的是在单稳态电路被触发后,在回到稳态之前(在这里即输出端q为'1'期间)仍可以继续进行触发,同时在此期间输出端始终保持为'1'不变,直到最后一次触发T时间(即所设定的输出端暂稳态的保持时间)后,才回到稳态,在这里即输出端q为'0'。实现这一功能其实非常简单,只需在单次触发的VHDL程序上增加一个进程,用来处理重触发过程即可。所编写的原程序清单如下:

可以看到,这段程序是在单次触发的单稳态电路源程序基础上增加了一个信号cnt-tf和一个ReTRIG进程。在这段VHDL程序的设计中,信号ent.tf的作用与q_tf类似,用来在进程]触发后仍可以捕捉触发信号ReTRIG和COUNT之间传递状态。ReTRIG进程则使程序在被,并使计数器cnt复位,实现重触发功能。

在了解了这种可重触发的单稳态电路的源程序设计思路后,下面我们来看一下这一电路在实际运行的过程中是如何工作的。在上文中所提供的VHDL源程序中,当这一电路程序被第1次触发后,其输出端4为'1',计数器cnt开始计数,这时若触发信号tr再次来到,则会启动ReTRIG进程,由于计数器已经开始计数,cnt不等于.,因此cnt_tf信号被置'1',同时cnt.tf信号传递到COUNT进程,计数器cnt被清零,并重新开始计数,从而实现重触发功能。

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。

| 微信关注 | ||

|

| 技术专题 | 更多>> | |

|

| 2024慕尼黑上海电子展精彩回顾 |

|

| 2024.06技术专题 |