在电路设计过程中,应用工程师往往会忽视印刷电路板(PCB)的布局。通常遇到的问题是,电路的原理图是正确的,但并不起作用,或仅以低性能运行。在本文中,我将向您介绍如何正确地布设运算放大器的电路板以确保其功能、性能和稳健性。

最近,笔者与一名实习生在利用增益为2V/V、负荷为10kΩ、电源电压为+/-15V的非反相配置OPA191运算放大器进行设计。图1所示为该设计的原理图。

图1:采用非反相配置的OPA191]OPA191原理图

我让实习生为该设计布设电路板,同时为他做了PCB布设方面的一般指导(例如:尽可能缩短电路板的走线路径,尽量将组件保持紧密排布,以减小电路板所占空间),然后让他自行设计。设计过程到底有多难?其实就是几个电阻器和电容器罢了,不是吗?图2所示为他首次尝试设计的布局。红线为电路板顶层的路径,而蓝线为底层的路径。

图2:首次布局尝试方案

看到他的首次布局尝试,我意识到了电路板布局并不像我想象的那样直观;我至少应该为他做一些更详细的指导。他在设计时完全遵从了我的建议:缩短了走线路径,并将各部件紧密地排布在一起。但其实这种布局还有很大的改善空间,以便减小电路板寄生阻抗并优化其性能。

接下来就是对布局的改进。我们所做的首项改进是将电阻R1和R2移至OPA191的倒相引脚(引脚2)旁;这样有助于减小倒相引脚的杂散电容。运算放大器的倒相引脚是一个高阻抗节点,因此灵敏度较高。较长的走线路径可以作为电线,让高频噪声耦合进信号链。倒相引脚上的PCB电容会引发稳定性问题。因此,倒相引脚上的接点应该越小越好。

将R1和R2移至引脚2旁,可以让负荷电阻器R3旋转180度,从而使去耦电容器C1更贴近OPA191的正电源引脚(引脚7)。让去耦电容器尽可能贴近电源引脚,这一点极其重要。如果去耦电容器与电源引脚之间的走线路径较长,会增大电源引脚的电感,从而降低性能。

我们所做的另一项改进在于第二个去耦电容器C2。不应将VCC与C2的导孔连接放在电容器和电源引脚之间,而应布设在供电电压必须通过电容器进入器件电源引脚的位置。图3显示了移动每个部件和导孔从而改善布局的方法。

图3:改进布局的各部件位置

将各部件移至新位置后,仍可以做一些其他改进。您可以加宽走线路径,以减小电感,即相当于走线路径所连接的焊盘尺寸。还可以灌流电路板顶层和底层的接地层,从而为返回电流创造一个坚实的低阻抗路径。图4所示为我们的最终布局。

图4:最终布局

下一次当您布设印刷电路板时,建议您遵循以下布设惯例:

1.尽量缩短倒相引脚的连接。

2.让去耦电容器尽量靠近电源引脚。

3.如果使用了多个去耦电容器,将最小的去耦电容器放在离电源引脚最近的位置。

4.不要将导孔置于去耦电容和电源引脚之间。

5.尽可能扩宽走线路径。

6.不要让走线路径上出现90度的角。

7.灌流至少一个坚实的接地层。

8.不要为了用丝印层来标示部件而舍弃良好的布局。

上文中,我们谈到了布局仪表放大器(运放)PCB的正确方法,并提供了一系列可供参考的良好布局实践。接下来,将探讨布局仪表放大器(instrumentation amplifier,INA)时常见的错误,然后展示INA PCB如何正确布局。

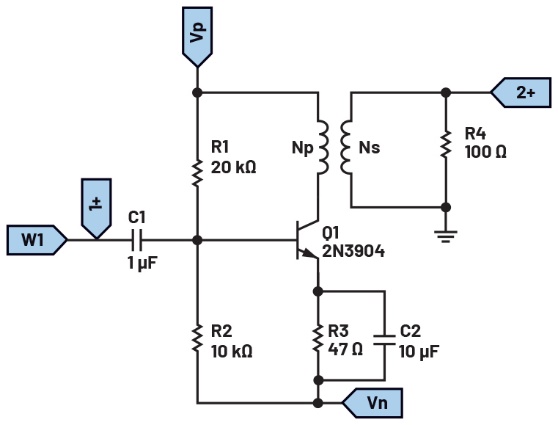

INA 用于要求放大差分电压的应用,如测量通过高侧电流感应应用中分流电阻的电压。图5所示为典型单电源高侧电流感应电路的原理图。

图5:高侧电流感应原理图

图5测量的是通过RSHUNT的差分电压,R1、R2、C1、C2和C3用于提供共模和差模滤波,R3和C4提供U1 INA的输出滤波,U2用于缓冲INA的参考引脚。R4和C5用于形成低通滤波器,将运放给INA参考引脚带来的噪音降至最低。

虽然图5中的原理图布局看起来很直观,但却非常容易在PCB布局中出错,造成电路性能下降。图6显示了工作人员在检查INA布局时常见的三种错误。

图6:INA常见PCB布局

从上图可见,第一个错误是对通过电阻器差分电压Rshunt的测量方式。可以看到Rshunt到R2的线路较短,因此其电阻要小于Rshunt到R1线路的电阻。这一线路阻抗上的差异可能会引入INA的输入偏置电流在U1输入侧造成差分电压。由于INA的任务是放大差分电压,因此,如果输入侧的线路不平衡可能会导致出现错误。因此,需确保INA输入线路的平衡并尽可能短。

第二个错误则是关于INA增益设置电阻Rgain的。U1引脚到Rgain焊垫的线路长于实际所需长度,因此会造成额外的电阻和电容。由于增益取决于INA增益设置引脚、引脚1和引脚8之间的电阻,额外的电阻可能带来错误的目标增益。而由于INA的增益设置引脚连接着INA内的反馈节,额外的电容可能造成稳定性问题。因此,需确保连接增益设置电阻的线路应尽可能短。

最后,可能需要改进缓冲电路参考引脚的位置。参考引脚缓冲电路位于距离参考引脚较远的位置,这可能增加连接参考引脚的电阻,导致噪声或其他信号可能耦合到线路中。参考引脚上额外的电阻可能会降低大多数INA提供的高共模抑制比(CMRR)。因此,需将参考引脚缓冲电路安排在尽可能靠近INA参考引脚的位置。

图7所示为纠正这三类错误后的布局。

图7:纠正三类错误后的PCB布局

在图7中,可以看到R1和R2到分流电阻的线路长度相同,并采用了一个开尔文连接。增益设置电阻到INA引脚的线路做到了尽可能短,基准缓冲电路也尽可能靠近参考引脚。

如果您今后要为INA布局PCB,请确保遵循以下原则:

1.确保输入侧所有线路完全平衡;

2.减少线路长度并最大程度降低增益设置引脚上的电容;

3.将基准缓冲电路安排在尽可能靠近INA参考引脚的位置;

4.将解耦电容安排在尽可能靠近电源引脚的位置;

5.至少覆设一个实心接地层;

6.不要为了给元件使用丝印而牺牲良好的布局;

7.遵循本文第一部分中提到的指南。

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。

| 微信关注 | ||

|

| 技术专题 | 更多>> | |

|

| 2024慕尼黑上海电子展精彩回顾 |

|

| 2024.06技术专题 |