对于开关电源来说,驱动电路作为控制电路和功率电路的接口,其作用至关重要,本文就将详细探讨开关电源的驱动电路的参数设计以及驱动芯片的选型。

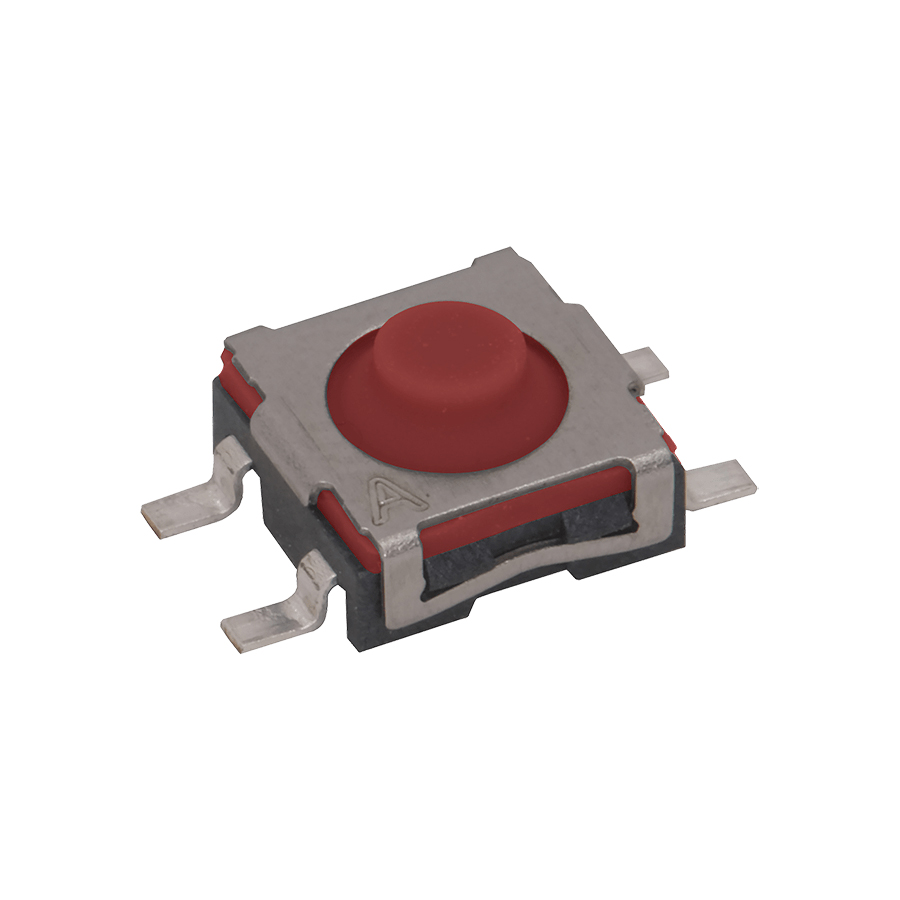

常用的mos管驱动电路结构如图1所示,驱动信号经过图腾柱放大后,经过一个驱动电阻Rg给mos管驱动。其中Lk是驱动回路的感抗,一般包含mos管引脚的感抗,PCB走线的感抗等。在现在很多的应用中,用于放大驱动信号的图腾柱本身也是封装在专门的驱动芯片中。本文要回答的问题就是对于一个确定的功率管,如何合理地设计其对应的驱动电路(如驱动电阻阻值的计算,驱动芯片的选型等等)。

注1:图中的Rpd为mos管栅源极的下拉电阻,其作用是为了给mos管栅极积累的电荷提供泄放回路,一般取值在10k~几十k这一数量级。由于该电阻阻值较大,对于mos管的开关瞬态工作情况基本没有影响,因此在后文分析mos的开关瞬态时,均忽略Rpd的影响。

注2:Cgd,Cgs,Cds为mos管的三个寄生电容,在考虑mos管开关瞬态时,这三个电容的影响至关重要。

图1 常用的mos管驱动电路

1、驱动电阻的计算

1.1、驱动电阻的下限值

驱动电阻下限值的计算原则为:驱动电阻必须在驱动回路中提供足够的阻尼,来阻尼mos开通瞬间驱动电流的震荡。

当mos开通瞬间,Vcc通过驱动电阻给Cgs充电,如图2所示(忽略Rpd的影响)。根据图2,可以写出回路在s域内对应的方程:

根据式(1),可以求解出ig,并将其化为典型二阶系统的形式:

根据式(2),可以求解出该二阶系统的阻尼比为:

为了保证驱动电流ig不发生震荡,该系统的阻尼比必须大于1,则根据(3)可以求解得到:

式(4)给出了驱动电阻Rg的下限值,式(4)中Cgs为mos管gs的寄生电容,其值可以在mos管对应的datasheet中查到。而Lk是驱动回路的感抗,一般包含mos管引脚的感抗,PCB走线的感抗,驱动芯片引脚的感抗等,其精确的数值往往难以确定,但数量级一般在几十nH左右。因此在实际设计时,一般先根据式(4)计算出Rg下限值的一个大概范围,然后再通过实际实验,以驱动电流不发生震荡作为临界条件,得出Rg下限值。

图2 mos开通时的驱动电流

1.2、驱动电阻的上限值

驱动电阻上限值的计算原则为:防止mos管关断时产生很大的dV/dt使得mos管再次误开通。

当mos管关断时,其DS之间的电压从0上升到Vds(off),因此有很大的dV/dt,根据公式:i=CdV/dt,该dV/dt会在Cgd上产生较大的电流igd,如图3所示。

图3 mos关断时的对应电流

该电流igd会流过驱动电阻Rg,在mos管GS之间又引入一个电压,当该电压高于mos管的门槛电压Vth时,mos管会误开通,为了防止mos管误开通,应当满足:

由上式解得:

式(6)给出了驱动电阻Rg的上限值,式(6)中Cgd为mos管gd的寄生电容,Vth为mos管的门槛电压,均可以在对应的datasheet中查到,dV/dt则可以根据电路实际工作时mos的DS电压和mos管关断时DS电压上升时间(该时间一般在datasheet中也能查到)求得。

从上面的分析可以看到,在mos管关断时,为了防止误开通,应当尽量减小关断时驱动回路的阻抗。基于这一思想,下面再给出两种很常用的改进型电路,可以有效地避免关断时mos的误开通问题。

图4 改进电路1

图4给出的改进电路1是在驱动电阻上反并联了一个二极管,当mos关断时,关断电流就会流经二极管Doff,这样mos管gs的电压就为二极管的导通压降,一般为0.7V,远小于mos的门槛电压(一般为2.5V以上),有效地避免了mos的误开通。

图5 改进电路2

图5给出的改进电路2是在驱动电路上加入了一个开通二极管Don和关断三级管Qoff。当mos关断时,Qoff打开,关断电流就会流经该三极管Qoff,这样mos管gs的电压就被钳位至地电平附近,从而有效地避免了mos的误开通。

1.3、驱动电阻阻值的选择

根据1.1节和1.2节的分析,就可以求得mos管驱动电阻的上限值和下限值,一般来说,mos管驱动电阻的取值范围在5~100欧姆之间,那么在这个范围内如何进一步优化阻值的选取呢?这就要从损耗方面来考虑,当驱动电阻阻值越大时,mos管开通关断时间越长(如图6所示),在开关时刻电压电流交叠时间久越大,造成的开关损耗就越大(如图7所示)。所以在保证驱动电阻能提供足够的阻尼,防止驱动电流震荡的前提下,驱动电阻应该越小越好。

图6 mos开关时间随驱动电阻的变化

图7 mos开关损耗随驱动电阻的变化

比如通过式(4)和式(6)的计算得到驱动电阻的下限为5欧姆,上限为100欧姆。那么考虑一定的裕量,取驱动电阻为10欧姆时合适的,而将驱动电阻取得太大(比如50欧姆以上),从损耗的角度来讲,肯定是不合适的。

2、驱动芯片的选型

对于驱动芯片来说,选型主要考虑如下技术参数:驱动电流,功耗,传输延迟时间等,对隔离型驱动还要考虑原副边隔离电压,瞬态共模抑制等等(common mode transient immunity),下面就分别加以介绍。

2.1 最大电流

在mos管开通的时候,根据图2,可以得到mos开通瞬间的驱动电流ig为(忽略Lk的影响)

其中ΔVgs为驱动电压的摆幅,那么在选择驱动芯片的时候,最重要的一点就是驱动芯片能提供的最大电流要超过式(7)所得出的电流,即驱动芯片要有足够的“驱动能力”。

2.2 功耗

驱动功率计算表达式如下:

其中Qg为栅极充电电荷,可以在datasheet中查到,ΔVgs为驱动电压的摆幅,fs为mos的开关频率,在实际选择驱动芯片时,应选择驱动芯片所能提供的功率大于式(8)所计算出来的功率。同时还要考虑环境温度的影响,因为大多数驱动芯片所能提供的功率都是随着环温的升高而降额的,如图8所示。

图8 驱动允许的损耗功率随着环温升高而降额

2.3 传输延迟(Propagation Delay)

所谓传输延迟,即驱动芯片的输出上升沿和下降沿都要比起输入信号延迟一段时间,其对应的波形如图9所示。对于传输延迟来说,我们一般希望有两点:

1)传输延时的实际要尽量短。

2)“开通”传输延时和“关断”传输延时的一致性要尽量好。

图9 驱动芯片输入输出传输延时

下面就针对第二点来说一说,如果开通和关断传输延时不一致会有什么影响呢?我们以常用的IGBT驱动,光耦M57962为例,给出其传输延时的数据,如图10所示。

图10 M57962的传输延时数据

从图10可以看到,M57962的的开通传输延时一般为1us,最大为1.5us;关断传输延时一般为1us,最大为1.5us。其开通关断延时的一致性很差,这样就会对死区时间造成很大的影响。假设输入M57962的驱动死区设置为1.5us。那么实际到IGBT的GE级的驱动死区时间最大为2us(下管开通延时1.5us, 上管关断延时1us),最小仅为1us(下管开通延时1us, 上管关断延时1.5us)。造成实际到达IGBT的GE级的死区时间的不一致。因此在设计死区时间时,应当充分考虑到驱动芯片本身的传输延时的不一致性,避免因此造成的死区时间过小而导致的桥臂直通。

2.4 原副边绝缘电压

对于隔离型驱动来说(光耦隔离,磁耦隔离)。需要考虑原副边的绝缘电压,一般项目中都会给出绝缘电压的相关要求。若没有相关要求,一般可取绝缘电压为mos电压定额的两倍以上。

2.5共模瞬态抑制等等(common mode transient immunity)

对于桥式电路来说,同一桥臂上管的源极(也就是下管的漏极)是高频跳变的,该高频跳变的dV/dt会通过隔离驱动原副边的寄生电容产生较大的共模电流耦合到原边,从而对控制驱动产生影响,如图11所示。所以说,驱动芯片的共模瞬态抑制(common mode

transient immunity)也很重要,在实际选择驱动芯片时,驱动芯片的CM transient immunity应该大于电路中实际的dV/dt,越大越好。

图11 共模瞬态抑制

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。

| 微信关注 | ||

|

| 技术专题 | 更多>> | |

|

| 2024慕尼黑上海电子展精彩回顾 |

|

| 2024.06技术专题 |