相信不少初入茅庐的工程师们在学习的旅途中走了不少弯路,下面我们就针对信号完整性相关知识术语进行普及。

1.信号完整性(Signal Integrity)

信号完整性是指信号在信号线上的质量。信号具有良好的信号完整性是指当在需要的时候具有所必须达到的电压电平数值。

2.传输线(Transmission Line)

传输线是一个网络(导线),并且它的电流返回到地或电源。

3.特性阻抗(Characteristic Impedance)

组成信号传输回路的两个导体之间存在分布电感和分布电容,当信号沿该导体传输时,信号的跃变电压(V)和跃变电流(I)的比值称为特性阻抗(Z0),即 Z0=V/I。

4.反射(Reflection)

反射就是在传输线上的回波。信号功率(电压和电流)的一部分传输到线上并达到负载处,但是有一部分被反射了。如果源端与负载端具有相同的阻抗,反射就不会发生。

5.串扰(Crosstalk)

串扰是两条信号线之间的耦合。信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。

6.过冲(Overshoot)

过冲就是第一个峰值或谷值超过设定电压。对于上升沿是指最高电压,而对于下降沿是指最低电压。过分的过冲能够引起保护二极管工作,导致过早地失效。

7.下冲(Undershoot)

下冲是指下一个谷值或峰值。过分的下冲能够引起假的时钟或数据错误(误操作)。

8.电路延迟

指信号在器件内传输所需的时间(Tpd) 。例如,TTL的电路延迟在3 ~ 20nS 范围。

9.边沿时间

器件输出状态从逻辑低电平跃变到高电平所需要的时间(信号波形的 10~90%),通常表示为上升沿(Tr)。器件输出状态从逻辑高电平下降到低电平所需要的时间(信号波形的 90~10%),通常表示为下降沿(Tf)。

10.占空比偏斜

信号传输过程中,从低电平到高电平的转换时间与从高电平到低电平的转换时间之间的差别,称为占空比偏斜。TTL和CMOS信号的占空比偏斜问题较为突出,主要是因为其输出的上升沿和下降沿延迟不同。

11.输出到输出偏斜

同一器件不同输出引脚之间的信号延迟差别,称为输出到输出偏斜。

12.器件到器件偏斜

由于制造工艺和使用环境的变化,造成的不同器件对应引脚之间的信号延迟差别,称为器件到器件偏斜。通常,器件之间的偏差远大于其他类型的偏斜。

13.动态偏斜

主要是指由于温度变化、地或电源噪声造成阀值电平随时间漂移,从而产生信号延迟的变化。

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。

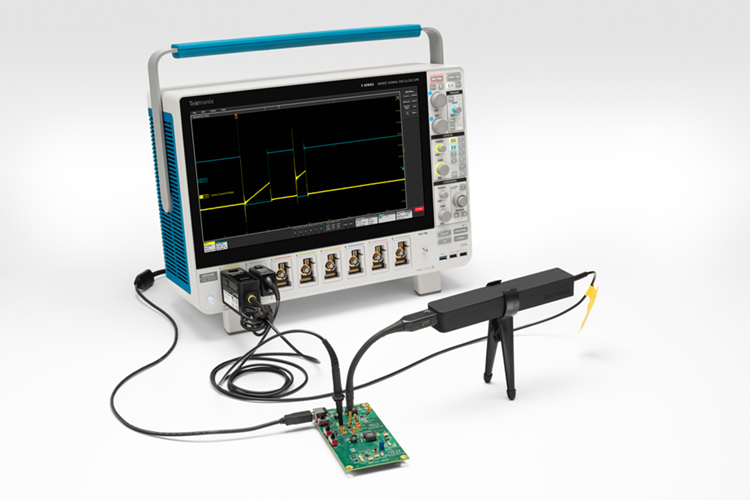

| 【测试案例分享】 提高信号完整性的秘密武器:实时示波器测试TDR阻抗的全新方案 | 24-09-29 15:46 |

|---|---|

| 贸泽、Analog Devices和Samtec推出全新电子书 汇集各路专家关于信号完整性的真知灼见 | 24-09-02 16:46 |

| 一场精度的“交响乐”:以低噪声技术协调电源和信号完整性 | 23-07-13 16:51 |

| 如何通过低噪声和低纹波设计技术来增强电源和信号完整性 | 23-07-05 16:17 |

| 一文带你了解传输线理论 | 23-01-04 10:21 |

| 微信关注 | ||

|

| 技术专题 | 更多>> | |

|

| 2024慕尼黑上海电子展精彩回顾 |

|

| 2024.06技术专题 |