本文通过图文结合的方式,和大家一起分享究竟是何缘故,要在贴片晶振邻近平面层挖空,希望读完本文的各位能清楚的理解这个用意是什么?

一些多层高速板上的贴片晶振有时在设计时会挖空相邻的平面层,如下所示:

这是一块四层板,底层有一个贴片晶振,

第三层的地平面在设计时用禁止区域将晶振正下面的地平面挖空,

第二层晶振下面的平面没有挖空,

顶层也没有挖空。

很多人不解,在贴片晶振邻近平面层挖空的用意是什么呢?

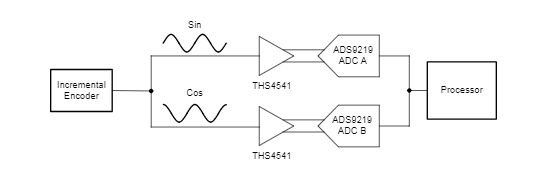

因为贴片晶振两个焊盘是长方形的焊盘,刚好和邻近的平面形成了一个电容器,由电容计算公式C=εs/4πkd可知,长方形的焊盘与邻近的地平面之间寄生的电容量和焊盘的面积S,焊盘到平面的距离d有关。一般情况焊盘的面积S都不会变了,所以晶振长方形的焊盘与邻近的地平面之间寄生的电容量主要由焊盘到平面的距离d决定。d一般都很小,比如1.6MM的四板,层压结构如下图所示,

由图可知,芯板占了主要的厚度,焊盘到平面的距离d只有3.5mil,非常的小,如果用电容计算公式C=εs/4πkd算出来的寄生电容值是很大的。

有个例子是这样的,原厂有个参考原理图,晶振的谐振电容是12pF,但是PCB样板做回来后,测试发现样板的频偏很大。

后来把晶振的两个谐振电容改成4.7pF后,频偏才有所改善。

由此可见,贴片晶振的两个焊盘脚与其下方的平面存在着寄生电容。寄生电容会影响系统的频偏,频偏过大时,系统在平常工作环境可以正常运行,但是在极限条件下,如高低温条件,很有可能不能正常运行了。如果贴片晶振的两个焊盘脚与其下方的平面存在着寄生电容很大,谐振电容不贴时,晶振的频偏也是很大。那么这个PCB板用来生产,出来的产品虽然平常工作时没有什么问题,但是在一些高低温的条件下,就可能会出问题了,这是一个很大的风险。所以在设计PCB时,遇到贴片晶振时,应该考虑挖空晶振下方的平面层。

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。

| 微信关注 | ||

|

| 技术专题 | 更多>> | |

|

| 2024慕尼黑上海电子展精彩回顾 |

|

| 2024.06技术专题 |