Question:

问题:

What is the right frequency generation component for my application?

何种频率产生器件适合我的应用?

Answer:

答案:

Understanding the performance characteristics of frequency generation components is critical to determining the right solution for the target use case. This is a quick guide meant to help RF system engineers through the selection process.

了解频率产生器件的性能特征对于为目标使用场景确定正确的解决方案至关重要。这是一个快速指南,旨在帮助RF系统工程师熟悉整个选择流程。

Key Performance Criteria

主要性能判据

Let us first define the criteria that are typically used to characterize the performance of frequency generation components. The most basic one we would normally start our selection process with is the output frequency range. There is a broad variety of components designed to generate frequencies across the entire spectrum, supporting ranges limited to a single tone or spanning multiple octaves. However, when selecting a component based on its output frequencies, it is important to consider that wideband and high frequency capabilities are often traded off for other fundamental characteristics, which include frequency stability, output spectral purity, and switching speed.

我们首先定义表征频率产生器件性能通常使用的判据。选择流程一般从最基本的判据开始,那就是输出频率范围。为了生成整个频谱范围内的频率,人们设计了各种各样的器件,支持从单音到跨越多个倍频程的频率。然而,当根据输出频率选择器件时,必须注意到,宽带和高频能力常被用来交换其他基本特性,包括频率稳定性、输出频谱纯度和开关速度。

Frequency stability represents short-term and long-term variations in the output signal. Short-term stability is associated with variations that are much smaller than one complete period of the signal. These variations are expressed in terms of phase jitter and phase noise. Phase jitter defines small fluctuations in the phase of a signal in the time domain, and the phase noise is its spectral representation described by the relative noise power level contained in a 1 Hz bandwidth at various offsets from the carrier frequency. If the frequency variations occur over a longer period of time, we usually talk about long-term stability, which describes the drift of the output frequency (typically expressed in parts per million or ppm) due to various aspects including temperature, load conditions, and aging.

频率稳定性代表输出信号的短期和长期变化。短期稳定性与远小于一个完整信号周期的变化有关。这些变化以相位抖动和相位噪声表示。相位抖动定义时域中信号相位的微小波动,相位噪声是其频谱表示,由相对于载波频率的不同偏移频率下1 Hz带宽中包含的相对噪声功率水平来描述。如果频率变化发生在较长时间段内,我们通常会使用长期稳定性来描述,它是指由于温度、负载条件、老化等各方面导致的输出频率漂移(通常用ppm表示)。

Spectral purity is another important characteristic to be considered in the component’s selection process. It is described by the spurious content present in the output spectrum of a device, which is usually quantified by the level of harmonics and feedthrough components expressed relative to the level of the fundamental frequency.

频谱纯度是器件选择流程中要考虑的另一个重要特性。它由器件输出频谱中存在的杂散成分来描述,通常用相对于基频水平表示的谐波水平和馈通分量来量化。

In addition to the stability and spectral purity of the output signal, the switching speed (also known as settling time or lock time) is yet another typical trade-off parameter that needs to be considered when choosing the optimum frequency generation solution. It describes how much time it takes for the component to switch from one frequency to another frequency, and this requirement can largely vary depending on the final application.

除了输出信号的稳定性和频谱纯度之外,开关速度(也称为建立时间或锁定时间)是又一个典型的权衡参数,选择最优频率产生器方案时需要予以考虑。它描述器件从一个频率切换到另一个频率所需的时间,此要求可能会因最终应用而有很大差异。

The Main Types of Components

器件的主要类型

Now that we have defined the key performance criteria used to characterize frequency generation components, let us give a short overview of their main types, which are designed to offer different sets of characteristics associated with these criteria. This overview should ultimately serve as a guide to choosing the right type of device, which should meet the needs of the target application.

上面定义了用于表征频率产生器件的主要性能判据,现在我们简要说明其主要类型,这些类型旨在提供与这些判据相关的不同特性组合。此概述最终应作为选择正确类型器件以满足目标应用需求的指南。

A crystal (XTAL) oscillator (XO) is a component that uses a piezoelectric resonator (typically quartz) to generate fixed output frequency from a few kilohertz up to several hundred megahertz. A special type of XO called a voltage controlled crystal oscillator (VCXO) allows the frequency to be altered, but only by a very small amount to enable fine adjustments. XOs are electromechanical transducers with extremely high Q factors that can exceed 100,000, resulting in a very stable output frequency characterized by a very low phase noise. XOs are limited in their maximum output frequency and tuning capabilities; however, they are the perfect choice when a single precise reference needs to be provided to other types of components to derive much higher frequencies.

晶体(XTAL)振荡器(XO)使用压电谐振器(通常为石英)产生几千赫兹至几百兆赫兹的固定输出频率。有一种特殊类型的XO,称为压控晶体振荡器(VCXO),它允许改变频率,但只能改变很小的量以支持微调。XO是具有极高Q因子(可超过 100,000)的机电换能器,可产生非常稳定且相位噪声非常低的输出频率。XO的最大输出频率和调谐能力有限,但是,当需要为其他类型的器件提供单一精确参考以获得更高频率时,它是出色的选择。

A voltage controlled oscillator (VCO) is a different type of a frequency generation component that relies on LC resonant circuits. Electrical circuit elements result in significantly lower Q factors compared to crystals (typically by a factor of 1000 less); however, they enable much higher output frequencies and wide tuning ranges. VCOs produce an output signal whose frequency is controlled by an external input voltage. A VCO’s core can use different resonant circuits. Single-core VCOs using high Q resonators offer a low phase noise performance over a limited frequency range, whereas the oscillators designed for a lower Q factor target a wideband operation with mediocre noise characteristics. Multiband VCOs using several switched high Q resonator circuits offer a compromise solution that provides wideband operation and low phase noise performance that is achieved at the expense of a slower tuning speed limited by the time required to switch between different cores. VCOs are a great all-around solution, but they generally do not provide a stable output signal, which is why VCOs are often used in conjunction with phase-locked loops (PLLs) to improve output frequency stability.1

压控振荡器(VCO)是一种不同类型的频率产生器件,依赖于LC谐振电路。与晶体相比,电气电路元件的Q因子要低得多(通常低1000倍),但它可以实现高得多的输出频率和宽调谐范围。VCO产生的输出信号频率由外部输入电压控制。VCO的内核可以使用不同的谐振电路。使用高Q谐振器的单核VCO可在有限频率范围内提供低相位噪声性能,而较低Q因子的振荡器以宽带操作为目标,噪声特性很一般。使用多个切换式高Q谐振器电路的多频段VCO是一种折衷解决方案,既支持宽带操作,又能提供低相位噪声性能,但其代价是调谐速度较慢,因为切换不同的核需要时间。VCO是一种出色的全方位解决方案,但它一般不能提供稳定的输出信号,这就是为什么VCO经常与锁相环(PLL)配合使用以提高输出频率稳定性的原因1。

A phase-locked loop (PLL) or PLL synthesizer is a circuit that ensures the stability of a VCO output frequency required in many frequency synthesis and clock recovery applications. As depicted in Figure 1a, a PLL incorporates a phase detector that compares a divide-by-N version of the VCO frequency to the reference frequency and uses this difference output signal to adjust the DC control voltage applied to the tuning line of the VCO. This allows for instantaneous correction of any frequency drift and, thus, maintenance of the stable operation of the oscillator. A typical PLL IC includes an error detector (a phase frequency detector, or PFD, with a charge pump) and a feedback divider (see the dashed line area in Figure 1a), and it still requires an additional external loop filter, a precise reference frequency, and a VCO to form a complete feedback system for stable frequency generation. The realization of this system can be significantly simplified by using synthesizer ICs featuring an integrated VCO.1,2

锁相环(PLL)或PLL频率合成器可确保许多频率合成和时钟恢复应用所需的VCO输出频率稳定。如图1a所示,PLL包含鉴相器,其将VCO频率的N分频与参考频率进行比较,并使用该差值输出信号调节施加于VCO调谐线路的DC控制电压。这使得任何频率漂移都能得到即时校正,因而振荡器能够保持稳定工作。典型的PLL IC包含误差检测器(带电荷泵的鉴频鉴相器或PFD)和反馈分频器(参见图1a中的虚线区域),另外还需要外部环路滤波器、精密参考频率和VCO以构成一个完整的反馈系统,从而产生稳定的频率。使用集成VCO的频率合成器IC可以大大简化该系统的实现1,2。

Synthesizers with integrated VCO combine a PLL and a VCO in a single package and require only an external reference and a loop filter to realize the desired function. An integrated PLL synthesizer is a versatile solution with a broad spectrum of digital control settings for accurate frequency generation. It may often include integrated power splitters, frequency multipliers, frequency dividers, and tracking filters to permit up to several octaves of frequency coverage beyond the fundamental range of the integrated VCO. The intrinsic parameters of all these components determine the output frequency range, phase noise, jitter, lock time, and other characteristics representing the overall performance of the synthesizer circuit.1

集成VCO的频率合成器将PLL和VCO组合在单个封装中,只需要外部参考和环路滤波器就能实现所需的功能。集成式PLL频率合成器是一种多功能解决方案,具有广泛的数字控制设置,支持产生精确频率。它常常包含集成功分器、倍频器、分频器和跟踪滤波器,频率覆盖范围超越了VCO的基频范围,达到数个倍频程。所有这些元件的内在参数决定了输出频率范围、相位噪声、抖动、锁定时间和其他表示频率合成电路总体性能的特性1。

A translation loop is another type of synthesizer solution based on the PLL concept but implemented using a different approach. As shown in Figure 1b, it uses an integrated downconversion mixing stage instead of an N-divider in the feedback loop to set the loop gain to 1 and minimize the in-band phase noise. Translation loop ICs (see the dashed line area in Figure 1b) are designed for highly jitter sensitive applications and, in combination with an external PFD and an LO, enable a complete frequency synthesis solution offering instrument-grade performance in a compact form factor.1

转换环路是基于PLL概念的另一类频率合成器,但采用不同的方法实现。如图1b所示,其反馈环路中使用的是集成下变频混频级,而不是N分频器,环路增益设置为1,带内相位噪声极小。转换环路IC(参见图1b中的虚线区域)专为对抖动高度敏感的应用而设计,并与外部PFD和LO组合使用,以紧凑的尺寸实现完整的频率合成解决方案,提供仪表级性能1。

A direct digital synthesizer (DDS) is an alternative to integrated PLL synthesizers realized using a different concept. The basic DDS architecture is schematically depicted in Figure 1c. It is a digitally controlled system that includes a highly accurate reference frequency representing a clock signal, a numerically controlled oscillator (NCO) creating a digital version of the target waveform, and a digital-to-analog converter (DAC) delivering the final analog output. DDS ICs offer rapid switching speeds, fine tuning resolution of the frequency and phase, and low output distortion, which make them an ideal solution for the applications where superior noise performance and high frequency agility are of primary importance.1,3

直接数字频率合成器(DDS)是集成PLL频率合成器的替代方案,采用不同的原理实现。基本DDS架构的原理图如图1c所示。它是一种数字控制系统,包括表示时钟信号的高精度参考频率、创建目标波形数字版本的数字控制振荡器(NCO)以及提供最终模拟输出的数模转换器(DAC)。DDS IC提供非常快的开关速度、精细的频率和相位分辨率以及低输出失真,因此特别适合于出色噪声性能和高频率捷变性至关重要的应用1,3。

Conclusion

结论

Frequency generation components are used in a broad range of applications fulfilling various functions including frequency conversion, waveform synthesis, signal modulation, and clock signal generation. This article presented a brief overview of the main types of these components designed to address different sets of requirements imposed by final applications. For example, communication systems require low in-band noise to maintain low error vector magnitude (EVM), spectrum analyzers rely on local oscillators with fast lock time to realize rapid frequency sweep, and high speed converters need a low jitter clock to ensure high SNR performance.

频率产生器件应用广泛,可实现各种功能,包括变频、波形合成、信号调制和时钟信号产生。针对最终应用施加的不同要求,需要设计不同类型的频率产生器件,本文简要说明了这些器件的主要类型。例如,通信系统需要低带内噪声以维持低误差矢量幅度(EVM),频谱分析仪依赖于具有快速锁定时间的本振来实现快速频率扫描,高速转换器需要低抖动时钟以确保高SNR性能。

Figure 1. Simplified block diagrams of the (a) PLL, (b) translation loop, and (c) DDS.

图1.(a) PLL、(b) 转换环路、(c) DDS的简化框图

Analog Devices provides the broadest portfolio of RF integrated circuits in the industry fitting nearly all of the functional blocks in a signal chain. ADI products deliver best-in-class performance and address the most demanding requirements across a wide variety of RF applications ranging from communication and industrial systems, all the way up to test and measurement equipment and aerospace systems.

ADI公司提供非常丰富的RF集成电路产品组合,支持信号链中的几乎所有功能模块。ADI产品提供一流的性能,可满足广泛RF应用——从通信和工业系统一直到测试测量设备和航空航天系统——的最苛刻要求。

References

参考资料

1 Anton Patyuchenko. “RF Signal Chain Discourse—Part 2: Essential Building Blocks.” Analog Dialogue, Vol. 55, No. 3, July 2021.

Anton Patyuchenko。“解密RF信号链—第2部分:基本构建模块”。《模拟对话》,第55卷第3期,2021年7月。

2 Ian Collins and David Mailloux. “Revolution and Evolution in Frequency Synthesis: How PLL/VCO Technology Has Increased Performance, Decreased Size, and Simplified Design Cycle.” Analog Devices, Inc., January 2020.

Ian Collins和David Mailloux。“频率合成技术的变革和发展:PLL/VCO技术如何提升性能、减小尺寸并简化设计周期”。ADI公司,2020年1月。

3 Jim Surber and Leo McHugh. “Single-Chip Direct Digital Synthesis vs. the Analog PLL.” Analog Dialogue, Vol. 30, No. 3, July 1996.

Jim Surber和Leo McHugh。“单芯片直接数字频率合成与模拟PLL”。《模拟对话》,第30卷第3期,1996年7月。

About the Author

作者简介

Anton Patyuchenko received his Master of Science in microwave engineering from the Technical University of Munich in 2007. Following his graduation, Anton worked as a scientist at German Aerospace Center (DLR). He joined Analog Devices as a field applications engineer in 2015 and is currently providing field applications support to strategic and key customers of Analog Devices specializing in RF applications. He can be reached at anton.patyuchenko@analog.com.

Anton Patyuchenko于2007年获得慕尼黑技术大学微波工程硕士学位。毕业之后,Anton曾在德国航空航天中心(DLR)担任科学家。他于2015年加入ADI公司担任现场应用工程师,目前为ADI公司战略与重点客户提供现场应用支持,主要负责RF应用。联系方式:anton.patyuchenko@analog.com。

声明:本内容为作者独立观点,不代表电源网。本网站原创内容,如需转载,请注明出处;本网站转载的内容(文章、图片、视频)等资料版权归原作者所有。如我们采用了您不宜公开的文章或图片,未能及时和您确认,避免给双方造成不必要的经济损失,请电邮联系我们,以便迅速采取适当处理措施;欢迎投稿,邮箱∶editor@netbroad.com。

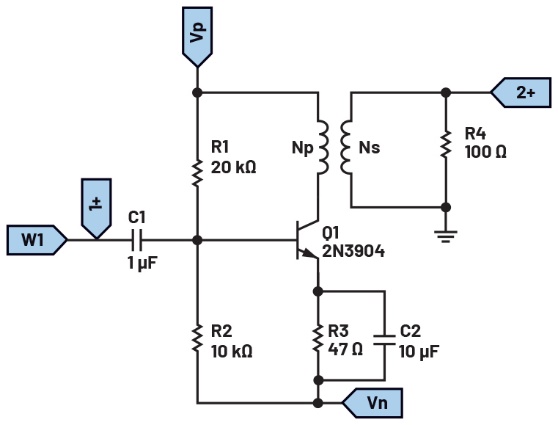

| ADALM2000实验:变压器耦合放大器 | 24-11-18 15:23 |

|---|---|

| 利用IMU增强机器人定位:实现精确导航的基础技术 | 24-11-14 16:29 |

| 48 V技术的魅力:系统级应用中的重要性、优势与关键要素 | 24-11-11 16:15 |

| ADI 三轴加速度计 ADXL317 在车载拾音上的应用 | 24-11-04 16:27 |

| ADI公司如何让IO-LINK和工业以太网在智能工厂车间通信 | 24-10-30 14:19 |

| 微信关注 | ||

|

| 技术专题 | 更多>> | |

|

| 2024慕尼黑上海电子展精彩回顾 |

|

| 2024.06技术专题 |