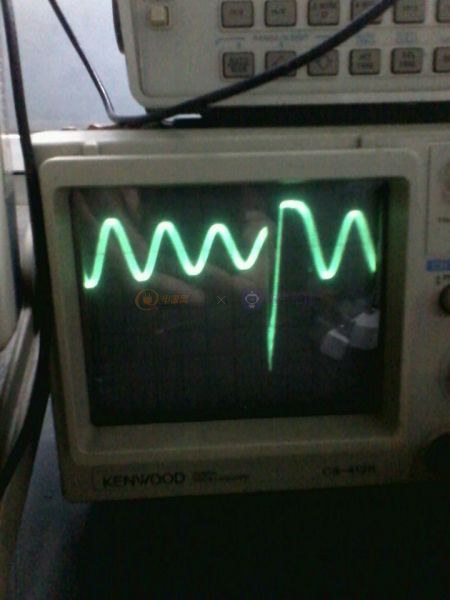

请教UC3842做的宽范围输入反激。输入电压升高后空载波形不能稳定变成间歇波形,发出响声。就像是最小的占空比被限制,如何解决。这个应该不是仅我一人遇到这问题吧

请教反激空载的问题

全部回复(50)

正序查看

倒序查看

现在还没有回复呢,说说你的想法

@qinzutaim

3842电流型IC,楼主的原因应该是3脚没能正确识别到小电流,解决的办法可以从4脚引入方波信号到3脚,或者从8脚引入一个直流偏置到3脚。

TL431的补偿RC, 光耦的限流电阻,初级是采用的2脚接地拉1脚的反馈方式,1脚到地的阻容补偿也都调过均没有改善,又8脚REF给1脚加上拉电阻也没用。

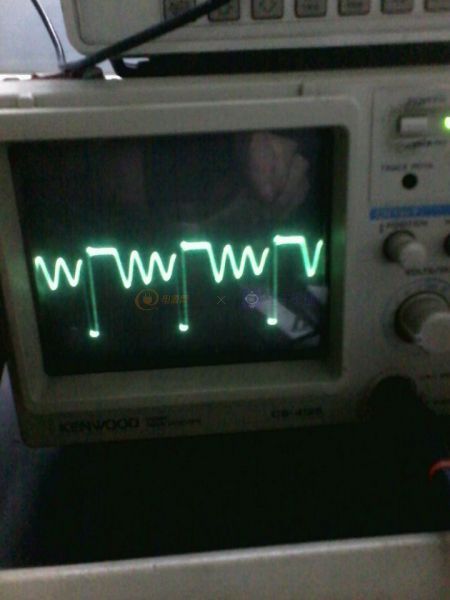

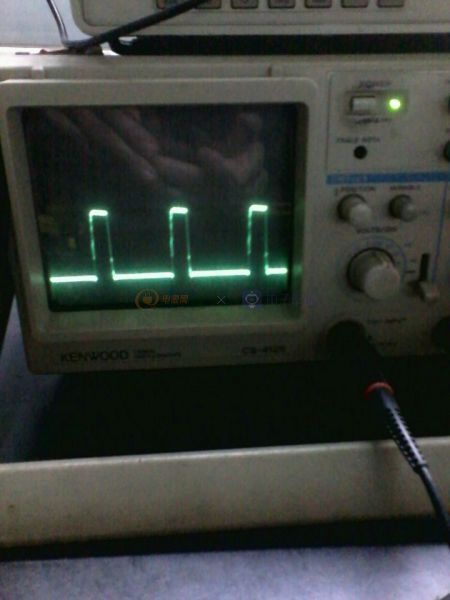

楼上贴 qinzutaim的回复基本就是问题的关键。按这个思路我将UC3842 3脚到地的电容减小甚至不装时空载波形不间歇了,输出此时也稳定,但这时的VDS波形表现为未完全导通就马上又关断的样子如附图。

另外在4脚RT/CT到3脚间加了一个221电容,有很大改善,但输入电压继续增加后还是会进入间歇。

0

回复

提示

@zhenxiang

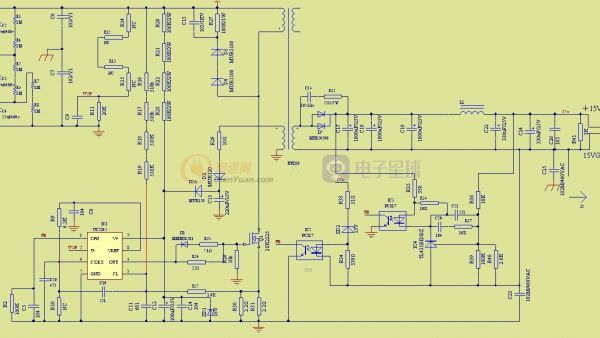

这样说着太复杂了。我还是把原理图贴上来吧[图片]

不知道真版的输入高低压比是多少,我用384x做从来没有使用过C10、R2以及C21。R2的作用从原理上解释不通。对于电流模式的,为了避免计算环路,通常牺牲一点带宽,简单用一型补偿,因此去掉C21,同时由于R38、R37和C20引入的无法避免的零点,必须抵消,因此需要C5,同时需要一个电阻接在Vref和1脚之间(1脚内部是电流源,这个电阻必须要),这个电阻的大小与C5的乘积等于R37+R38与C20的乘积,在这里取20K就行,这样下来,环路肯定是稳定的。另外R34应该是1K。供参考。

0

回复

提示

@rj44444

不知道真版的输入高低压比是多少,我用384x做从来没有使用过C10、R2以及C21。R2的作用从原理上解释不通。对于电流模式的,为了避免计算环路,通常牺牲一点带宽,简单用一型补偿,因此去掉C21,同时由于R38、R37和C20引入的无法避免的零点,必须抵消,因此需要C5,同时需要一个电阻接在Vref和1脚之间(1脚内部是电流源,这个电阻必须要),这个电阻的大小与C5的乘积等于R37+R38与C20的乘积,在这里取20K就行,这样下来,环路肯定是稳定的。另外R34应该是1K。供参考。

输入电压200-1000 输入超过500V时空载波形抖动,输入越高,间歇时间越长。

0

回复

提示