基于FPGA的pwm设计

一、设计需求

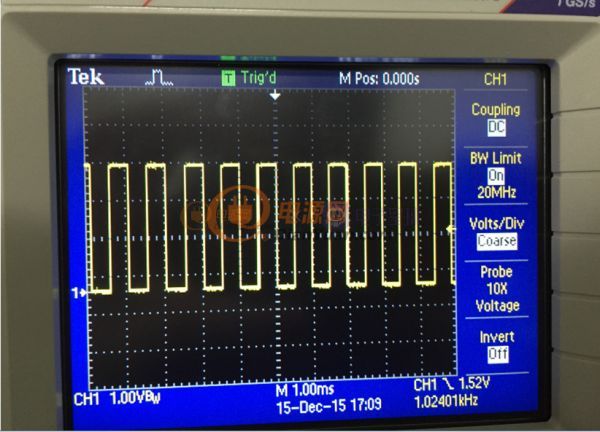

PWM控制就是对脉冲的宽度进行调制的技术,用以等效地获得所需要的波形,以实现对模拟电路的控制。本次设计,运用Verilog HDL语言,完成基于FPGA的PWM电路控制的程序设计。本次操作中,通过按键输入所需脉冲的频率(0--10MHz),通过FPGA得到所需的波形。

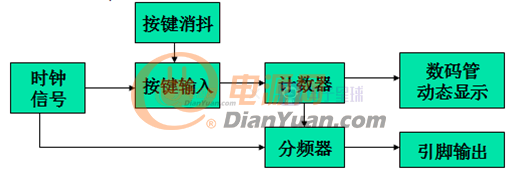

二、设计框图

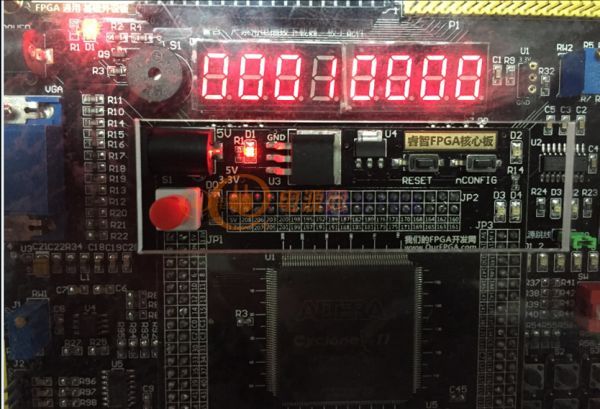

本次操作需运用Verilog HDL完成一个可以设置输入频率(0--10MHz)的PWM设计。本次设计中需完成频率输入、按键消抖、计数器、分频器、引脚输出、数码管动态显示等模块的设计工作。

三、设计工具

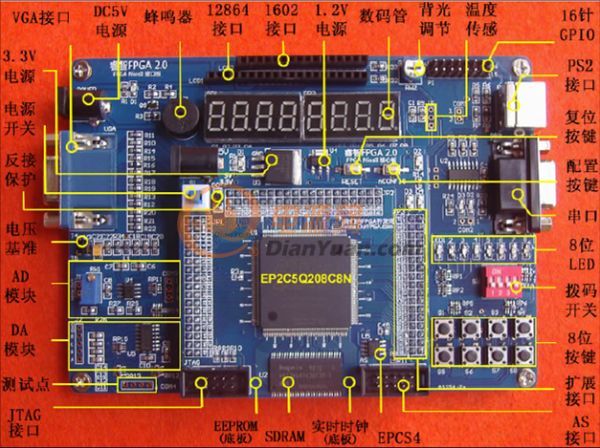

型号:Altera 公司的 CycloneII系列芯片EP2C8Q208C8

软件:Quartus11.0,主要用于编译、综合、下载;

语言:Verilog HDL

四、模块设计

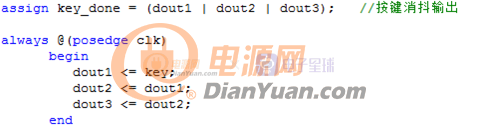

4.1按键消抖电路

实际应用中,按键的瞬间会伴随有一连串的抖动,因而需要消抖。检测出键闭合后执行一个5ms~10ms的延时,让前沿抖动消失后再一次检测键的状态,如果仍保持闭合状态电平,则确认为真正有键按下,开始执行操作。

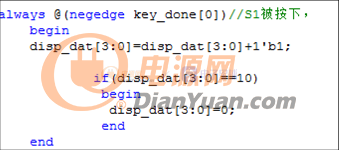

4.2按键输入电路

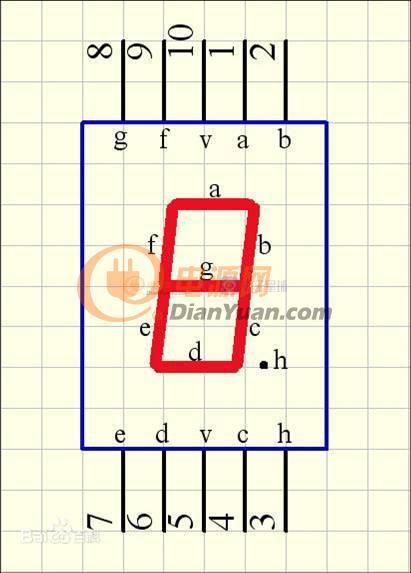

通过按键key_done[0]到key_done[7](对应开发板上s1—s8键),设置所需频率的个位、十位、百位、K位、十K位、百K位、M位、十M位。

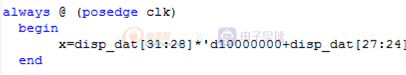

通过按键输入的数字之间没有关联,用一个公式将之联系起来,并作为设定频率的关联参数。

4.4分频电路

FPGA时钟信号的频率为50MHZ,根据设计要求,需要对脉冲进行分频。一路为脉冲c3,用以数码管动态显示电路的驱动;一路为c2,用于得到理想波形。

五、实验结果