研究生马上就要结束了,总结一下自己在实验室硬件电路设计以及FPGA逻辑调试的一些经验教训。

第一次正经发帖,文笔不好,就想到哪写到哪,之后想起来的,再接着修改。今天先开个头,少写一些,待会有事情要去忙。

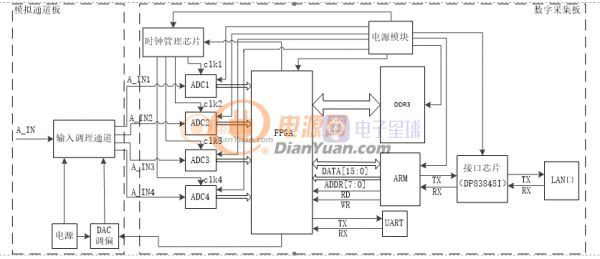

研究生仪器仪表专业,最近几年实验室的项目都是IC测试仪,我主要负责其中模拟模块的AD采集模块的设计调试。采集主要就是把甲方要求的模拟信号(单端/差分、幅度、频率)通过模拟调理通道,把小信号用运放放大、大信号RC电阻分压无源衰减,再加上调偏的加法或者说减法电路,使信号的幅度接近ADC芯片的满量程输入范围,以便获得最大的信噪比SNR。经过ADC之后的数字信号接到FPGA的IO,FPGA内部在对数据进行降速,再讲数据存储进DDR3这种大容量存储器。最后,需要一些通信接口(如PXIe、PXI、LXI等)把DDR3里边存的数据发送到上位机,作进一步的显示以及数据处理。

放一张我毕设的丑图。这是个并行交替采样的系统框图。4个ADC拼更高的采样率。通信接口选的网口和串口。选这两种通信接口的原因是串口只需要RX、TX两根线,再加个TTL转USB的模块,上位机随便找个串口助手就可以接受发送数据了,非常简单、方便。选网口的原因是上一届的师兄有成熟的硬件、软件方案,可以直接拿来用(但是自己也需要了解清楚硬件每一部分的功能,以及软件哪些地方需要改,才能满足自己的应用,毕竟每个人的应用场合不是完全一样的)。不过,用别人的东西,一定要批判的接收,别人的不一定对。我自己就遇到过,师兄们的器件的封装,丝印层画反了,那是个直插的10脚JTAG连接座子,画反了就会焊反,连上就没有反应,PC就检测不到FPGA。So,用别人的东西很爽,但是一定得批判的接受哟。

扯得有点远了。数字电路部分基本上都是成熟的方案(师兄们用过的电路),自己也就选了下时钟芯片以及电源芯片。做采集,数字部分基本上都是之前用过的,主要需要我们对通道进行重新设计。通道部分主要是选一下集成运放和压控增益放大器(VGA)。主要的工作其实就是一个match匹配,把输入的信号分成有限的N个档位,在最小档位的输入信号幅度范围内,需要最大的放大倍数。这时一个运放完成不了,这就需要多级放大,多个放大器串联,还需要VGA等精确调整放大倍数。在最大档位的输入信号幅度范围内,信号需要无源衰减,然后后边的放大电路实现跟随,直接让信号进入ADC。这里的经验就是,没有用过的运放,最好画个2层的10*10的实验板,用信号源和示波器做个试验,看看到底运放的输入带宽是多少,幅度能到多少。运放datasheet上所写以及所画的曲线,不一定在我们的板子上达到。还是要批判的看,避免通道板设计完成后,达不到所要求的效果。

今天没时间了,明天接着总结。