待机功耗即电器设备在关断或没有运行主要功能时其耗电量。假设一个设备一整年下来的耗电量也不小的。虽然待机功耗看似微不足道,但如果考虑到家庭里所有电子设备的累积效应,这个数目就很可观了。

通过有效措施提高有功模式下的效率,降低待机功耗的。一方面可以改进电源的架构,判断系统何时处于低功耗状态,采取措施提高效率。另一方面 提高元器件性能以优化最低功耗。

提高满载条件下的效率,必须改变传统的思考方式,通过降低功耗来提高满载与轻载条件下的效率。必须重点关注架构级和元件级优化的改进,以实现最高效的设计和最低的功耗。特别需要注意的是低磁化电流变压器设计,通过降低轻载下铜损耗来提高效率。

此外,还需要通过顶层系统回顾,以找出给定系统中的所有损耗,然后利用带PFM或突发模式的控制器来降低轻载功耗。最后,划分功率岛区,根据需要利用负载开关来启动/关断子电路,也可以降低待机功耗。

功耗一般分为两种,来自开关的动态功耗(电容充放电)和来自漏电的静态功耗。尽可能的降低功耗,元件的选型就很重要。

1、使用MOS管门电路,尽量少使用TTL门电路。

2、给电路设置休眠,待机状态,能够进入省电模式。

3、将电路设计最简化。模块分布合理,减少布线。

4、降低工作频率。

5、旋转低功耗的元件进行电路的设计开发。

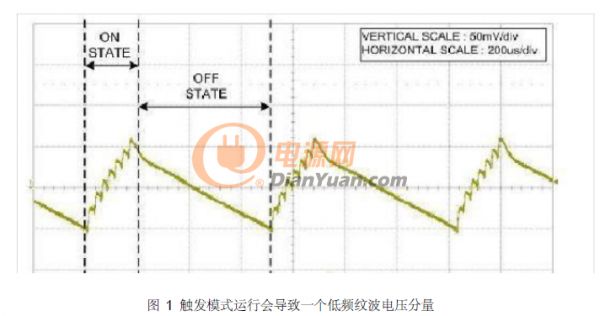

电源的主控器功耗要较低,其触发模式的一个负面影响是会导致输出端上一个额外的低频率纹波电压。在开启状态时,输出包括了与电源正常开关相关的典型纹波电压。然而,在触发频率下会带来更多的纹波含量。由于触发频率很低,用一个L-C 滤波器对其进行衰减是不切实际的。相反最好通过增加输出电容来减少低频输出电压偏离。

通过控制器降低静态电压。许多控制器都使用准谐振开关来提升所有负载级别下的效率。准谐振反向电源使用了由变压器漏极电感和寄生电容形成的谐振来以更低的损耗启动。

另一个是电源的RCD钳位元件,通过限制MOSFET漏极上的电压峰值来降低振铃和避免过压应力。该电压峰值是在MOSFET关闭并突然中断主绕组中的电流时由存储在变压器漏极电感中的电能引起的。

降低钳位电路中电压峰值和损耗的第一步是设计一个具有最小漏极电感的变压器。除此以外,我们还可以增加钳位电阻以进一步降低损耗,但这样做同时还会增加电压峰值幅度。在开关周期的复位阶段, 反射的输出电压被外加在会导致更多损耗的钳位电阻两端。

降低钳位电容还会降低轻负载损耗。当控制器处于触发模式运行时, 钳位电路就会在开启状态间进行放电。如果钳位电容太大, 那么过多的能量就会存储起来, 并在关闭状态期间耗散掉。在一些情况下, 钳位电容在下一个开启状态开始前可能不会完全实现放电。将钳位RC网络的时间常数设置为开关周期的10 倍左右是降低该损耗的一个不错的常规法则。