作者修或者改东西秉承提高效率或增强性能或加多功能的原则(容易烂尾-_=)。

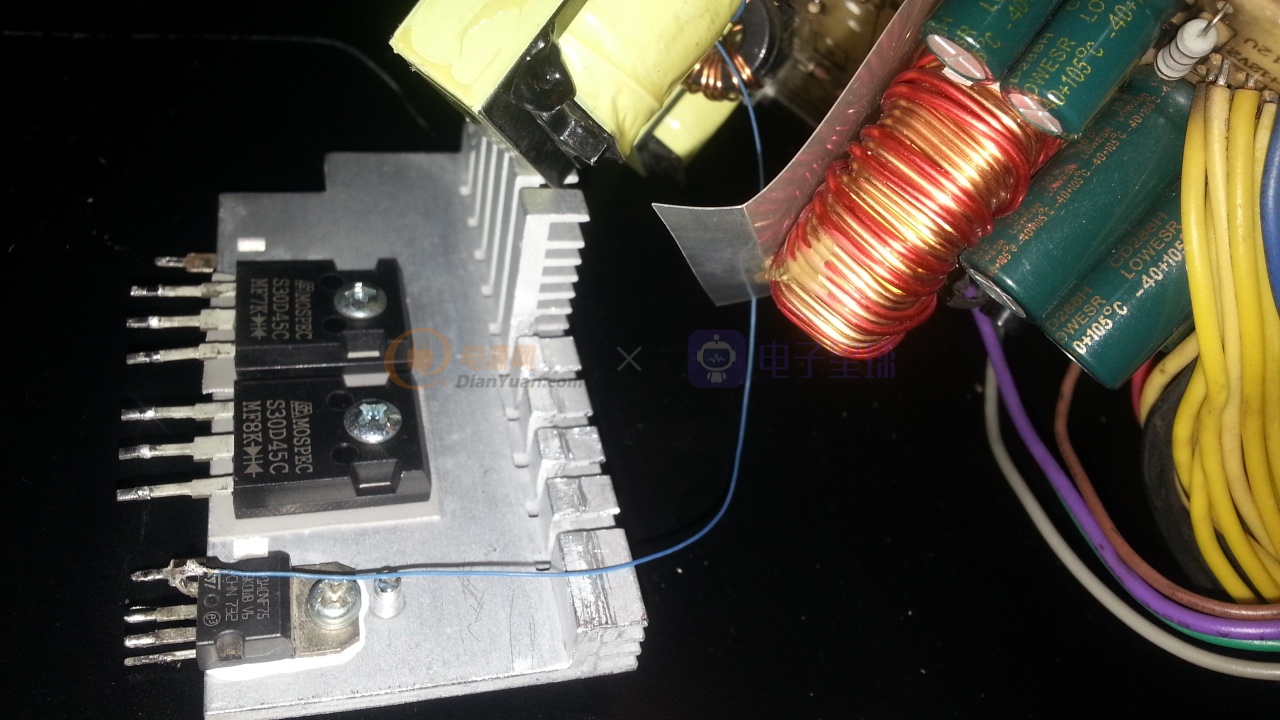

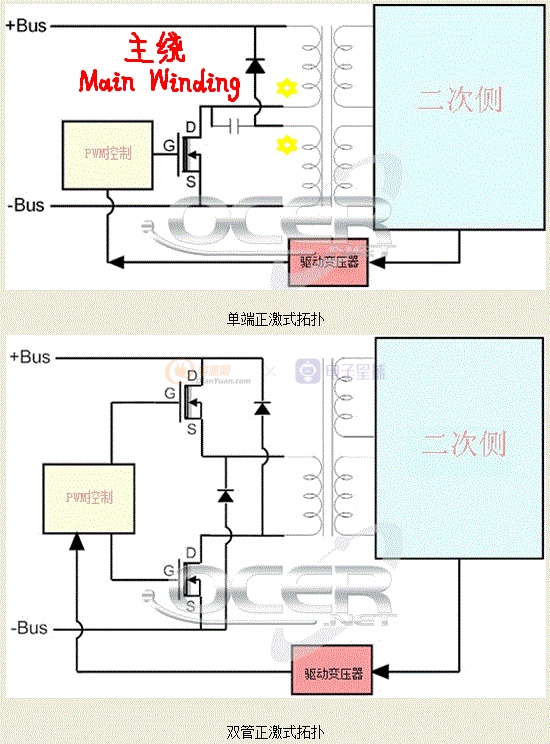

1)开胃菜:由于常见的单管正激电源是电压馈电型,整流期间的波形是方波,因此可将次级改为混搭Hybrid组合,即MOS整流,肖特基续流(续流期间不是方波,改起来麻烦):

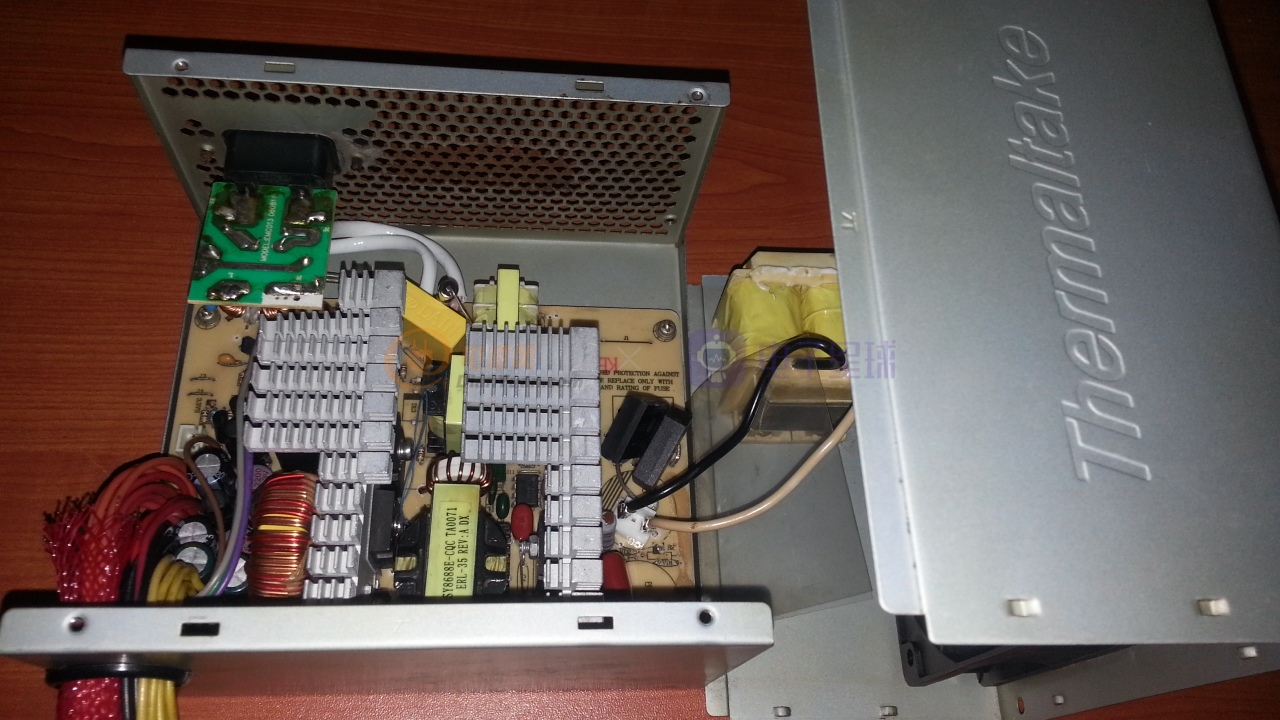

1.1)经过作者试绕几匝测试绕组,测定出“磐古V600”,其(靠铁壳的)主励磁绕组估算为40匝,绕向为逆时针。推荐主12V改为(绕向同为逆时针的)1.5匝(在中柱和边柱各绕1匝可实现,依着磁通方向哦!因我国电压常高于额定220ACV)给100V的MOS提供自驱电压,V60100C沟槽型肖特基TMBS跷腿续流。

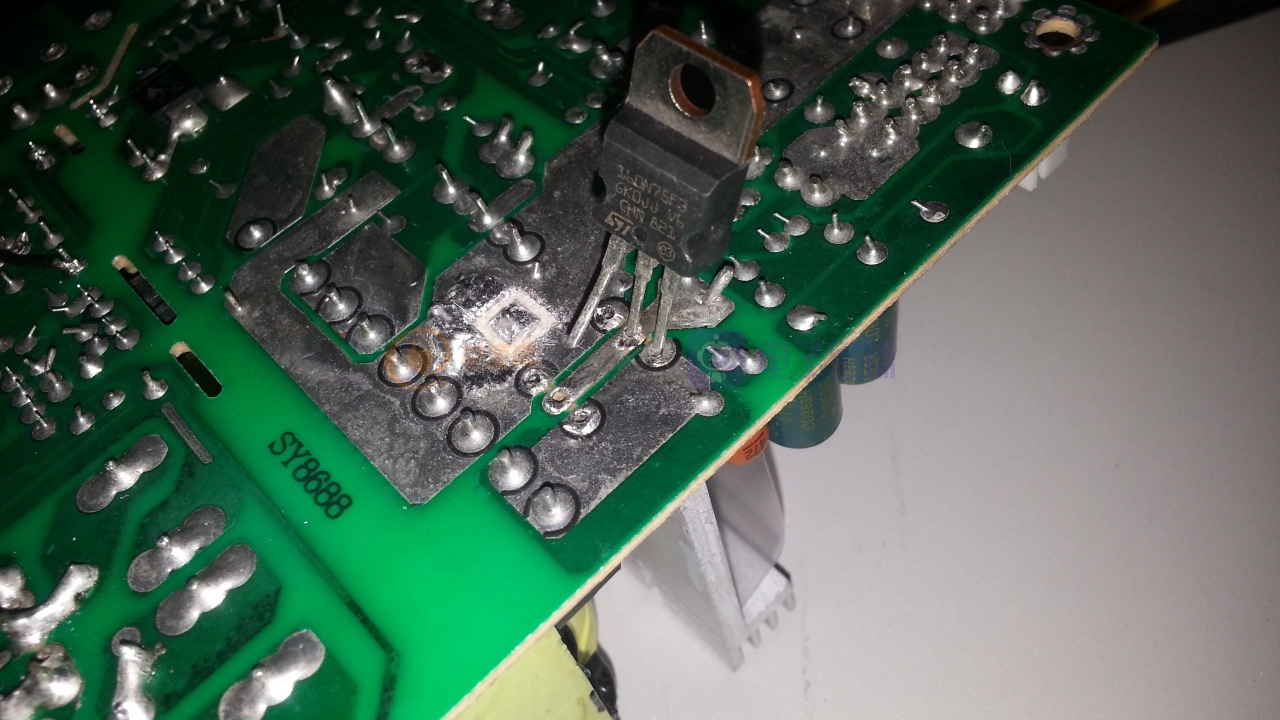

1.2)作者实际使用2匝自驱的STP140NF75。本该考虑GS毛刺电压增加稳压管,且75V的该MOS耐压明显不足100V被我主观忽略了,凑合用的,因为不是我主要的构想意图,哈哈。还曾顺并了一颗100V&3A的肖特基到该MOS的SD极减轻反向恢复损耗和该同步MOS未完全导通时让顺并的肖特基分摊电流稍微提高效率。

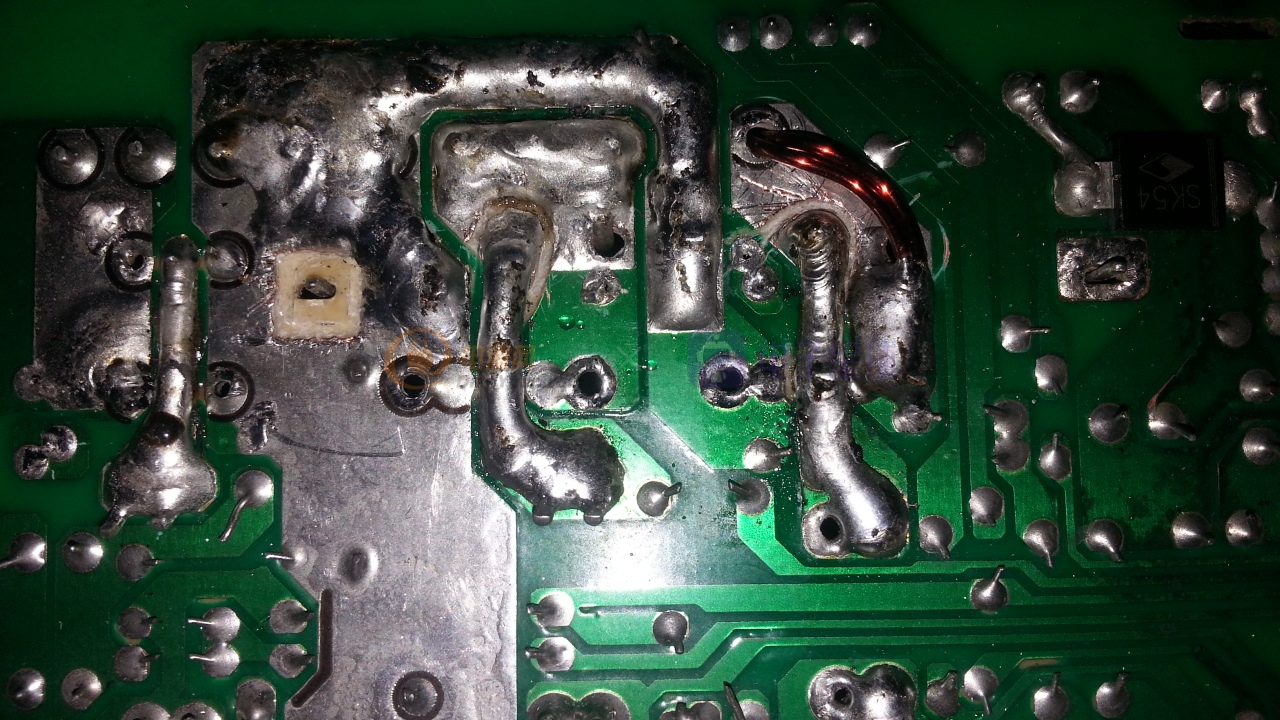

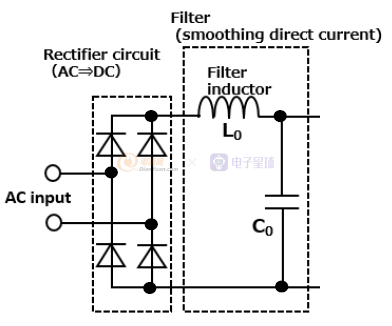

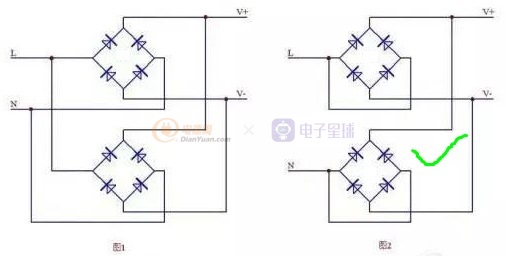

2)主菜:将常见的电压馈电型单管正激电源改成大致上的(准)电流馈电型。即将被动式PFC大铁芯电感移至桥后(思路源于电磁炉,建议降低原机的电感量,并且建议拆除许多电源的大铁芯电感所并联的约1-2.2uF的CL电容。作者认为该CL电容是减轻断电打火的,因为众所周知电感的性质是在突然切断输入时如果无法续流/储能无处释放就会击穿空气而打火),并最终使用了大概8uF的CBB电容代替了原先的410uF电解电容(即2串820uF铝电解)。

优势2.1)由于整流桥后的频率翻倍,可以节约电感材料且降低铜损(本人最终重绕了1个约0.25mH的未生锈的硅钢片电感代替约30mH原有锈斑的硅钢片电感。最易得的替代品是约0.33mH的电磁炉黄白环电感。实际试过最低感量约100uH的φ20mm的铁硅铝电感亦可代替。)。被动PFC电感置于整流桥后不光实现了PFC还兼具直流母线的储能。

优势2.2)8uF的CBB电容代替原先的大容量铝电解电容,没有明显的上电冲击,可以取消抗冲的NTC,且CBB的寿命明显比铝电解长。

优势2.3)由于8uF的CBB电容很小,因此在稍微加重负载时,母线的电压将由几乎平直的约311DCV(理论值220√2)明显降低成驼峰形的约198DCV【若带载跌落后的轮廓恰好是正/余弦的半周,则理论直流分量值220√2÷(π/2)。电感量不足的话会畸变和跌落严重】。这使得开关寄生尖峰的问题得以缓解。作者使用了700V的MOS代替900V的MOS,同理次级肖特基用了80V的代替100V提效。同时稍降低了辅助电源的启动电阻损耗。

劣势2.a)需要折中选取被动PFC电感:取值若太小,则母线储能不足;若太大,则PF值偏低。置于整流桥后的电感必须抗直流偏置,剩磁也较大。

劣势2.b)如果是作者示例的ATX电源,由于母线储能的减少,可能导致保持时间hold-up time无法满足一个AC周期cycle(对应到美国60Hz/我国50Hz约16ms/20ms)。作者的观点是杯水车薪的16ms/20ms并不能保证机械硬盘的磁头复位(机械装置动作通常慢吞吞),只是用来给服务器后备UPS提供短暂的接力过渡和掉电监测所用(自己的家用小白鼠PC无所谓)。

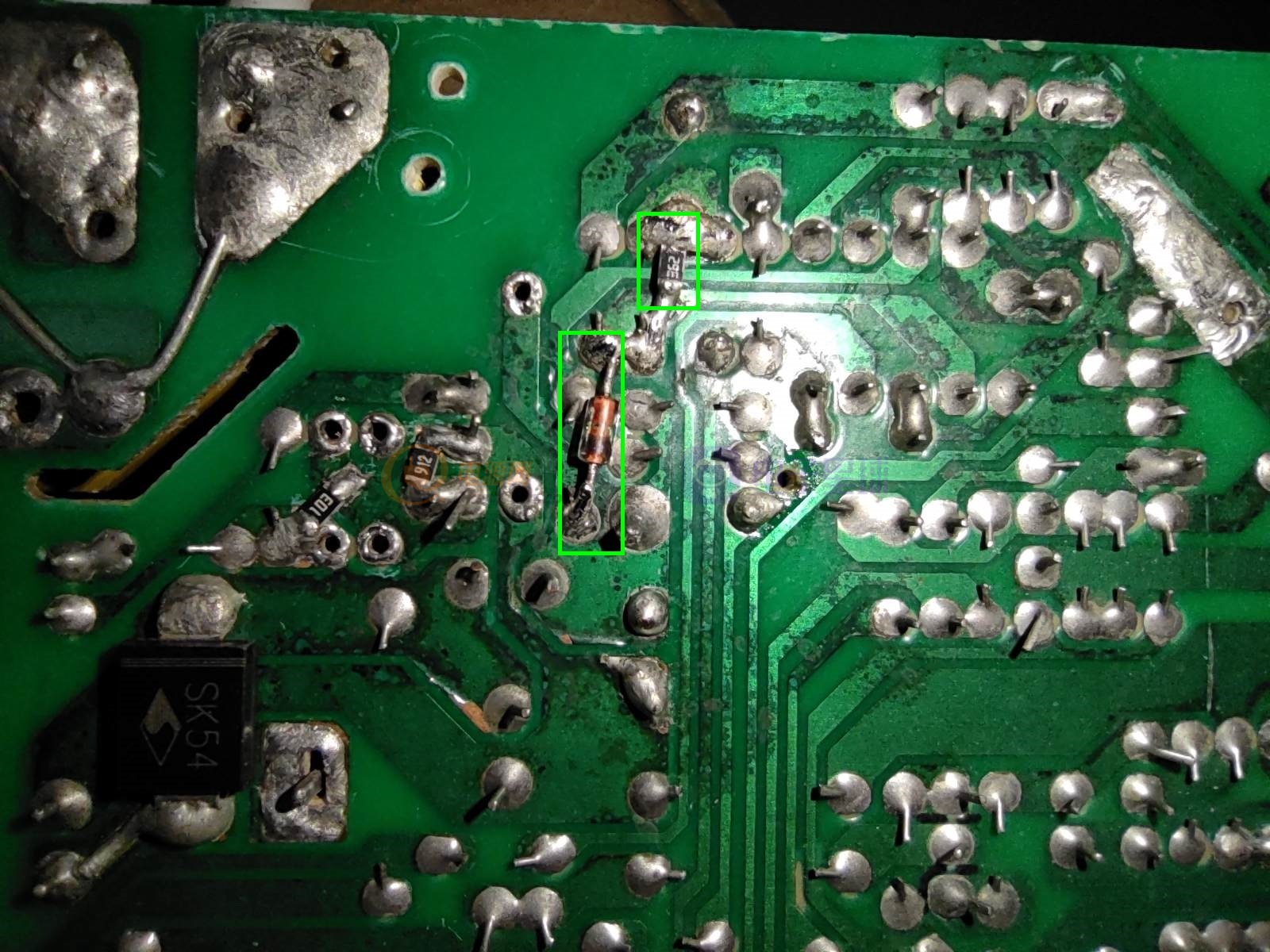

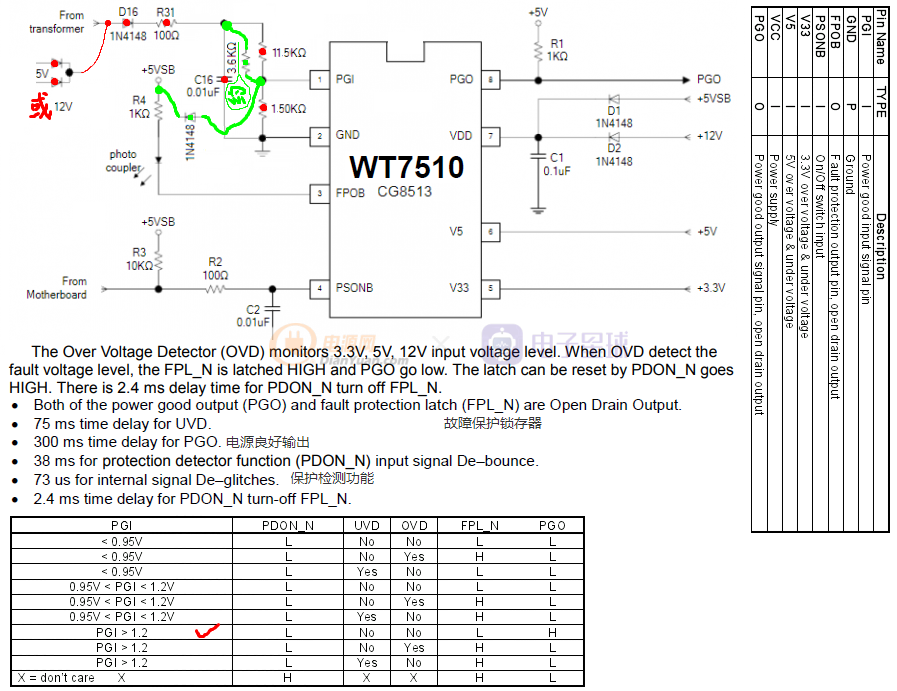

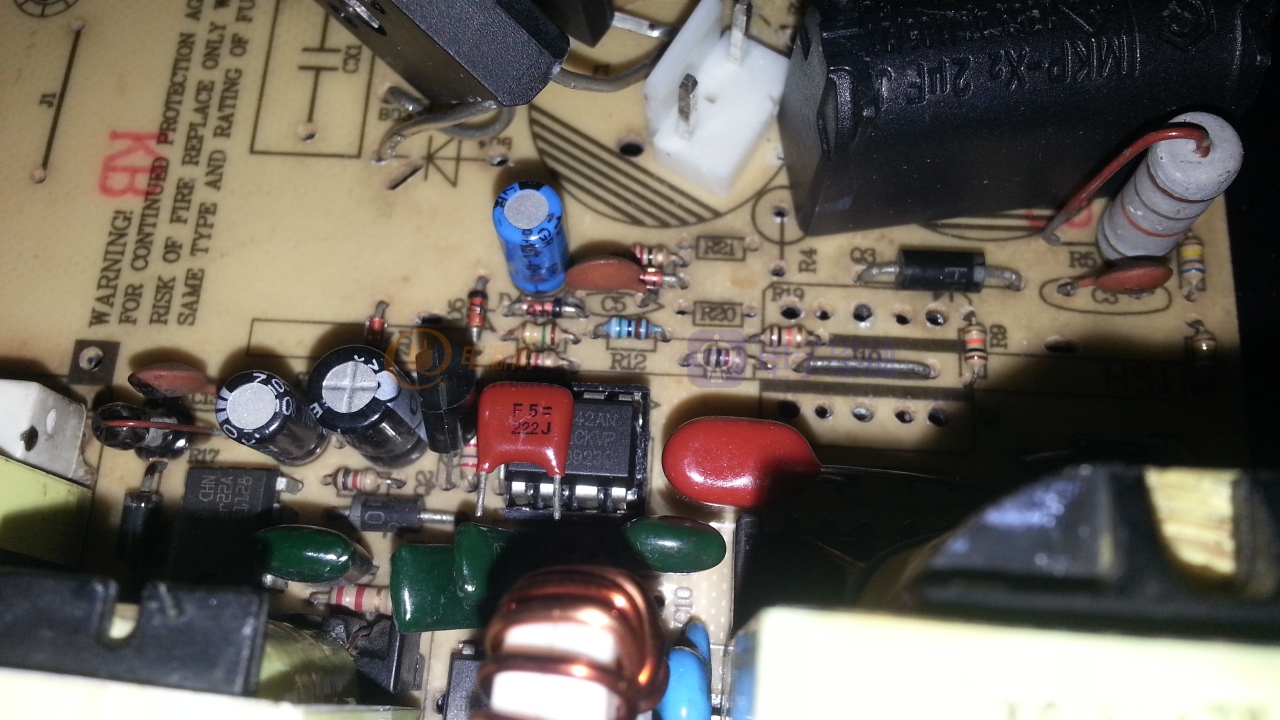

劣势2.c)如果是作者示例的ATX电源,由于主变压器的波形和峰高改变巨大,可能需要调整ATX的Power-Good电路(矽创保护ST9S313或WT7510或CG8513可参考本例附图修改)。

其它多项不是很重要的实际改动和考虑BTW:

2.X1)担心占空比可能不足(由于母线直流下降),改小振荡电容后将UC3845/UC3844改为了UC3843/UC3842,基本维持在原有频率。本机原有的单管正激配置跨接了一颗100nF电容组成了SEPIC结构,这是一个非常好的附加设计。

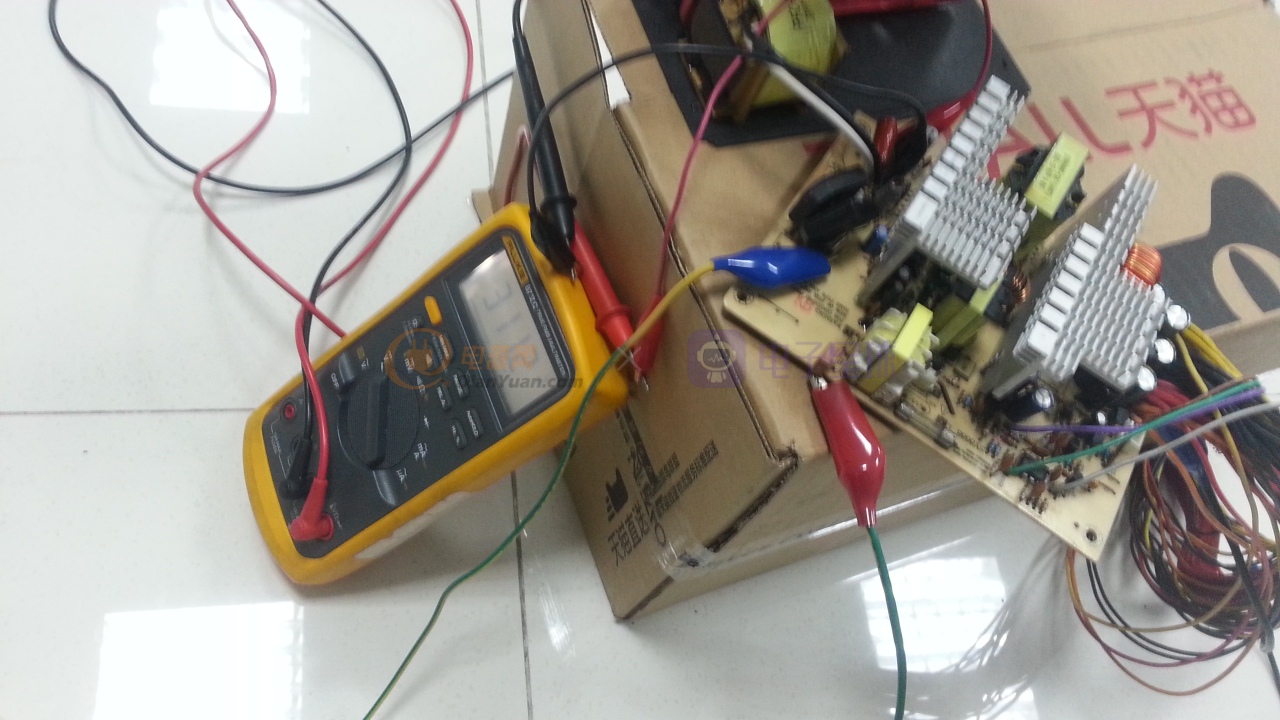

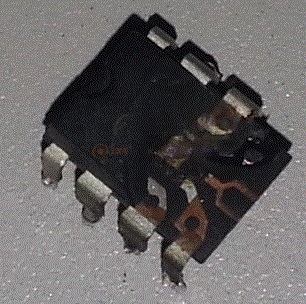

2.X2)作者曾试探性使用了顶天650V耐压的大个子20N60C3/20N65C3(最终把4个脚的65C7095暴殄天物当3个脚用了),带载12V&65W车灯也扛了许多次,虽然最终估计是因为裸奔无风扇试机太久殉职了。

2.X3)本例使用的单管正激电源改前和改后都仍然是(不能裸奔的)硬开关拓扑(而参考的常见准谐振反激式电磁炉为软开硬关),也就是主MOS的反向恢复特性无需考虑(曾试用很差达2us的700V&12A&0.9欧的2SK2828完全正常)。

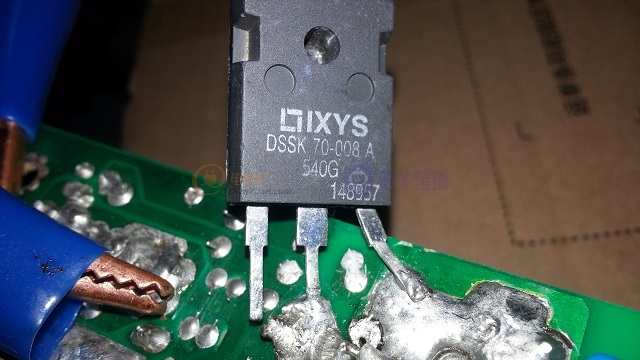

2.X4)作者在使用2个桥堆和次级的肖特基时都是尽可能跷腿后各自独立使用,利于均流,而不是直接并联。

2.X5)进线交流端不建议添加2uF的CBB,会加大上电冲击,虽然对EMC或者说EMS/EMI有利。而且改到桥后的被动PFC电感断电时的剩余储能可以由桥堆的4颗二极管同时导通得以续流。

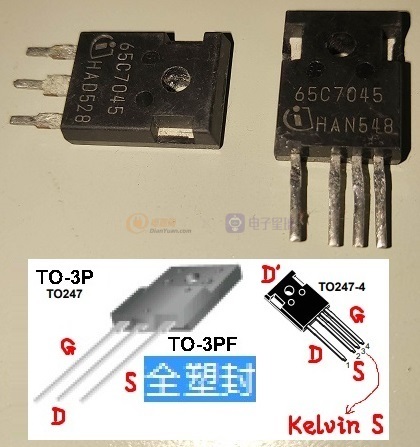

2.X6)作者挖掉了散热片的电气GND连接(实测4个脚的65C7095/65C7045也不是S极与Tab相连,希望破灭。如果有那种S极与Tab相连的设计,作者还设想用3个脚和4个脚的65C7095/65C7045做成共裸散热片的半桥呢。尽管S极直接并联在如推挽拓扑时也有优势,然而分析了下感觉厂家没有将4个脚的MOS设计改成S极与Tab相连也说得过去,因为散热面积大的衬底与MOS的D极是相连的。),虽然对EMC不利,但是可以拆除绝缘垫片后再涂抹导热硅脂,对散热有利。

2.X7)由于原机负12V采用的反激取电,因此将风扇改为了24V(硬接在正12V和负12V之间),用以代替假负载。

2.X8)洗刷刷,除锈,锉了散热片的毛刺,换了铁壳。大量埋铜拖锡,加强了非晶磁环,铁粉芯磁环涂了些环氧树脂防热空气老化。

修改/强化的东西有时作者竟然希望它早点坏,因为不坏时作者懒得再折腾。修改该电源时就凑合使用了很极限的元器件,因为主要是想按第2种方式改。喜欢把东西做得皮实和多功能,哈哈。

太耗时啦,已到深夜,有些字是用鼠标写的,大家将就看哈。趴窝睡觉~