大家好,我是电源漫谈,很高兴和各位一起分享我的第32篇原创文章,喜欢和支持我的工程师,一定记得给我点赞、收藏、分享。

根据前述文章,数字电源之我见(1)典型控制系统框图 中的介绍,控制一个数字电源,首要的一步就是要将模拟信号转换为数字信号,这部分工作由芯片内的ADC来完成,本文就ADC的典型结构及时钟分配,和分辨率特点,基本工作原理等特性做一个概括性的介绍。

一.ADC的典型结构

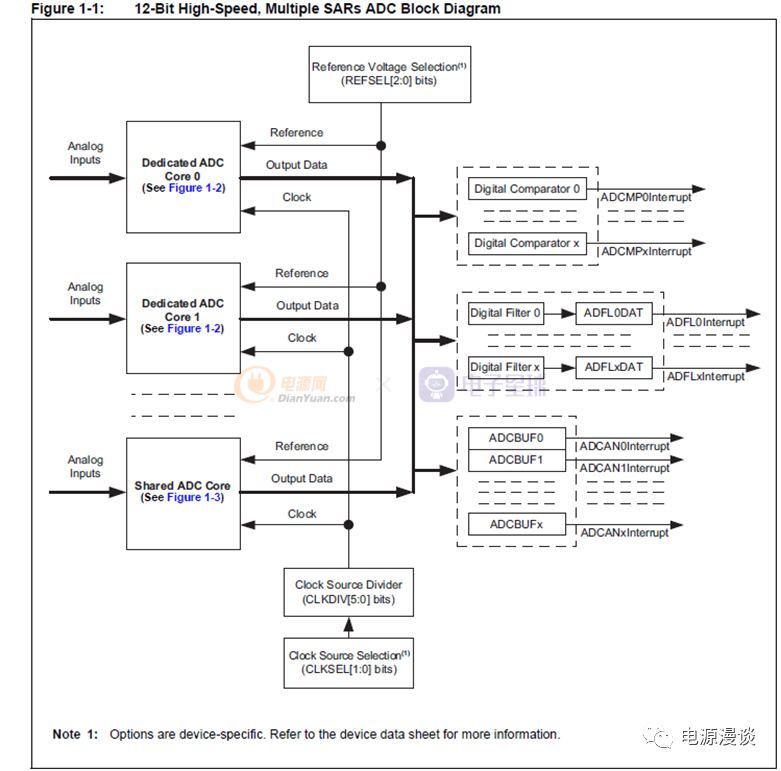

对于dsPIC33C系列产品来说,ADC的基本框图结构如图1所示,

图1 12bit的多核SAR ADC的基本结构

从图1中的基本结构可知,其内部包含多个ADC的CORE,其中编号最大的一个CORE是共享ADC CORE,其它为独立ADC CORE.

ADC的CORE可以根据所连接的通道的信息,如输出格式,测量模式等对输入信号进行处理,经过转换后的结果会放在每一个模拟通道专用的结果buffer寄存器中。当对数字滤波和数字比较器进行了配置,允许使用相应通道的结果时,这个结果可以传递给数字滤波器和数字比较器来做相应的动作。

二.ADC的采样转换基本过程

简单说来,ADC转换过程主要包含三个步骤,首先对输入信号进行采样捕捉,当捕捉到这个信号后,就会进行保持(holding),将结果传递到ADC的转换器中,最后,就是转换过程,将模拟信号基于通道设置的数据格式信息,转化为数字信号。

从本质上讲,数据的采样过程,就是使用输入信号对芯片内部的ADC的采样保持电容进行充电,所以,采样时间要足够,才能让采样充电后的电容电压值等于输入信号。采样之后,在一个合适的时间,输入信号就会和采样电容断开,将电压传到转换器中,这就是所谓的保持,之后就是对信号进行数字化转换,并提供相应的转换结果。这部分我们后面会根据不同的CORE特性进行详细探讨。

因为涉及模拟信号的数字化,所以ADC需要一个工作的时钟源,及一个量化模拟信号的参考电源,这两个参数都是可以选择的,包括时钟源的分频等。

三.ADC的时钟配置

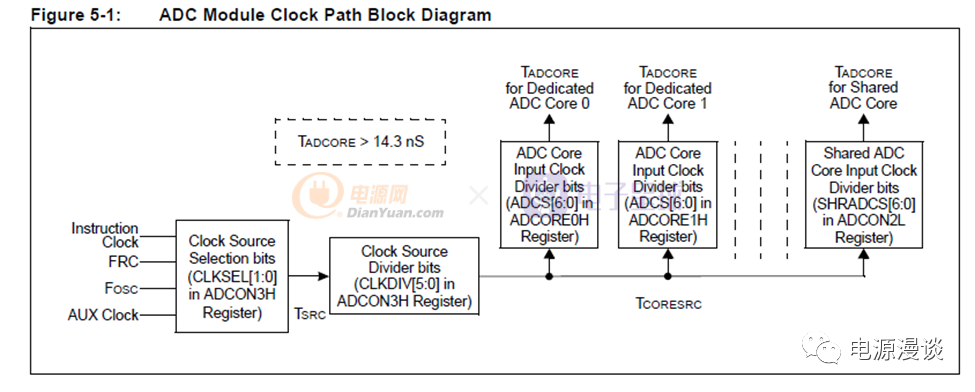

图2 ADC的时钟分配

ADC具有多个可以选择的时钟源,时钟源可以在ADCON3H中的CLKSEL中设置,时钟源的周期就是TSRC,如图3所示。

图3 ADC可选择的时钟源

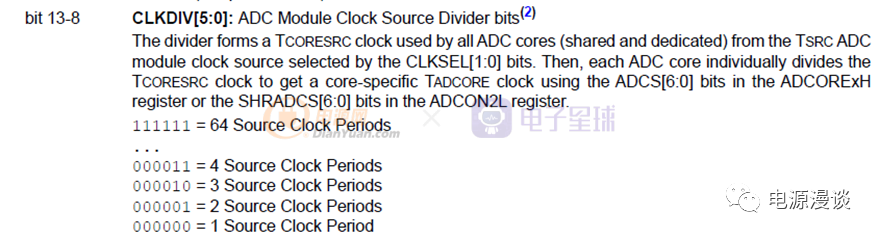

选择的时钟源可以进行分频,可以在CLKDIV中设置,这是时钟源进入ADC模块后的分频,它在ADCON3H中,如图4所示。

图4 ADC模块的时钟分频选择

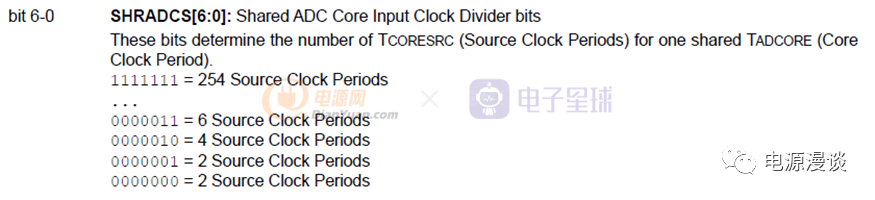

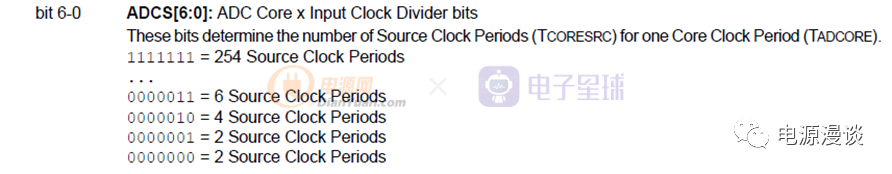

模块分频后的时钟就是TCORESRC,它会进入每一个ADC CORE中。之后每一个ADC CORE可以设置不同的分频来给每一个ADC CORE设置不同的时钟,这部分分频在各个ADC CORE的寄存器中,如独立CORE在ADCONnH中的ADCS位,或者共享CORE的ADCON2L的SHRADCS中设置。在每一个CORE中分频后的时钟称为TADCORE,如图5,6所示。

图5 共享内核的时钟分频

图6 专用内核的时钟分频

总的说来,就是选择一个初始时钟源,进行一个模块内的分频,一个CORE内的分频,最终得到ADC CORE的采样转换时钟。

最终经过分频后的CORE的时钟需要不能超过70MHz,那么也就是TADCORE大于14.3nS,这一个基本要求需要满足。

四.ADC的转换分辨率

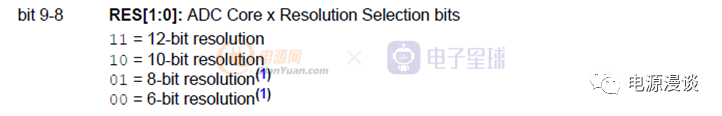

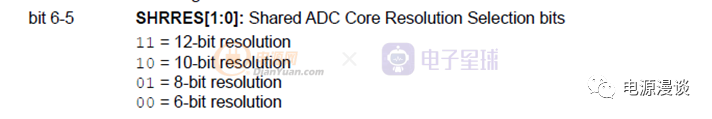

每一个SAR ADC的内核的分辨率或者结果位数是可以灵活设置的,分别在相应的寄存器中设置,如独立CORE在ADCOREnH中的RES来设置,共享内核在ADCON1H中的SHARES来设置,每一个内核可以设定不同的ADC转换分辨率。

图7 独立内核的ADC分辨率设定

图8 共享内核的ADC分辨率设定

值得注意的是,芯片复位后的ADC默认分辨率为最大分辨率12bit。

以上就是关于数字电源的重要外设ADC部分的一些基本特性的概述,包括工作原理,内核分类,时钟分配,分辨率特性等,后面我们会更进一步的去讨论相关特性。你了解了吗?^_^