我是Sig008,从事信号、电源完整性工作,喜欢钻研,喜欢交流,今后会多把一些理论知识以简单易懂的方式梳理出来,供大家一起交流;

大家也可以添加我的个人微信,进一步交流讨论:LLFF_5021

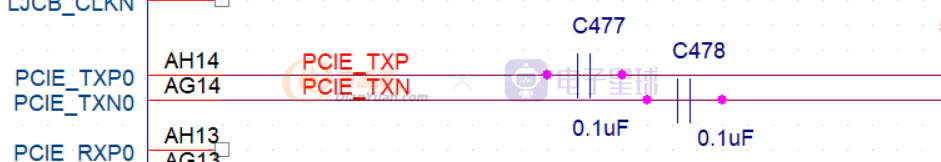

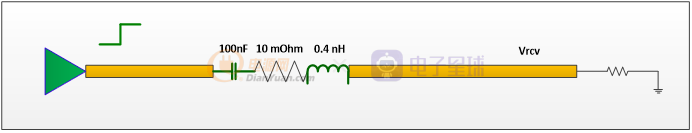

我们经常见到信号中串有耦合电容,如下结构。

AC耦合电容的作用有:

隔离直流分量;

允许电容两端使用不同level的电压值;

防止热插拔时的瞬态电流;

协议要求,检测对端用;

等等...

这些不是我们的重点,下面我们来直观的看一下,信号通过电容后的影响;

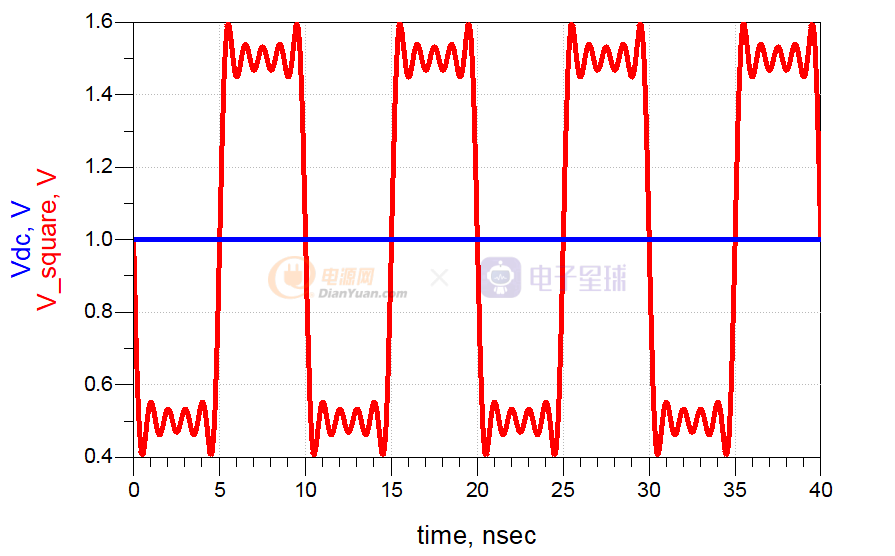

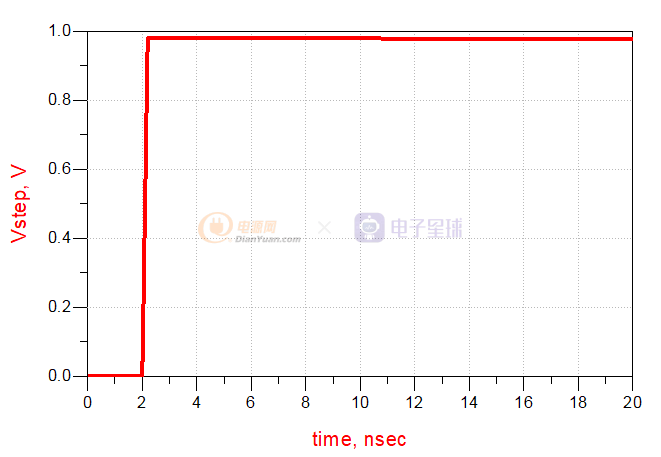

对于一个没有AC耦合电容的100MHz信号波形如下:

此时1V摆幅的波形中含有1V的直流分量;

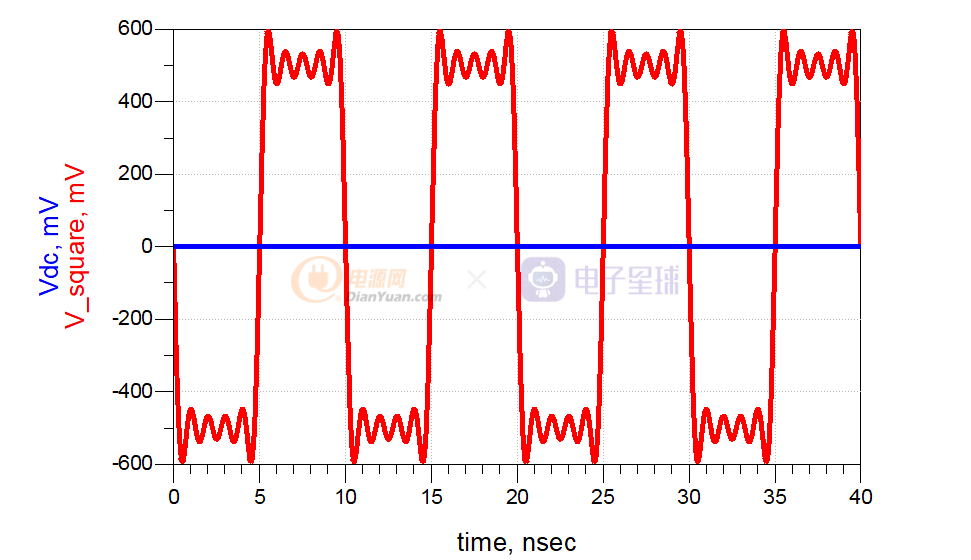

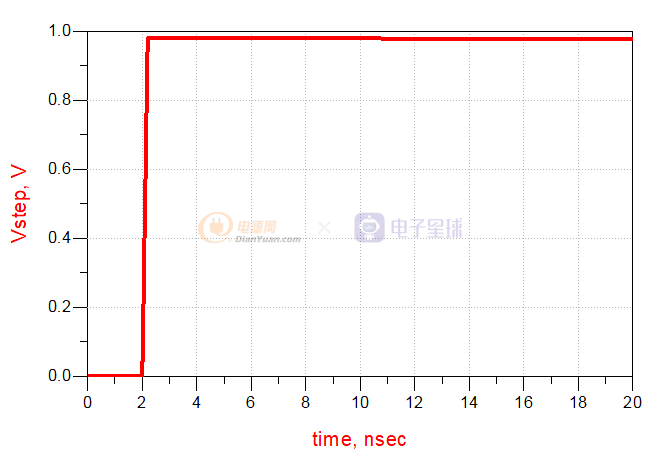

信号过了220nF AC耦合电容后:

此时,经过100nF耦合电容后,信号当中的1V直流分量没有了;

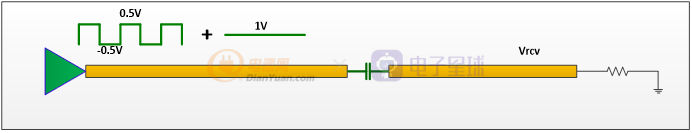

此时可以在电容后边加上其他level的电平:

这就是信号通过AC耦合电容后,隔去直流成分,以及达到收发芯片使用不同电平的效果;

接下来,我们看一下容值的选择:

电容的阻抗 Z=1/(2*pi*freq*C)

由此可见,当选择的电容过于小时,对于低频部分阻抗越大,下面直观观察波形:

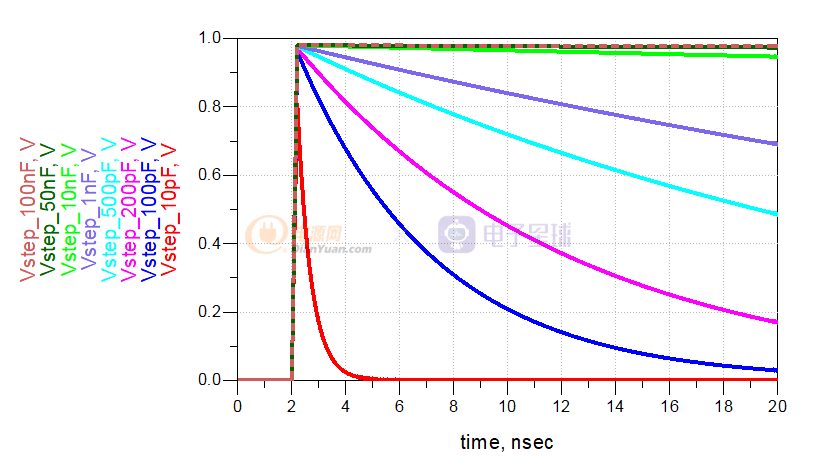

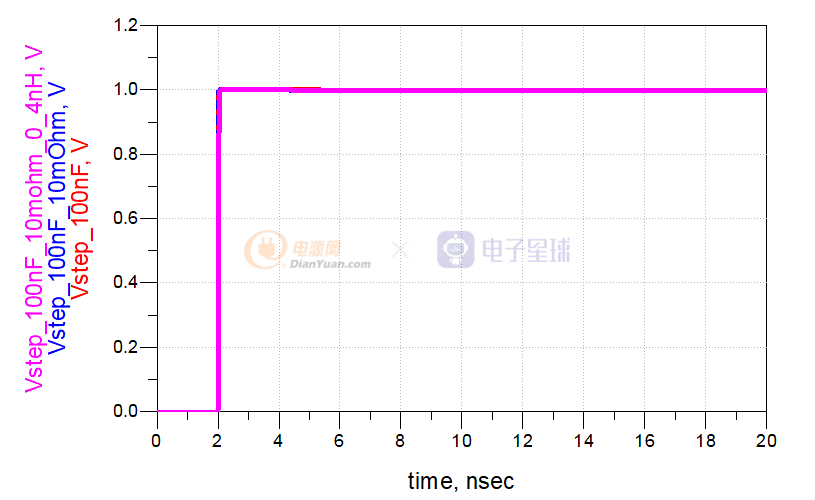

发送端驱动一个上升跳变边沿,波形如下:

再次基础上,加上100nF的电容,波形如下:

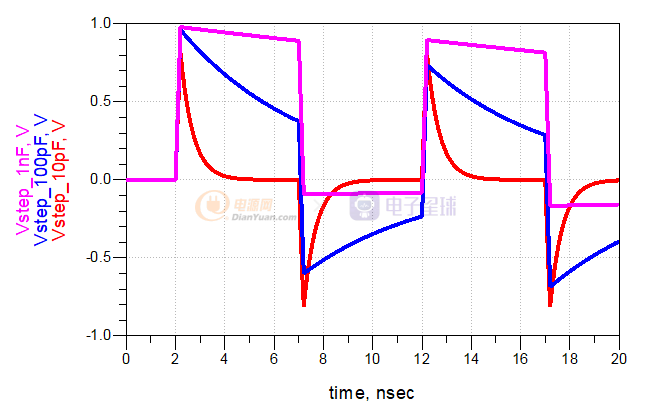

此时,跳变信号经过100nF电容后,几乎没有变化,减小电容为10pF时,波形如下:

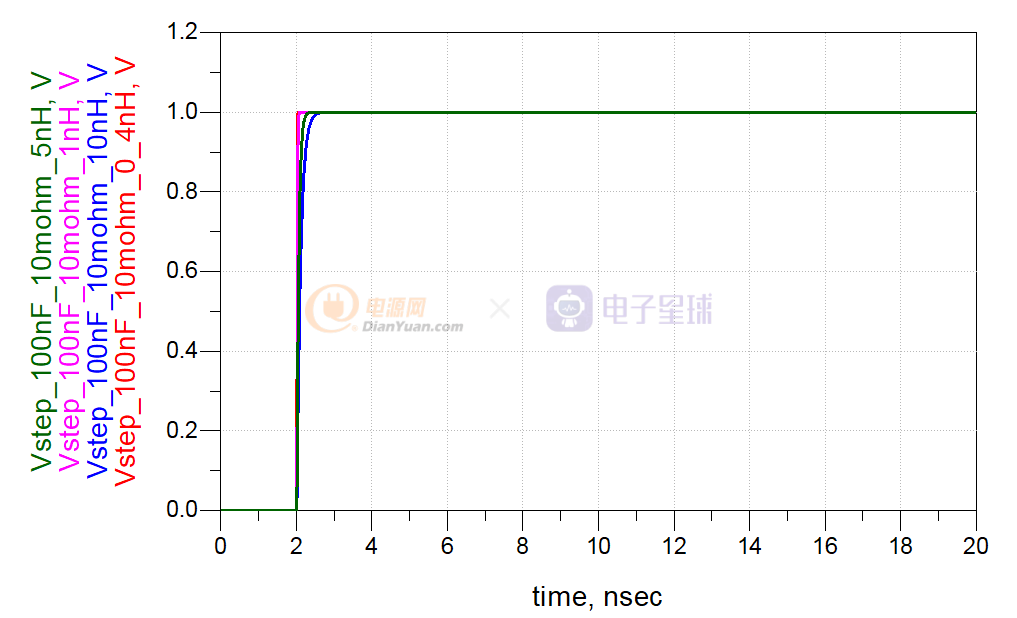

逐渐增加电容大小:

由仿真波形,可以直观的得出结论,电容容值越大,信号越可以顺利通过;

这里就是一个电容充电的时间常数问题,τ=RC

而电容的电流 I(t)=A*

从公式中可以看出,通过电容的电流迅速升高,然后按照上述公式,程倒指数下降,而下降的速度和指数的幂有关,幂越大,下降的越快,而当幂当中的τ,也就是RC的值越小时,电容电流下降的越快,相反,当RC,也就是电容的值越大时,电容电流下降的越慢,如上图,当电容达到50nF时,几乎能保持相当的时间了,足够满足100Mhz以上的信号了。

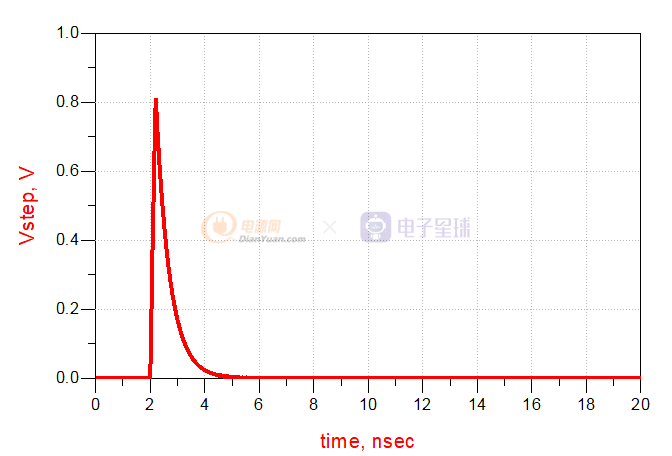

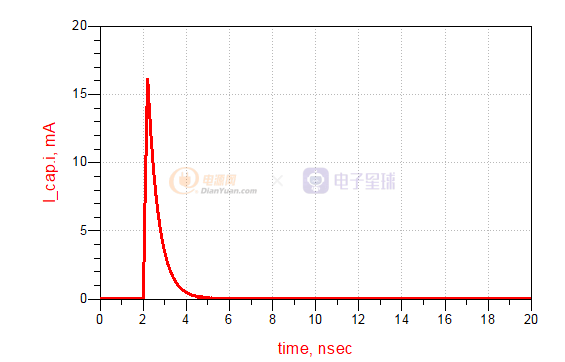

电容的电流见下图:

可以看到,电容电流的形状和通过电容后的波形形状是一样的;

通过演示,可以很直观的了解信号通过电容后是什么样的;

看样子,电容要选大一点的;

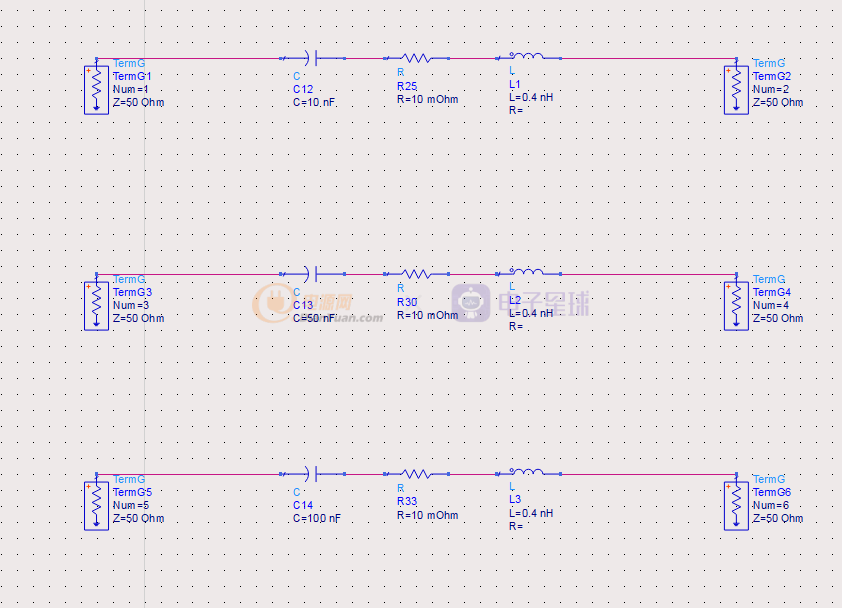

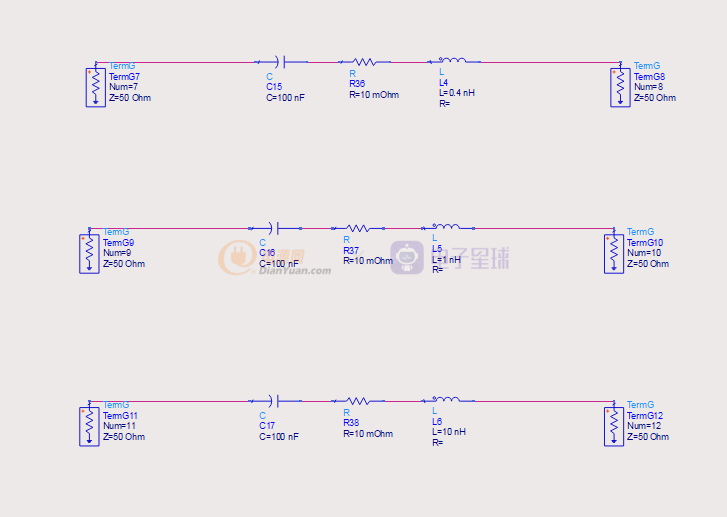

当然也不是越大越好,原因之一就是,电容都不是理想电容,还有寄生电感(ESL)和等效串联电阻(ESR);

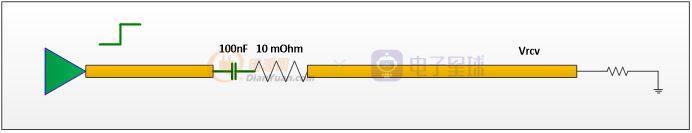

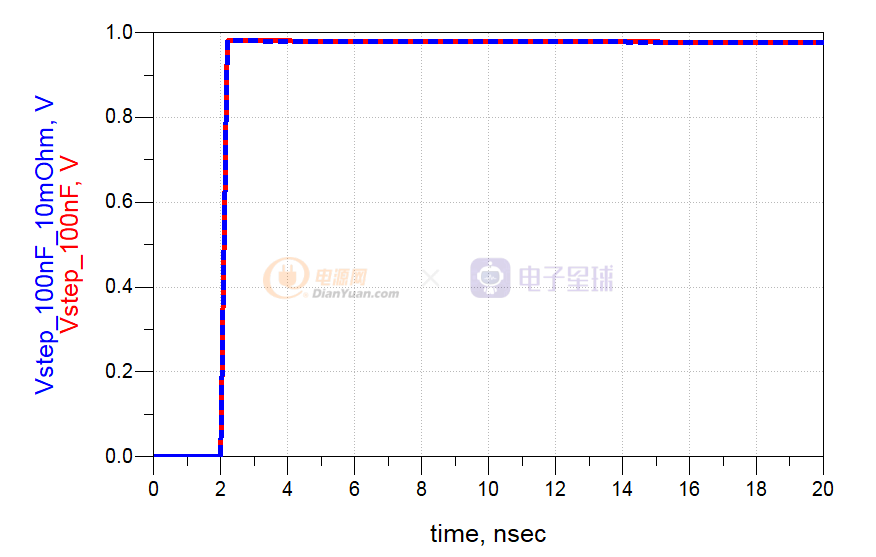

下面看一下在100nF的电容后面紧跟着一个10 mOhm的电阻,波形如下:

可以看到,波形几乎没有变化,由于计生电阻很小,没有构成影响;

继续串接一个0.4nH的电感,波形如下:

当前上身边沿为30ps,可见几乎也没有影响,下面来对比一下不同电感值的波形:

由此可见,当电感大了之后,信号的边沿会变缓,因为,电感阻高频,所以边沿中的高频成分有所衰减,但是电感要到几nH之后才会体现出这种影响,而一般几uF,几百nF的电容寄生电感大概为0.4~0.6左右(因厂家、封装而异),因此一般选择100nF、220nF的电容是比较合理的。

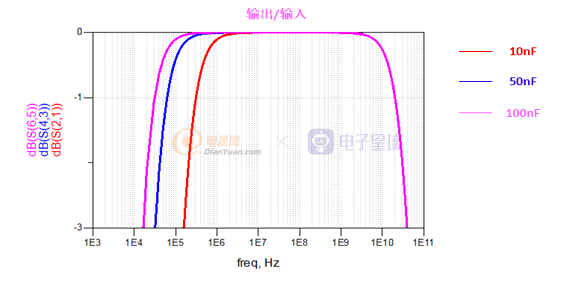

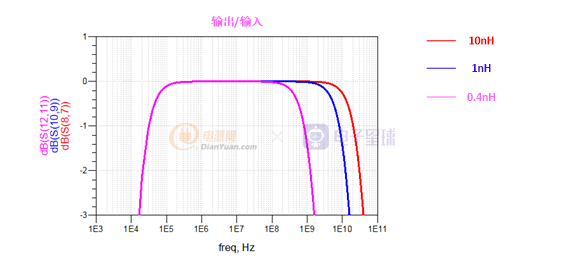

下面看一下电容容值和其寄生电感的值对频谱的衰减程度:

不同容值电容的衰减频谱

不同寄生电感的衰减频谱

可以看到,实际的电容相当于一个带通滤波器,而对于1nH的电棍,高频部分要到11GHz的频率才衰减到-3dB。

对于电容容值的选择,以及信号通过电容后的影响,我们已经非常清楚了;

当然电容不是越大越好的原因之二,就是电容大了之后封装也会大,从而PCB的焊盘也会大,这对信号的阻抗会造成较大影响,甚至会引起谐振,关于电容焊盘以及电容位置的影响,我们下期文章介绍。