摘要

本设计是基于Altera公司的Cyclone II系列EP2C8Q208C8N芯片的双路低频信号发生器。系统应用FPGA内部特有的可配置IP核和锁相环等设计信号发生器。整个系统由触摸屏人机操控界面、红外操控、信号发生器、叠加电路组成。信号发生器可输出两路相互独立的信号,信号类型有矩形波、三角波以及正弦波。两路信号的频率、幅值、相位、占空比等参数都可通过红外遥控以及触摸屏调节和预置。频率的预置范围为1000赫兹到2000赫兹,步进值为1赫兹。幅值的预置范围为0V~5V,相位的预置范围为0°~360°,占空比预置范围为0~100%,且步进值都小于1。当两路波形都为正弦信号时,可以通过叠加电路对两路正弦信号进行叠加。

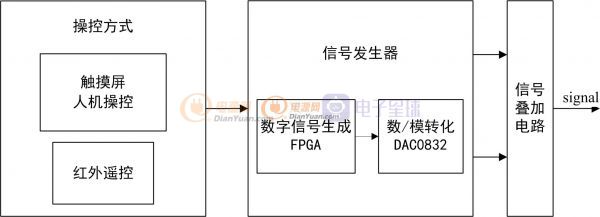

系统结构框

本设计是以Altera公司的可编程芯片做载体,运用Verilog作为软件设计工具,从而实现DDS原理,即信号发生器的核心思想。再加上信号发生器的硬件电路就可以输出特定的信号,也就是本设计中的数/模转换电路。从电池兼容EMC考虑,该电路的布局要紧凑的硬件,使导线长度尽可能短。这样即可以避免内部自身线路时间的干扰,也可以避免外界的干扰,适当增加滤波器来屏蔽干扰。这样就可以提高输出信号的质量。所有信号的参数可以通过两种方式程控调节,即人机操控方式和红外遥控方式。从图中可以看出系统主要由触摸屏人机操控界面、红外操控、信号发生器、叠加电路等组成。

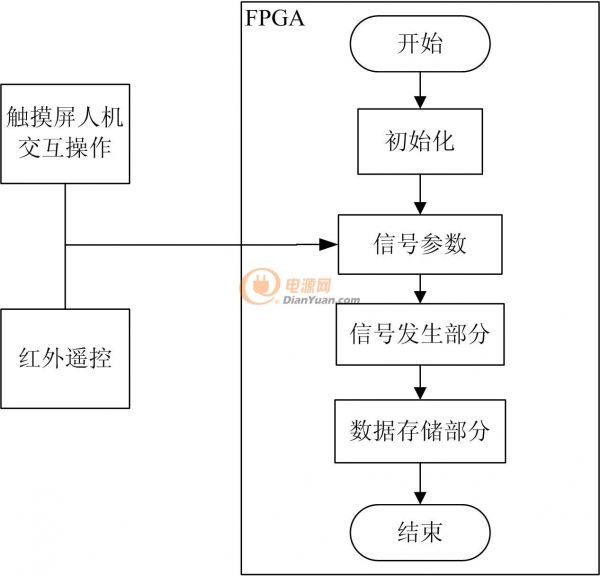

软件设计

软件设计包括三个部分,控制部分、信号发生部分、数据存储部分。FPGA的具体程序是采用顶层原理图分块编程的方式。控制部分实现触摸屏和红外遥控对信号参数设置的功能,信号发生部分产生三种信号,正弦波、方波、三角波,数据存储部分存储三种信号的波形数据。

FPGA软件设计采用顶层原理图模式,正弦波、三角波、矩形波信号发生器的顶层模块原理图,块内是用Verilog语言编写的程序。

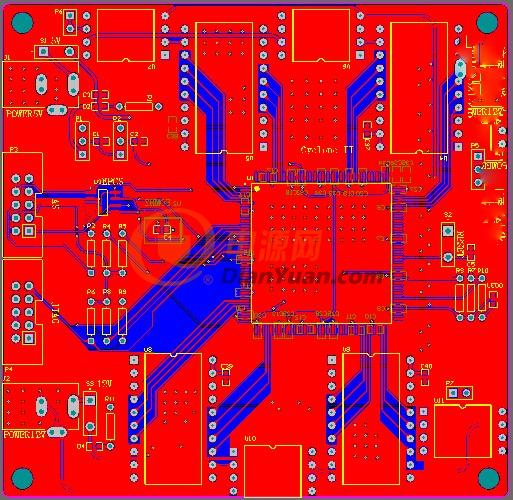

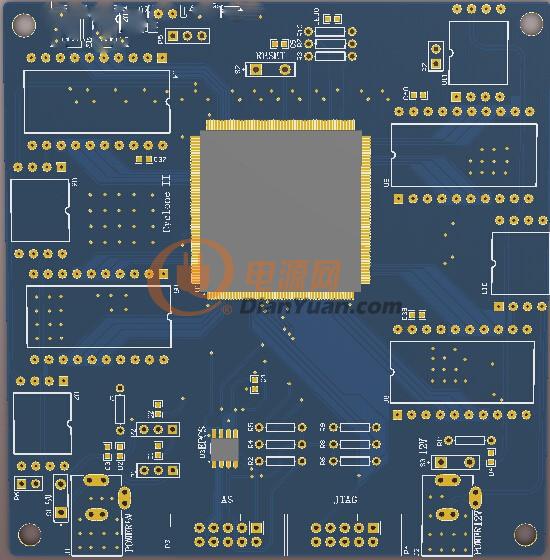

系统电路图

这是我大学期间第一次将所做的设计做出PCB,并且真正打样焊接出来,这个过程让我明白设计文件和打样出的实物的区别,需要注意的点。大家能看出来我这次PCB上有哪些错误吗?请留言哦。

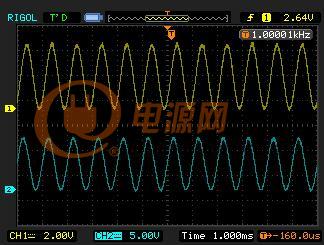

实测输出波形

输出两路独立的方波、正弦波、三角波。

有需要资料,或者交流的,请留言哦