电容的作用

全部回复(12)

正序查看

倒序查看

现在还没有回复呢,说说你的想法

@11455355

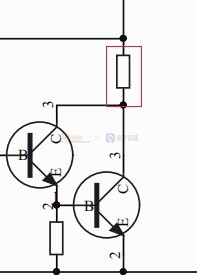

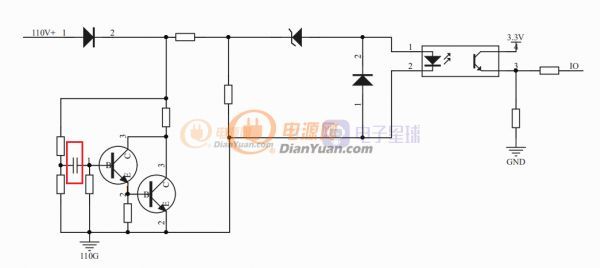

像是软启动或者芯片复位电路,110V上电,C初始充电电流大,使得两个三极管正偏导通,光耦发射端被短路,光耦得不到触发电流,IO端低电平无输出,当C充电到接近饱和程度,充电电流下降,三极管转入负偏截止,光耦发射端有电流通过,IO端高电平输出。C和周边电阻以及两只NPN三极管形成延时电路,延时开,通过光耦隔离输出,具体延时时间常数,由C的容量和周边电阻的阻值决定。这个电路典型特点是IO输出高电平比110V上电晚,符合软启动电路和芯片复位电路基本特征。

意思就是电容充电的过程中有电流流过?两个三极管就会相应的导通?当电容充满电之后,电容右端的电压变低,所以三极管就截止了。

0

回复

提示

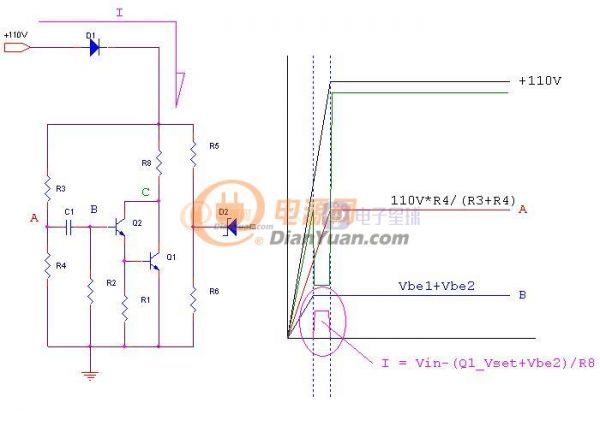

上圖示我幫你畫出的時序圖, 你看一下你的 KeyPoint 為何, 因為我也不知道你這作啥用

圖示, 當+110V電壓加入後,

1). R3開始對C1充電, A 點電壓最高為+110V*R4 / (R4+R3)

2). 當B 點的C1開始充電達到(Q1_Vbe+Q2_Vbe) 則達靈頓電路即啟動, 而為何使用達靈頓, 應該是要讓Q1瞬間飽和, 不要有線性區

3). 當Q1飽和後, C 點飽和電壓為(Q1_Vset+Q2_Vbe) , 所以會有電流從R8流過, 電流 I = +110V-(Q1_Vset+Q2_Vbe) / R8

4). B 點電壓被箝位在(Q1_Vbe+Q2_Vbe), 但 A 點電壓還在上升, 因此還有電流往 B 點流 , Q1 , Q2 會保持導通, 直到 A 點電壓不再上升 即

+110V*R4 / (R4+R3) = VC1 + (Q1_Vbe+Q2_Vbe)

C1則變成斷路, 當 B 點不再提供電流, Q1, Q2 隨即截止

5). 當Q1,Q2 截止後, I = 0

====================================

這唯一變化為電流, 如果+110V Source 端有電流偵測, 那只要再Source 端監測, 則可以確保負載是接上的....可能吧..我猜.......

1

回复

提示

@juntion

[图片]上圖示我幫你畫出的時序圖,你看一下你的KeyPoint為何,因為我也不知道你這作啥用圖示,當+110V電壓加入後, 1).R3開始對C1充電,A點電壓最高為+110V*R4/(R4+R3)2).當B點的C1開始充電達到(Q1_Vbe+Q2_Vbe)則達靈頓電路即啟動,而為何使用達靈頓,應該是要讓Q1瞬間飽和,不要有線性區3).當Q1飽和後,C點飽和電壓為(Q1_Vset+Q2_Vbe),所以會有電流從R8流過,電流I=+110V-(Q1_Vset+Q2_Vbe)/R84).B點電壓被箝位在(Q1_Vbe+Q2_Vbe),但A點電壓還在上升,因此還有電流往B點流,Q1,Q2會保持導通,直到A點電壓不再上升 即 +110V*R4/(R4+R3)=VC1+ (Q1_Vbe+Q2_Vbe) C1則變成斷路, 當B點不再提供電流,Q1,Q2隨即截止5).當Q1,Q2截止後,I=0====================================這唯一變化為電流,如果+110VSource端有電流偵測,那只要再Source端監測,則可以確保負載是接上的....可能吧..我猜.......

斑竹好用心,这时序图简单明了解释的很清楚。就是这电路确实不知道有啥作用。

0

回复

提示

@juntion

[图片]上圖示我幫你畫出的時序圖,你看一下你的KeyPoint為何,因為我也不知道你這作啥用圖示,當+110V電壓加入後, 1).R3開始對C1充電,A點電壓最高為+110V*R4/(R4+R3)2).當B點的C1開始充電達到(Q1_Vbe+Q2_Vbe)則達靈頓電路即啟動,而為何使用達靈頓,應該是要讓Q1瞬間飽和,不要有線性區3).當Q1飽和後,C點飽和電壓為(Q1_Vset+Q2_Vbe),所以會有電流從R8流過,電流I=+110V-(Q1_Vset+Q2_Vbe)/R84).B點電壓被箝位在(Q1_Vbe+Q2_Vbe),但A點電壓還在上升,因此還有電流往B點流,Q1,Q2會保持導通,直到A點電壓不再上升 即 +110V*R4/(R4+R3)=VC1+ (Q1_Vbe+Q2_Vbe) C1則變成斷路, 當B點不再提供電流,Q1,Q2隨即截止5).當Q1,Q2截止後,I=0====================================這唯一變化為電流,如果+110VSource端有電流偵測,那只要再Source端監測,則可以確保負載是接上的....可能吧..我猜.......

学习了,感谢。这个电路就是起一个上电瞬间增大输入采集电流的功能。

0

回复

提示