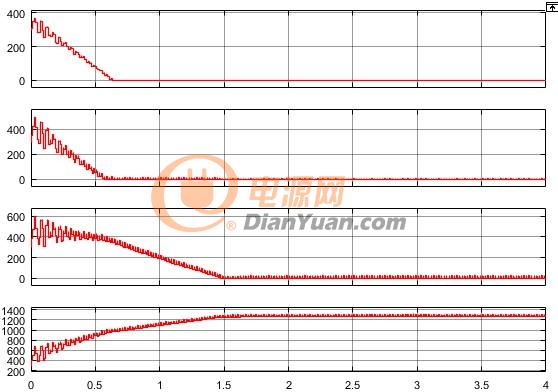

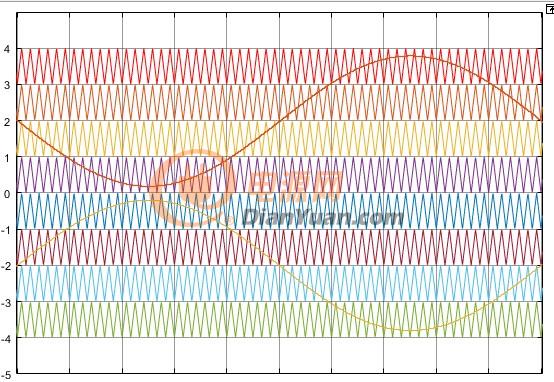

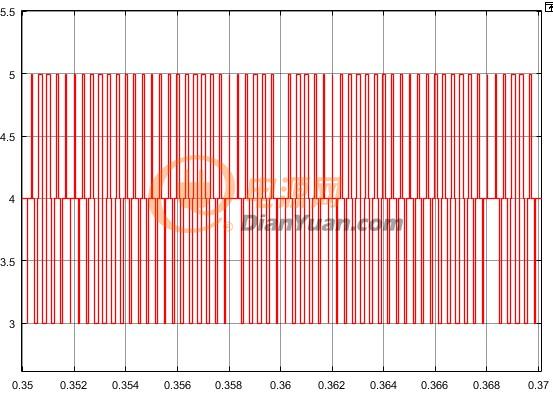

如图1为载波层叠A相上桥臂模块电压波形,根据波形可以看出模块电压发散,此问题由于模块未均压所致,须加入均压模块。以PD调制方式为例,上下桥臂各个模块的载波频率和相位相同,分别与调制波做对比,其中载波频率为3KHz,载波比为mf =fc / fr=3000/50=60,调制度ma=Ar / NAc =1.8×2/(4×1)=0.9。当调制波大于载波,输出1,否则输出0。上桥臂输出1的个数为上桥臂导通模块的个数,下桥臂输出1的个数为下桥臂导通的模块个数,设上桥臂导通的个数为Nup,下桥臂导通的个数为Ndown。图3为A相导通的模块总数,有图可知PD调制方式每相导通模块数不恒为N,N为一个桥臂的模块个数。

图1 未均压时A相上桥臂模块电压

图2 A相PD调制

图3 A相导通模块个数

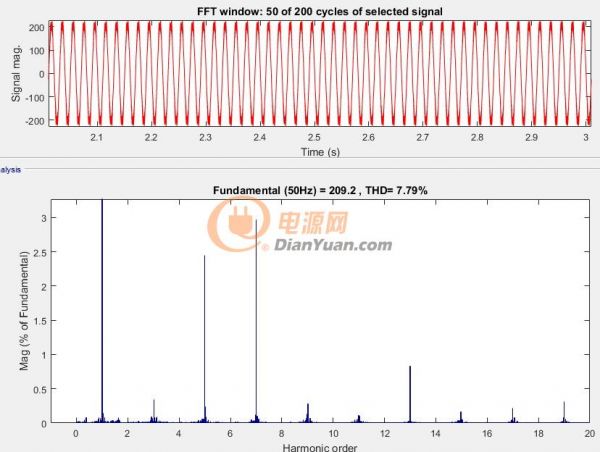

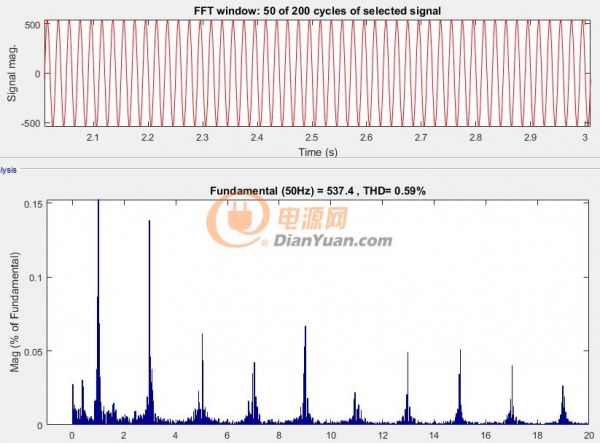

图4 未均压时A相的谐波分析

图5 均压后A相的谐波分析

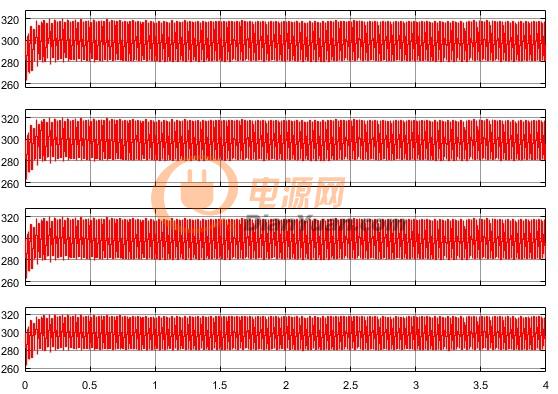

图6为均压后的A相上桥臂模块电压波形,均压后模块电压达到了稳定,在300V上下波动。

图6 均压后A相上桥臂模块电压波形

2.2 DSP实验

2.2.1 开环PWM波设置

系统时钟(SYSCLKOUT)的预定标处理将得到时间基准时钟(TBCLK)。实验板上晶振为30MHz,经过十倍频后在进行二分频得到75MHz时间基准时钟。

#define epwm_TBCLK 75e6

//TBCLK在此设置为75MHz;

//因为TECLK=SYSCLKOUT/(HSPCLKDIV*CLKDIV)=150M/(1*2)

由下条语句设置PWM波频率,由此计算出比较器A的值。其中可由PWM_CLK可以直接设置PWM波频率。

#define PWM_CLK 5e3 // If diff freq. desired, change freq here.

#define SP epwm_TBCLK/(PWM_CLK*2)

#define number (PWM_CLK/50)

float d1;

d1 = 2*3.1415926/(number);

fPhase=(fPhase + d1);

EPwm1Regs.CMPA.half.CMPA =(Uint16)(0.95*SP*(sin(fPhase)+1)/2);

2.2.2 死区设置

要设置延时时间为2us,则将DB为150。

#define DB 150 //75个点是1us ; 75/75e3

EPwm1Regs.DBRED =DB; //死区上升延时寄存器

EPwm1Regs.DBFED =DB;

3遇到的问题及解决方法

- (1) 问题:开关电源无法输出24V电压?

解决方法:用万用表测量电压,发现接线错误,错误接线如下。要输出24V电压,须将-V3接地,+V3接正极。

图7 错误接线

- (2) 问题:驱动输入端为PWM波,输出端却输出方波?

图8 驱动输出端输出波形