电源分配网络(PDN)设计

本期和大家分享讨论电源分配网络PDN设计思想,以下主要内容源自Intel资料,个人认为这个设计思路很清晰,适合初学者入门,所以将这些资料进行整理分享,后续会继续分享实战仿真经验。

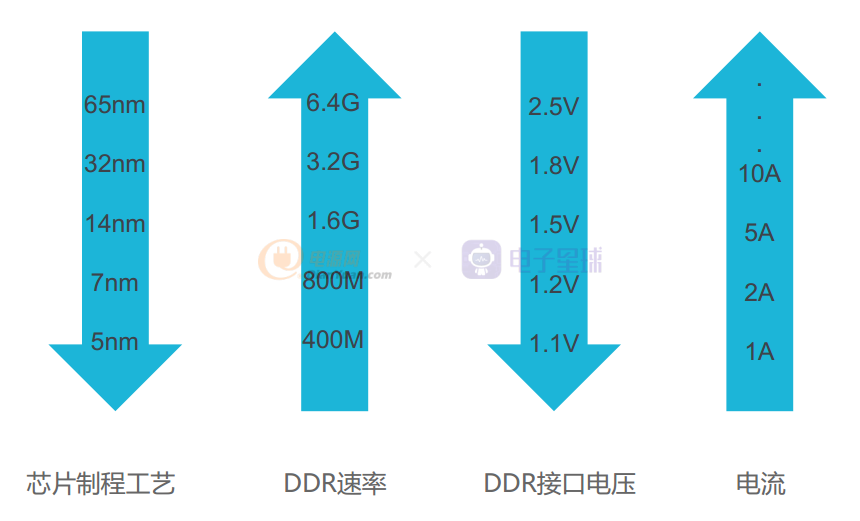

电源设计的趋势和挑战

芯片工作电压越来越低,电源对电压的Tolerace一般是5%或3%,甚至1%,因此 纹波动态15mv甚至10mv的电源要求,对测试和设计都提出了很高的挑战 。

纹波噪声来源:

芯片工作时,稳压电源模块VRM通过感知其输出电压的变化,调整其输出电流,从而把输出电压调整回额定输出值。

无法实时响应芯片对于电流需求的快速变化,电源电压发生跌落,从而产生电源噪声 。

当前芯片工作速度越来越快,高频瞬态电流越来越大,带来得噪声越来越不能被忽视 。

目标阻抗:满足负载最大瞬态电流变化,且电压波动范围在芯片允许范围内,PDN自身阻抗允许的最大值,超过这一阻抗值,则电源波动有可能超过电压允许范围。目标阻抗设计方法是一种保守的设计方法。

目标阻抗去耦合方法

·确定PCB去耦合机制的一种有效的策略是使用频域目标阻抗方法(FDTIM)。Altera PDN去耦合计算器工具使用了这一方法,也是使用Altera FPGA时确定电路板级去耦合需求所推荐的方法。

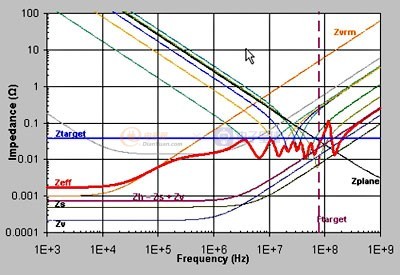

FDTIM去耦合概念

·FDTIM方法的关键概念是为要考虑的电源轨确定目标阻抗(ZTARGET)。从几个KHz,直至所要求的最大频率(fTARGET),可靠的去耦合策略保证了实际电源轨阻抗(ZEFF)比ZTARGET低。图1显示了这一概念,水平蓝色实线是ZTARGET,垂直棕色点线是fTARGET。对于红色实线ZEFF,使用了各种去耦合和体电容,这样,从DC直至fTARGET,其阻抗一直比ZTARGET低。采用这一设计,从DC直至去耦合目标频率都保持了电源完整性。

使用FDTIM设计可靠的去耦合机制时,请进行以下计算:

确定ZTARGET

计算电源轨的ZTARGET时,您应该知道以下信息:

- 系统中所有器件的最大瞬变电流要求,这些器件是由待考虑的电源轨供电的。您可以从相应器件的制造商那里获得这些信息。注意:Altera提供PowerPlay早期功耗估算器(EPE)工具,来估算其所有FPGA和CPLD的功耗。

- 电源轨允许的最大AC波纹只是供电电压的百分之一。您可以从待考虑的电源轨供电的器件电源容限规范中获得这些信息。

如果有这些信息,那么,可以按照下面来计算ZTARGET:

- ZTARGET= [VoltageRail (%Ripple/100)/MaxTransientCurrent]

例如,对于允许5%的AC波纹的1.1-v电源轨,希望最大瞬变电流是1.5 A,要对这样的电源轨可靠的去耦合,那么,目标阻抗是:

- ZTARGET= [(1.1)(0.05)/1.5]=36.7mΩ

确定fTARGET

所需要的最大频率是指,增加了一定数量的去耦合电容后,不会使得电源轨阻抗(ZEFF)低于目标阻抗(ZTARGET)时的频率点,这是因为杂散平面的主要阻抗是扩散电感以及封装的贴装电感。一般而言,这一fTARGET范围是从50/60 MHz直至150/200 MHz。在这些频率之外,是由所选目标器件的封装和管芯电容来维持电源完整性的。

选择去耦合CAPS以满足ZTARGET

在所要求的整个频率范围内,为保持电源完整性,电源分配系统采用了电压调节器模组(VRM)、板上分立去耦合电容,以及平面间电容(来自电路板堆叠的电源地夹层电容)。对于上面的例子,设计人员必须进行合适的选择,这样,在整个所要求的频率范围内,有效阻抗保持低于36.7mΩ。

- 平面电容对于高频,使用分立电容进行去耦合的效率不高。对于这些频率,使用电源平面电容对噪声去耦合。如图1所示,您可以看一下标准的并联平行极板电容,理解平面电容的概念。

图1.并联平面电容

当电源平面与地平面接近时,会出现电场。图1中上面的区域显示了电源岛,即电源平面,下面的区域显示了地平面,箭头表示电场电力线。这一电场提高了电容,由下面的公式表示其大小:

- C=(εοεrA)/h

其中:

- εο= 自由空间的介电常数

- εr= 所使用电介质的相对介电常数

- A= 重叠区域

- h= 单独的平面电源岛的两侧如果都有地平面,那么,需要计算每一侧的电容,加起来以确定总电容。平面电容是高频时去耦合的主要方法,因此,这是所有高速设计都要采用的。在高频,分立电容的作用并不明显。例如,考虑下面。实例:确定FR-4绝缘材料叠层(εr= 4.5)1平方英寸面积的并联平行极板电容,隔开了4 mils。解决方案:

- h= 4mils = 1.016 * 10-4 m

- εο= 自由空间的介电常数 = 8.85 * 10-12F/m

- A= 1平方英寸 = 6.4516 * 10-4m2

- εr= 4.5把这些数值应用到上面的电容公式中,得到C = 253 pF。因此,典型FR-4电路板叠层间隔4 mils,每平方英寸的电容大约是253 pF。数值与间隔距离成线性反比,与面积成线性正比。Altera在多种电路板上成功应用了平面电容。

- 减小杂散电感电源分配系统(PDS)的目的是为每一器件的电源和地焊盘提供并维持所要求的目标恒定电压。为能够高效的实现这一目标,PDS采用了电压调节器模组(VRM)、体电容和去耦合电容(Decaps),以及电源和地平面夹层结构(平面电容)。在各种瞬变的负载条件下,这些元器件能否有效的帮助维持恒定电压主要取决于它们相关的杂散电感。

VRM

作为一阶近似,VRM可以简单的建模为串联的电阻和电感,如图1所示。

图1. VRM的串联阻抗模型

在几十个KHz的低频范围内,VRM主要是电阻,具有极低的阻抗,因此,在低频时能够满足瞬时电流要求。但是,超出几十KHz之后,VRM阻抗主要是电感,无法再满足瞬变电流要求。您可以从VRM制造商那里得到VRM的ESR和ESL值,为获得最佳瞬变性能,选择较低的ESR/ESL调节器。

Decaps

板上分立去耦合电容必须能够满足从几十KHz到几百MHz (最大)的低阻抗要求,这取决于电容ESR和ESL,以及电路板贴装和扩散杂散电感。即使选择了具有极低ESR和ESL规范的去耦合电容,由于杂散贴装和扩散电感会限制这些电容的作用,因此,仅有这些电容还不够。由此,设计高效的PDS时,必须仔细的减小与电路板设计相关的各种杂散电感。

贴装电感

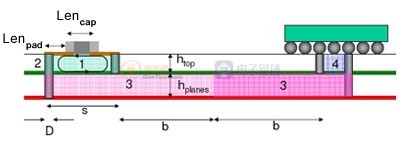

贴装电感是指在PCB上贴装了电容后带来的相关串联电感。这一杂散电感增加了电容供应商公开的ESL值。可以通过选择较小的电容封装,对PCB上的电容进行适当的布板,减小贴装电感。图2显示了与PCB平面和BGA器件相关的贴装去耦合电容的横截面。

图2. 去耦合电容贴装

使用下面的公式来估算贴装电感:

- Lmnt = Ltrace + Lvia

其中,

- Ltrace =128*[(2xLenpad)+Lencap]*(htop/w) pH

以及

- Lvia =10*htop*ln(2s/D) ph

其中,

- Lenpad= 电容焊盘长度加上从焊盘到过孔的走线长度(mils)

- Lencap= 电容长度(mils)

- w= 电容焊盘和过孔之间走线的宽度(mils)

- htop= 顶层和最近的电源/地平面之间的距离(mils)

- s= 电容电源过孔中心和地过孔中心之间的距离(mils)

- D= 过孔外层直径(mils)

- hplanes= 电源和地平面之间的距离 (mils)

- b= 电容和封装电源/地过孔之间距离的一半(mils)

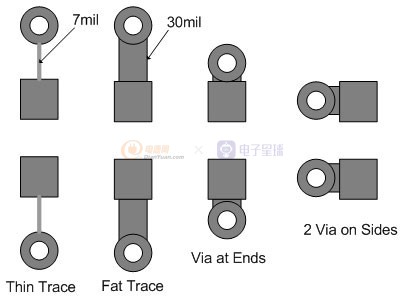

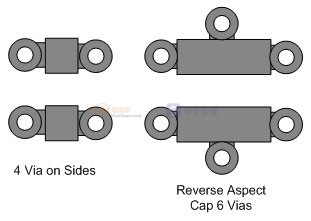

一般而言,为减小贴装电感,应保持电容电源和地过孔尽可能靠近相应的焊盘,使用宽连接走线和较大的过孔直径。电源和地平面对应靠近安装了电容的表面,以减小过孔电感的影响。此外,把过孔放在电容的同一侧(侧面过孔配置),而不是电容末端的对端(末端过孔配置),减小了电流环路面积,减少了穿过环路的磁通量,从而减小了电感。图3显示了各种电容布板拓扑,而表1对比了大小不同的电容各种电容布板类型的贴装电感。

图3.各种电容布板拓扑

图4.产生较低贴装电感的过孔布局类型

扩散电感

扩散电感是电源地平面对,以及从去耦合电容到目标BGA器件电源地球角之间的距离所围成的环路面积构成的电感。结果,这一电感与电源地夹层构成的平面间电容电感直接相关。下面的平面间电容部分详细解释了这一电感。

平面间电容

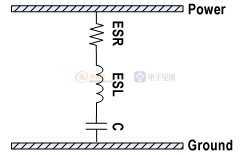

作为一阶分析,可以把PCB电源地平面对简单的建模为串联的电阻、电感和电容,如图5所示。注意,这一简单的模型忽略了趋肤效应和介质吸收等频率相关效应。

图5.电源地平面夹层简化的阻抗模型

图5中的ESL一阶公式如下所示:

- ESL = (μ0•h•l)/w

其中,

- μ0= 自由空间的磁导率(32 pH/mil)

- h= 电源和地平面之间的距离,以mils表示。

- l= 电源平面长度,以英寸表示。

- w= 电源平面宽度,以英寸表示。

您可以把电源地平面夹层的ESL解释为去耦合电容所看到的扩散电感,因为该电容为BGA器件提供电流。因此,从上面的ESL公式中,把去耦合电容尽可能靠近目标BGA器件放置,可以减小扩散电感(减小从电容到BGA器件的距离l)。此外,电源地夹层使用薄绝缘介质材料(减小h)和宽平面对(增大w),有助于减小去耦合电容看到的有效扩散电感。

结论

为能够成功的设计高效的PDS,应理解会影响PDS性能的各种杂散电感。本文档解释了在设计PDS时必须要考虑的三种杂散电感。讨论了VRM杂散电感、去耦合电容贴装电感,以及电源平面扩散电感,介绍了减小这些电感的方法。