本文内容旨在和大家讨论如何从datasheet中评估MOSFET等效电容,栅极电荷,栅极阈值电压,米勒平台电压,内部栅极电阻,最大Dv / Dt相关信息。我将会通过实例来分析,不足之处还望大家留言指正。

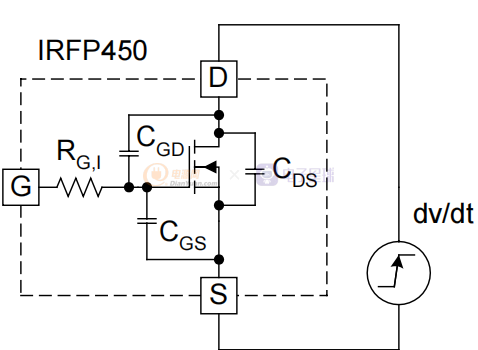

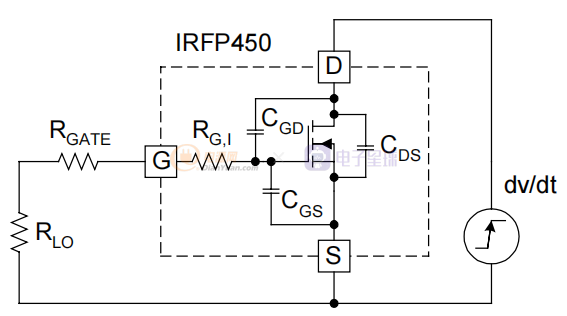

在此示例中,我们将要计算MOSFET的等效Cgs,Cgd和Cds电容,总栅极电荷,栅极阈值电压和Miller平台电压,近似内部栅极电阻以及IRFP450的dv / dt极限。 下图是地面参考栅极驱动应用中该MOS的示意图。

提供以下参数信息以进行必要的计算:

Vds,off=380V 器件的标称漏极-源极关断状态电压。

Id=5A 满载时最大漏极电流

Tj=100℃ 工作结温

Vdrv=13V 驱动电压

Rgate=5Ω 外部驱动电阻

Rlo=Rhi=5Ω 驱动电路的输出电阻

一、电容

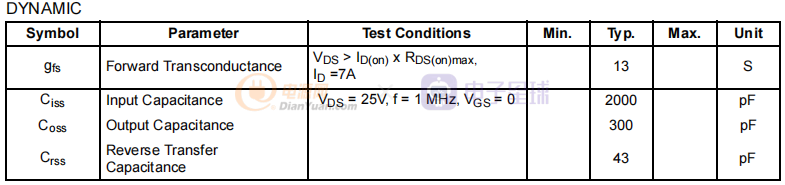

IRFP450的数据手册提供了以下电容值:

使用这些值作为基础,可以估算出实际应用的平均电容为:

等效值:

计算结果:

电容值可以从以下基本关系中获得:

Cgd=Crss,avg Cgd=22pF

Cgs=Ciss-Crss Cgs=2000pF-43pF=1957pF

Cds=Coss,avg-Crss,avg Cds=154pF-22pF=132pF

请注意,Cgs是根据原始数据表中的值计算得出的。 在一个方程式之内,值得注意的是使用在相同测试条件下测得的电容器值。 还请记住,Cgs是恒定的,它与电压无关。 另一方面,Cgd和Cds电容器具有很强的非线性和电压依赖性。 它们的最高值为0V或接近0V,并且随着栅极至漏极端子和漏极至源极端子两端电压的分别升高而迅速降低。

二、驱动充电

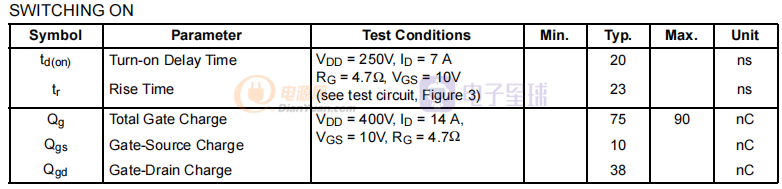

对于特定的栅极驱动幅度,漏极电流电平和漏极截止状态电压,最坏情况下的栅极电荷数在IRFP450数据手册中给出。

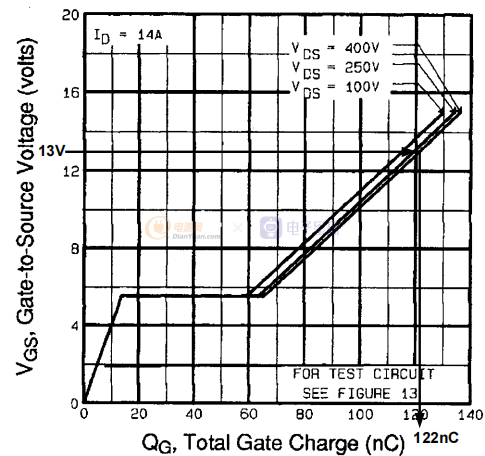

使用下图所示的典型“总栅极电荷”曲线可以很容易地校正不同的栅极驱动幅度。从左侧的13V栅极至源极电压开始,找到相应的漏极至源极电压曲线(如果未给出确切值,则进行内插),然后在水平轴上读取总栅极电荷值。如果需要更准确的值,则必须分别确定不同的栅极电荷成分。 栅极至源极电荷可以从左侧的曲线估算,只有正确的米勒高原水平必须已知。 可以从(一)中获得的Crss,avg值计算米勒电荷。 最后,过驱动电荷分量-将栅极-源极电压从Miller平台升高到最终幅度---应该再次从图中进行估算。

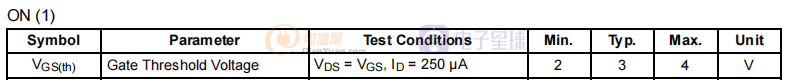

三、栅极阈值和米勒平台电压

正如已经在(二)中显示的那样,接下来要探讨几个MOSFET开关特性受栅极阈值和Miller平台电压的实际值影响。 为了计算Miller平台电压,一种可能性是使用数据手册中列出的MOSFET的栅极至源极阈值电压(VTH)和跨导(gfs)。

从表中看,阈值的定义不是很好,列出的gfs信号量很小。 获得实际VTH和Miller平台电压的更准确方法是使用数据手册的“典型传输特性”曲线。

从相同的温度曲线中,选择两个易于读取的点,并注意相应的漏极电流和栅极至源极电压。 选择漏极电流值以对应于图形的垂直网格线,这样就可以准确读取电流。 然后沿相交点到水平轴并读取栅极-源极电压。从漏极电流开始将获得更高的精度,因为栅极-源极电压与漏极电流的对数比例成线性比例 。 在线性范围内更容易估算Vgs1和Vgs2,因此潜在误差要小得多。

举个栗子:(150℃)

Id1=3A

Vgs1=4.13V

Id2=20A

Vgs2=5.67V

栅极阈值和米勒平台电压可以计算为:

Id1=K*(Vgs1-Vth)^2

Id2=K*(Vgs2-Vth)^2

这些值对应于150°C的结温,因为使用了“典型传输特性”中的150°C曲线。 由于阈值电压的温度系数很大,因此必须在此应用中针对100°C的工作结温校正结果。栅极阈值电压和Miller平台电压电平必须通过以下方式进行调整:

四、内部栅极电阻

另一个有趣的参数是内部栅极网格电阻(Rg,i),该参数未在数据手册中定义。 该电阻是连接设备中各个MOSFET晶体管单元的栅极的分布式电阻器网络的等效值。 因此,设备内的栅极信号分布看起来和行为与传输线非常相似。 这导致器件中各个MOSFET单元的开关时间不同,具体取决于驱动单元与栅极连接的焊盘之间的距离。

确定Rg,i的最可靠方法是使用阻抗桥进行测量。 该测量与实验室中常规执行的电容器的ESR测量相同。 为了进行此测量,MOSFET的源极和漏极端子短接在一起。 阻抗分析仪应设置为RS-CS或可用的RS-CS-LS等效电路,以产生等效栅极电阻Rg,i,MOSFET的输入电容,Ciss和晶体管的串联寄生电感的分量值设备,全部串联连接。

对于此示例,通过HP4194阻抗分析仪测量了IRFP450的等效分量值。 器件的内部栅极电阻确定为Rg,i =1.6Ω。 等效电感测得为12.9nH,输入电容为5.85nF。

五、dv/dt限制

MOSFET晶体管仅在其漏极-源极电压快速上升时才容易受到dv / dt感应的导通。 从根本上讲,导通是由流经器件栅极-漏极电容器并产生正栅极-源极电压的电流引起的。 当该电压的幅度超过器件的栅极至源极导通阈值时,MOSFET开始导通。 需要考虑三种不同的情况:首先,查看由CGD和CGS电容器形成的电容分压器。 根据这些电容值,可以将栅极至源极电压计算为:

如果VGS <VTH,则MOSFET保持截止状态。 为了确保这一点,最大漏极至源极电压可通过以下方式估算:

该机制提供了针对dv / dt在低压应用中引起的导通的全面保护,而不受内部栅极电阻和外部驱动阻抗的影响。

对于更高电压的应用,希望确定MOSFET的自然dv / dt极限。 该特性对应于在外部驱动器阻抗为零的理想情况下,器件在不导通的情况下可以承受的最大dv / dt。 这由示意图中的栅极-源极连接短路来表示。

由于CGD的充电电流,Rg,i两端的电压降会启动导通。因此,自然dv / dt极限可通过以下公式计算得出:

这个极限值对于评估设备对特定应用的适用性非常重要,在该应用中,电路的其他组件会强制关闭dv / dt。 这些应用包括同步整流器,谐振模式和软开关电源转换器。

第三次计算根据MOSFET器件的寄生元件和栅极驱动电路的特性描述了漏极-源极电压波形的dv / dt极限,为避免导通,栅极-源极电压 必须保持在开启阈值电压以下:

值得注意,MOSFET晶体管的阈值电压会随着温度发生显着变化,这一点很重要。 因此,必须考虑高结温的影响。 对于在100°C的工作结温下使用IRFP450型晶体管的特定示例,计算得出以下限制:

CASE1:在以下漏极/源极电压以下时,没有dv / dt引起的导通:

CASE2:IRFP450的dv / dt限制为:

CASE3:电路中的dv / dt限值包括驱动器输出阻抗的影响为: