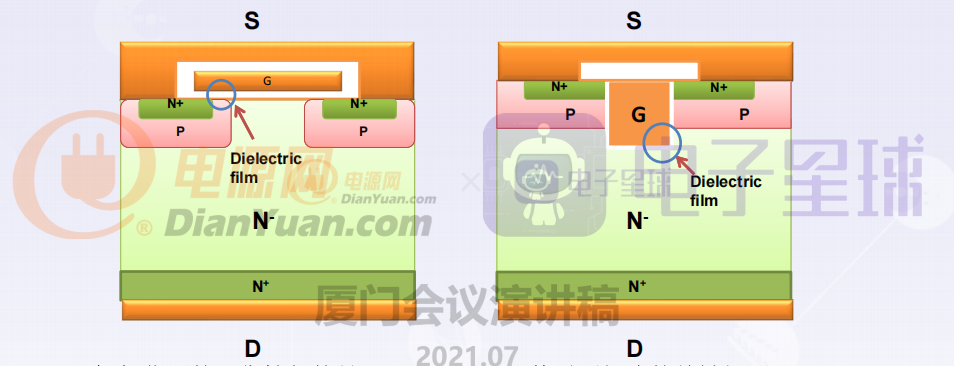

在电源网厦门线下会议上,厦门大学张峰老师对目前SiC MOSFET问题作出详细的叙述,首先是栅氧化层的可靠性仍然是SiC MOSFET器件需要解决的关键问题。

1. 阈值电压Vth随温度提高下降

2. 栅压非对称性(如-10V—25V)

3. DMOSFET器件沟道迁移率较低,通态电阻较高

4. UMOSFET器件可靠性亟需提高

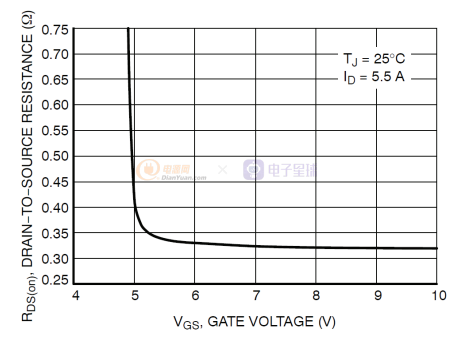

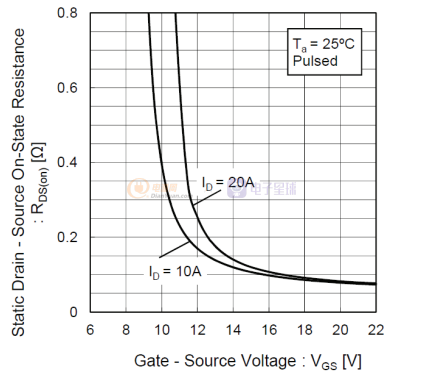

WBG 技术仍处于发展的早期阶段,在如何驱动 SiC 和 GaN FET 方面存在差异。 GaN FET 是横向器件,因此需要 5 到 6 V 的相对较低的最佳驱动电压。一些 GaN 器件使用 GaN 结场效应晶体管 (JFET) 与硅 FET 的共源共栅组合; 它们的驱动技术类似于驱动硅 FET。 SiC FET 通常需要 20 V 才能开启,需要负 –5V 才能关闭,以防止在高电压和高电流下切换时由于接地弹跳而意外开启。 最近的趋势是将 SiC FET 的驱动电压降低几伏。 图 1 显示了各种 WBG FET 的 RDSON 对 Vgs 的依赖性,以说明最佳驱动电压的主要差异。

GaN 共源共栅 12-V 驱动 (a)

GaN 共源共栅 12-V 驱动 (a)

SiC 20/-5-V 最佳驱动 (b)

SiC 20/-5-V 最佳驱动 (b)

图6 GaN 5V 最佳驱动 (c)

图6 GaN 5V 最佳驱动 (c)

在印刷电路板 (PCB) 上快速开关分立 WBG 器件的布局具有挑战性。 一种方法是在同一封装中集成和优化驱动电路和功率器件。 这种方法减少了封装和布局寄生效应,并优化了功率级以获得最佳性能,包括保护和诊断功能。 系统中此类模块的布局要容易得多,但缺点是设计灵活性有所降低。

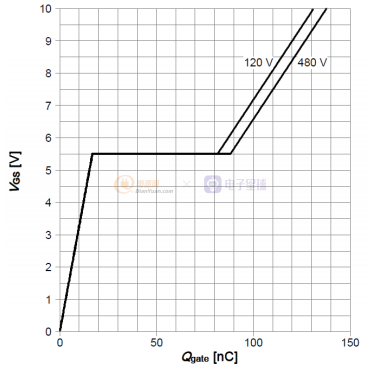

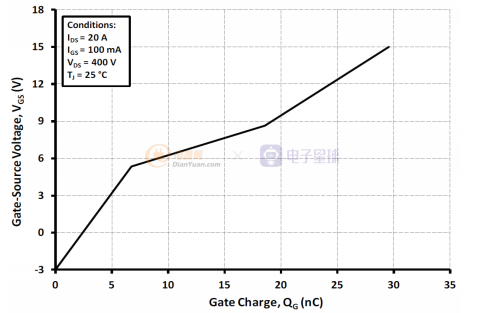

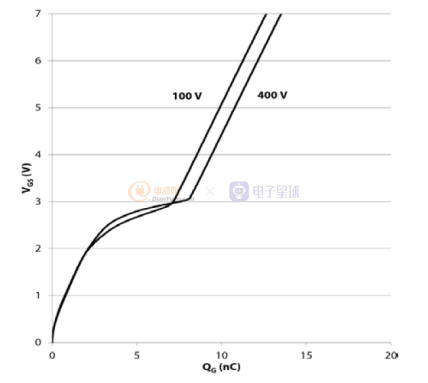

与硅相比,WBG 器件的特定 RDSON 更低意味着您需要更小的芯片尺寸和更低的栅极电荷来驱动 FET。 图 2显示了类似 RDSON 和额定电压器件的 Vgs 与 Qgs 的示例,比较了最佳驱动所需的电荷。

(a)

(b)

(c)

图2 各种 FET 技术的栅源电压过充电:硅、超级 JFET (a); 碳化硅场效应管 (b); GaN FET (c)。

额定电压为 650 V 和 67-mΩ RDSON 的硅超级结 FET 在 10 V 时需要 138-nC 驱动充电,而 900-V、65-mΩ SiC FET 在 15 V 和 650-V 时仅需要 30-nC , 55-mΩ GaN 在 6 V 时仅需要 5.8 nC。这意味着在与硅 FET 相同的频率下运行时,GaN 和 SiC 的驱动功率显着降低,或者可以提高 WBG 器件相对于硅的开关频率,同时仍然 保持相对较低的驱动损耗。

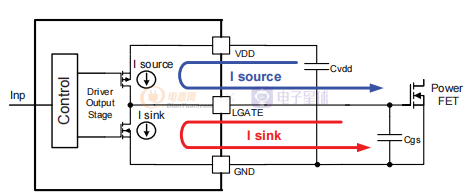

对于快速开关 WBG 功率器件,驱动回路封装和布局寄生效应的影响变得显着。 驱动器 IC 数据表通常指定在 DC 或大电容负载条件下测量的源输出电流和吸收输出电流。 这种电流没有考虑到快速开关期间寄生效应的影响。 根据数据表假设驱动器提供 4A 拉电流和 8A 灌电流。 图 3显示了这样的驱动电路。

图3 驱动电路额定为 4A 拉电流和 8A 灌电流

分别计算 Vgs 上升和下降时间:

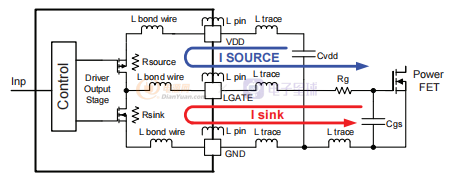

简单计算,假设 GaN 栅源电容 Cgs 典型值为 1nF,则上升时间为 2 ns,下降时间为 1 ns。 从实际设计的角度来看,这似乎并不现实。 更详细的分析将考虑布局和封装寄生电感,如图 4 所示。

图 4 驱动电路,包括封装和布局寄生电感

图 5 显示了驱动电压和电流的相关仿真波形。

图5 模拟驱动电压和电流,包括寄生效应

带有寄生电感的驱动电路的波形显示灌电流从 8 A 降低到 4.6 A。栅极电流和栅极源电压波形具有明显的振铃,Vgs 具有 1V 过冲和 –3V 下冲 . 关闭期间超过器件开启阈值的过冲可能会导致虚假开启和系统故障。 导通 FET 也会引起类似的振铃和由电感寄生引起的源极电流降低。

封装和布局寄生效应的另一个影响与开关期间漏源电压的高压摆率 dV/dt 相关。 外部和内部栅极电阻以及驱动器 IC 的大输出阻抗使 dV/dt 问题变得更糟。

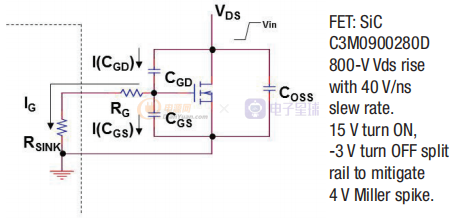

图6显示了一个简化示意图,用于说明问题和相关的测量波形。

图6 Vds 电压的高 dV/dt 导致 Vgs 电压处的噪声尖峰

在 FET 以高 dV/dt 关闭期间,Cgd 电容的大量充电电流会导致 Rsink 和 Rg 处出现电压尖峰。 该电压尖峰可能会将 Vgs 提升到 FET 的开启阈值之上。 这种效应称为米勒尖峰,可能会导致 FET 虚假开启。 图 6中的波形(40V/ns dV/dt 导致 4V 尖峰)说明了这种情况。 存在多种缓解此问题的方法,包括在关闭期间使用负偏压,或使用分离输出驱动器或采用额外米勒钳位电路的驱动器。 该钳位电路包括一个直接连接到栅极的附加开关,以便在米勒尖峰变得过高时将其下拉。

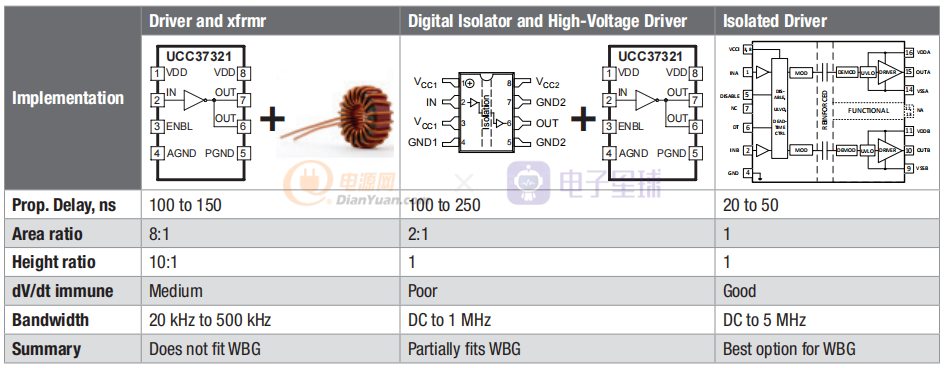

在许多情况下,您必须隔离功率器件的驱动信号。 隔离的原因包括安全性、电平转换和改进的抗噪性。 因此,相关绝缘被评为增强型、基本型或功能型。 表 1列出了一些可能的隔离解决方案及其优缺点。

表1各种驱动器隔离技术的比较

使用非隔离驱动器 IC 和栅极变压器的传统方法体积庞大,并且在频率和占空比范围方面受到限制。 结合数字隔离器和高压驱动器 IC 可提供紧凑、宽带宽的解决方案,但传播延迟和 dV/dt 抗扰度并不总是满足 WBG 器件的要求。 最近,完全隔离的驱动器 IC 已经面世,包括加强绝缘水平。 这些驱动器最适合快速 WBG FET,因为它们适应较宽的频率范围并且没有占空比限制,以及较短的传播延迟和较高的指定 dV/dt 抗扰度。

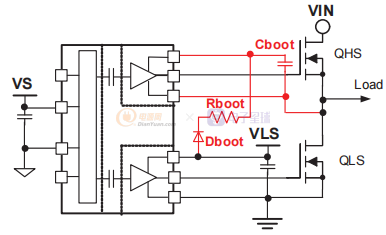

使用体栅极变压器驱动 FET 有许多缺点,但这种方法不需要额外的偏置电源。 高压隔离驱动器 IC 在驱动器侧需要一个偏置电源,该偏置电源能够在轨到轨的高频共模脉冲下可靠运行。 两种主要方法是基于自举二极管(图 7)或隔离偏置电源(图 8)。

图7 基于自举二极管的偏置电源

图 8 包括驱动器 IC 和隔离偏置电源

基于自举二极管的方法看起来很简单,但有许多缺点可能会限制其与 WBG FET 的使用:

• 二极管必须具有低 Qrr。

• 当总线电压等于或高于 600 V 时,可能需要 SiC 或 GaN 二极管。

• 偏置电压不精确。

• 需要定期对Cboot 电容器进行充电。

• 不能用于多级拓扑,如图 8 所示。

• 受 dV/dt 限制。

隔离式偏置电源通常更昂贵,但提供的好处抵消了许多应用中的成本。 优点包括:

• 始终可用。

• 可用于任何拓扑。

• 稳定、准确的偏置电压。

• 低电容Ciso 通过隔离提供高dV/dt 抗扰度。

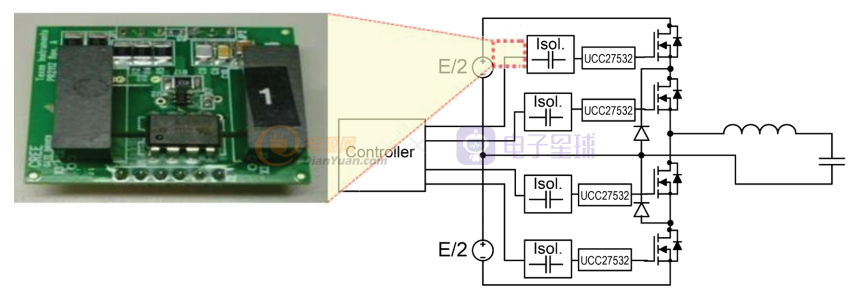

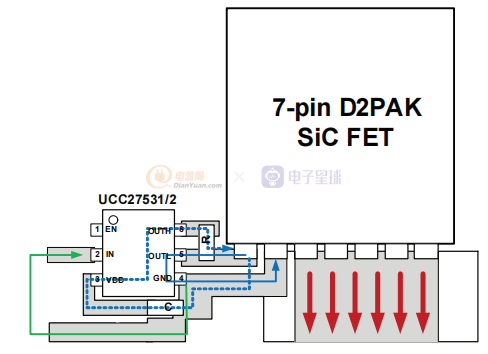

图 9 中显示的示例说明了以下布局和最佳驱动规则,以获得最佳 WBG FET 开关性能。 这些规则对于快速切换 WBG 设备尤其重要。

• 将驱动器放在 FET 旁边。

• 分离噪声接地,如图 9 所示。

• 将去耦电容放置在靠近 VDD 和 GND 的位置。

• 使用分离输出驱动器来优化开启/关闭。

• 使用分离轨减轻米勒导通。

• 选择低寄生元件。

• 尽量减少高 di/dt 环路。

• 尽量减少高 dv/dt 区域。

• 尽可能使用宽走线。

• 使用模拟器提取寄生参数。

图9WBG 功率 FET 的最佳布局示例

以上是我从电源网会议中学到的东西,会议上大佬都是会只讲要点和重点,基本的知识还是需要在会后自己补充。