GaN 正在实现更高的功率密度和更高效率的电源转换器。与 Si MOSFET 相比,GaN 提供更快的开关速度、更小的输出电荷和更低的开关损耗。与 MOSFET 不同,GaN FET 的横向结构内没有 p-n 结,也没有体二极管,也没有反向恢复电荷 (Qrr)。通过消除反向恢复损耗,GaN 可在硬开关拓扑中实现高效的高开关频率操作。例如,在连续导通模式 (CCM) 下的无桥图腾柱功率因数校正 (PFC) 中,使用超级结 MOSFET 是不切实际的,因为它们具有很高的反向恢复损耗。如图1所示,通过使用GaN FET作为高频开关,反向恢复损耗完全消除,开关相关损耗显着降低。交流驱动器的逆变器是另一种有益的拓扑结构,其低开关损耗和无反向恢复损耗可缩小紧凑型伺服驱动器和集成电机驱动器中的散热器尺寸。

图1 使用 GaN 作为高频开关和 Si MOSFET 作为整流器的无桥图腾柱 PFC

当电流通过体二极管或沟道从源极流向漏极端时,功率 MOSFET 将进入第三象限操作。 尽管 GaN FET 没有体二极管,但该器件的对称性有助于在第三象限中以类似二极管的行为进行传导。 与 Si MOSFET 的情况类似,建议不要在 GaN FET 上添加反并联二极管来传导反向电流。 添加一个反并联二极管会增加开关节点的输出电容并增加开关损耗。 相反,可以通过优化死区时间来最小化第三象限损耗。

一、GaN FET 的反向恢复

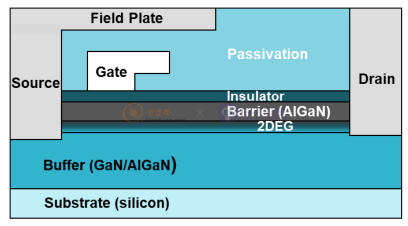

横向 GaN 结构由通过二维电子气 (2DEG) 通道连接的源极和漏极组成。 栅极电压控制沟道的导电性。 图 2 显示了横向 GaN 结构的简化横截面,说明了源极和漏极之间沟道区的对称性。 在第三象限操作中,漏极和源极切换位置。 漏极电位低于开启 GaN 器件的栅极,并允许在没有体二极管的情况下反向传导。

图2 GaN FET 横向结构的横截面

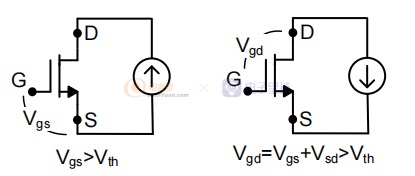

导通沟道(漏极到源极)的条件是栅源电压 Vgs 高于阈值电压 Vth,如图 3 所示。 通道打开时,Vds 可以使用公式计算。

图3 在正向和反向传导中打开通道的条件

Vds= IdsRon

Ron 是第一象限中通道的导通电阻。

当 Vgs 小于 Vth 时,电流不能在第一象限传导,但可以在第三象限流动。当电流反向流动(第三象限)时,漏极和源极端子可以交换终端。导通沟道反向导通的条件是栅漏电压 Vgd 高于阈值电压 Vth。像二极管一样,GaN FET中的沟道自换向,Vsd自偏置,使Vgd达到Vth,沟道传导反向电流。在此操作下,Vsd由Vth-Vgs偏置并随着反向电流Isd增加如公式 2 所示。在等式中,Ron_reverse,当器件工作在饱和区时,第三象限中具有关断栅极的等效导通电阻取决于 Isd。建议参考数据表中的 IV 曲线来估计第三象限中的 Vsd。当栅极在反向传导期间导通时,Vgd 等于 (Vgs + Vsd),高于 Vth,使沟道完全导通,导通电阻与第一象限中的 Ron 相同。

Vsd ≈ (Vth - Vgs) + IsdRon_reverse

Ron_reverse 是第三象限中关断门的等效导通电阻。

与 Si MOSFET 体二极管相比,GaN FET 具有更高的 Vsd 压降,因为当栅极关闭时 Vth - Vgs 通常高于 0.7 V。这可能会导致 GaN 比 Si MOSFET 更高的第三象限损耗。

图 4 显示了第一和第三象限中 GaN FET 的简化行为。 上述分析对于增强型和耗尽型 GaN FET 均适用。

图4 GaN 在第一和第三象限中的简化行为

二、第三象限的工作和损失估计

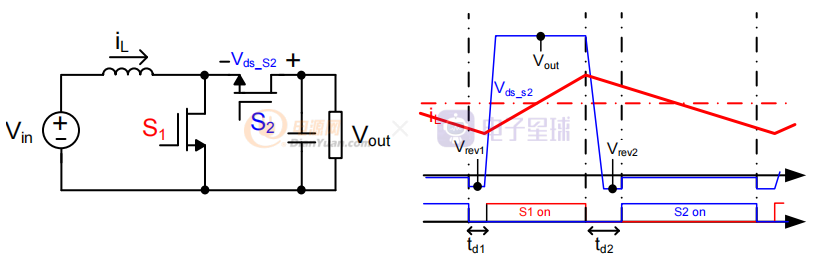

为了进一步解释操作,图 5 中显示了一个使用 GaN 的同步升压转换器作为示例。 当 S1 关闭时,S2 进入第三象限操作。 在 S2 打开之前,S2 像二极管一样工作,遵循第三象限图 4 中红色曲线中的行为。 在死区时间 td2 之后,S2 通道打开,S2 的行为遵循图 4 中第三象限中的蓝色曲线。 S2 关断后,S2 在 td1 的持续时间内恢复二极管动作。

图5 升压转换器中的第三象限操作

上述行为与 Si MOSFET 的不同之处在于,在死区时间 td1、td2 期间 Vds 下降、Vrev1 和 Vrev2 较高。 计算死区时间损失。

Pdt = fsw*td1*Vrev1*iL_vl + fsw*(td2 - tr )*Vrev2*iL_pk

fsw 是开关频率

tr 是 S1 Vds 的上升时间

iL_pk、iL_vl 分别为电感电流的峰值和谷值

Vrev1和Vrev2分别是iL_vl、iL_pk下对应的第三象限压降

对于硬开关边沿,死区时间由输入电荷、栅极驱动器传播延迟和失配决定。 对于软切换边沿,dv/dt 压摆率是另一个主要限制因素。

三、如何最大限度地减少死区时间损失

设计人员有多种选择可以最大限度地减少 GaN 的死区时间损失。

• 为GaN 选择合适的关断栅极电压。

• 最小化死区时间。

• 自适应死区控制

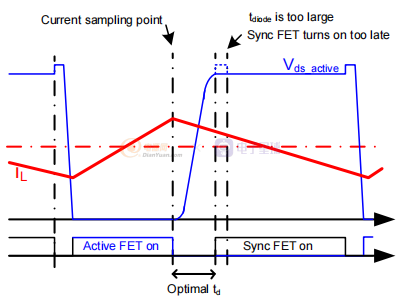

自适应死区时间控制的原理如图 6 所示,其中最佳死区时间几乎等于开关节点电容器充电时间。 最佳死区时间取决于电感器电流和开关节点电容,并且需要在每个开关周期中进行实时校正。 通过这样做,几乎可以消除“二极管”工作周期,如图 6 中的 tdiode 所示。

图6 自适应死区时间控制说明

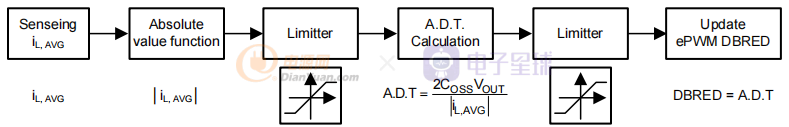

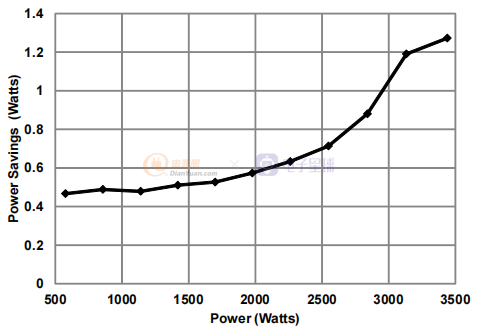

一般有两种实现方式。 通过数字控制,可以根据工作条件计算下一个开关事件的死区时间。 例如,在采用 C2000TM MCU 的基于 GaN 的图腾柱 CCM PFC中,在同步整流器 GaN FET 开启之前,计算死区时间。 图 7 显示了它的实现图。 在高压线 230 Vrms 下,使用自适应控制与固定死区时间相比节省的功率损耗如图 8 所示。

td = CswVo / iL,AVG

• td 是下一个开关事件的最小死区时间

• Csw 是从开关节点到地的总寄生电容

• Vo 是输出电压

• iL,AVG 是当前周期中采样的电感电流

图7. 自适应死区时间控制的实现

图8具有自适应死区时间的节能

对于模拟控制,在同步整流器的一些控制器中实现了自适应死区时间控制。 开关模式电压Vsw被监测并与预定阈值电压进行比较以提供检测信号以开启同步整流器。 检测信号和开启信号之间可能需要一个很短的时间,如 12 ns 到 15 ns,以留出足够的死区时间。

四、总结

横向结构中 GaN HEMT 没有 p-n 结消除了体二极管和反向恢复损耗,从而显着降低了硬开关拓扑中的开关损耗,例如无桥图腾柱 CCM PFC。 为了在相反方向传导电流,GaN FET 自换向并由于横向结构的对称性而表现得像一个二极管,但往往具有较大的 Vsd。 由于死区时间较短,可以最大限度地减少死区时间损失。 自适应死区时间控制是通过根据运行条件修正死区时间来进一步降低损耗的有效方法。