本系列文章的第 5 和第 6 部分介绍有助于抑制非隔离 DC-DC 稳压器电路传导和辐射电磁干扰 (EMI) 的实用指南和示例。当然,如果不考虑电隔离设计,DC-DC 电源 EMI 的任何处理方式都不全面,因为在这些电路中,电源变压器的 EMI 性能对于整体 EMI 性能至关重要。

特别是,了解变压器绕组间电容对共模 (CM) 发射噪声的影响尤其重要。共模噪声主要是由变压器绕组间寄生电容以及电源开关与底盘/接地端之间的寄生电容内的位移电流所导致的。DC-DC 反激式转换器已被广泛用作隔离电源,本文专门对其 CM 噪声进行了分析。

反激式拓扑

DC-DC 反激式电路在工业与汽车市场领域应用广泛,由于可轻松配置成单个或多个输出,尤为适合低成本隔离式偏置轨。需要进行隔离的应用包括用于单相及三相电机驱动器的高压 MOSFET 栅极驱动器,以及工厂自动化和过程控制所用的回路供电传感器和可编程逻辑控制器。

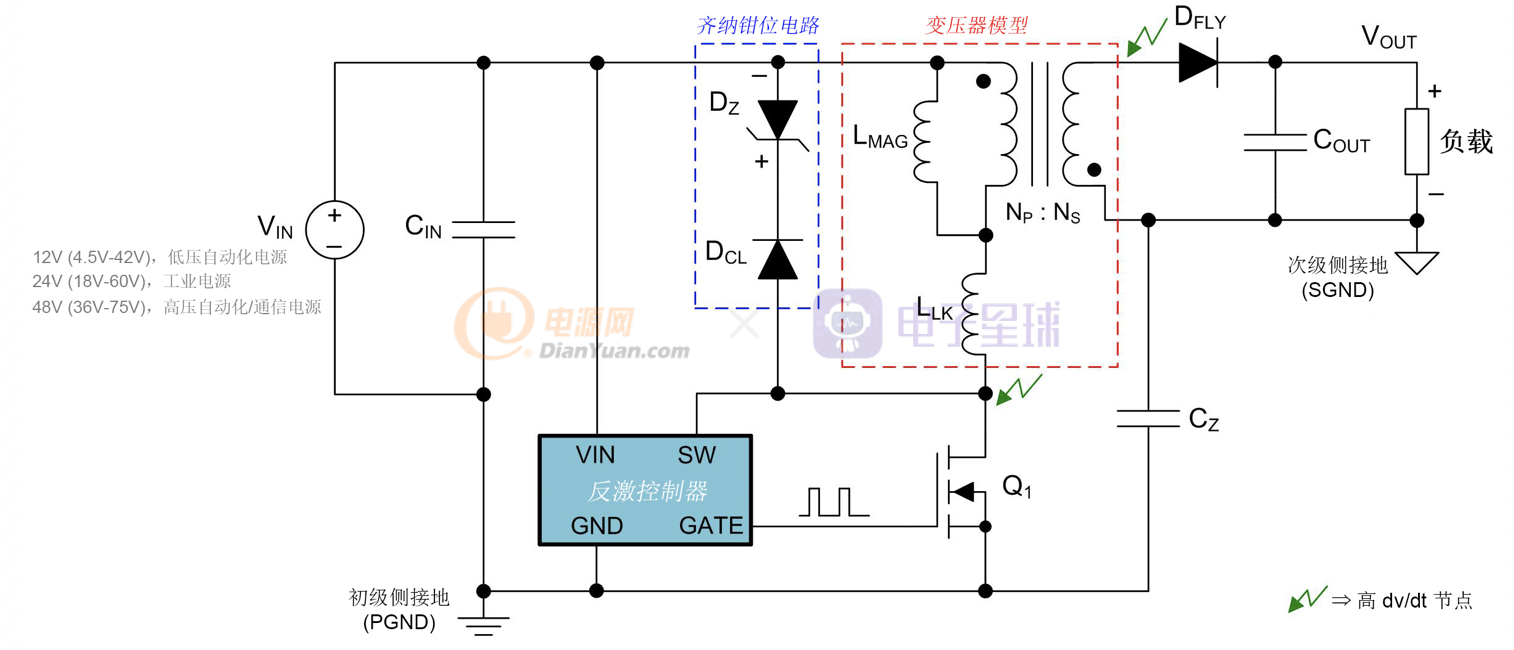

反激式实现方案如图 1 中的原理图所示,该实现方案提供了一种结构简单、元件器数量少的可靠解决方案。如果可以采用初级侧稳压 (PSR) 技术,则反馈稳压无需使用光耦合器及其相关电路,从而能够进一步减少元器件数量,简化变压器设计。具有功能型隔离的变压器可直接实现电路接地隔离,而增强型隔离则用于安全要求极高的高压应用。

图 1:采用典型的 24V 电源或 12V/48V 输入(分别用于工业或汽车电池应用)的 DC-DC 反激式稳压器。图中已明确标出具有磁化作用的反激式变压器、漏电感以及电路寄生电容

图 1:采用典型的 24V 电源或 12V/48V 输入(分别用于工业或汽车电池应用)的 DC-DC 反激式稳压器。图中已明确标出具有磁化作用的反激式变压器、漏电感以及电路寄生电容

反激式开关波形特性

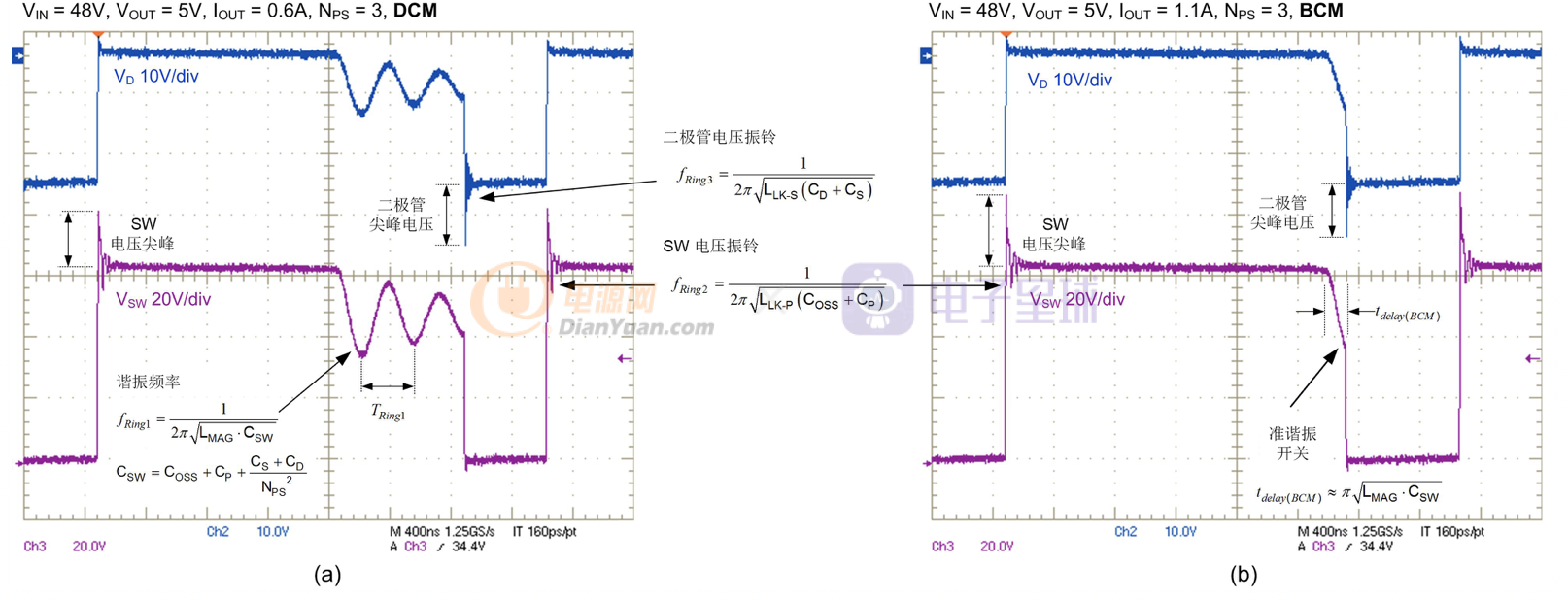

图 2 所示为以非连续模式 (DCM) 和边界导通模式 (BCM) 运行的反激式功率级(如图 1 所示)的初级侧 MOSFET 和次级侧整流二极管电压波形。图 2a 突出显示了 DCM 模式下的开关波形,其中初级侧 MOSFET 在开关节点谐振电压摆幅的谷值附近导通。图 2b 所示为 BCM 开关波形,其中准谐振 MOSFET 在从二次侧绕组电流衰减到零起约半个谐振周期延迟之后导通。在 DCM 和 BCM 模式下,初级侧 MOSFET 均在零电流时导通。

图 2:以 DCM (a) 和 BCM (b) 模式运行的反激式转换器初级侧 MOSFET 和次级侧二极管电压波形;跨越初级侧绕组的 DZ 电路可钳位与漏电感相关的电压尖峰

图 2:以 DCM (a) 和 BCM (b) 模式运行的反激式转换器初级侧 MOSFET 和次级侧二极管电压波形;跨越初级侧绕组的 DZ 电路可钳位与漏电感相关的电压尖峰

除了开关期间尖锐的电压和电流边沿,对于 EMI,电压尖峰过冲以及随后产生的振铃特性尤为棘手。每次换向都会激励开关与二极管寄生电容和变压器漏电感之间的阻尼电压和电流振荡。图 2 所示为 MOSFET 关断时的开关节点电压前沿尖峰和高频振铃。振铃特性取决于与 MOSFET 输出电容 (COSS) 谐振的初级侧漏电感 (LLK-P) 以及变压器初级侧绕组电容 (CP)。类似地,二极管电压振铃取决于与二极管结电容 (CD) 谐振的二次侧漏电感 (LLK-SEC) 及二次侧绕组电容 (CS)。过冲和振铃都会产生较高的瞬态电压 (dv/dt),因此任何至接地端的电容耦合都会导致产生感应位移电流和 CM 噪声。

以连续导通模式 (CCM) 工作时,主开关导通时反激二极管的反向恢复会产生额外的负面作用,使振铃电压升高并产生前沿尖峰电流,随着恢复电流反映到初级侧而流入初级侧 MOSFET。注意,反激式磁性元器件主要相当于耦合电感,因为电流通常不会同时流入初级侧和次级侧绕组。只有在开关转换期间才能出现真正的变压器行为,此时电流同时流入初级侧和次级侧绕组(漏电感中的电流逐渐增大)。

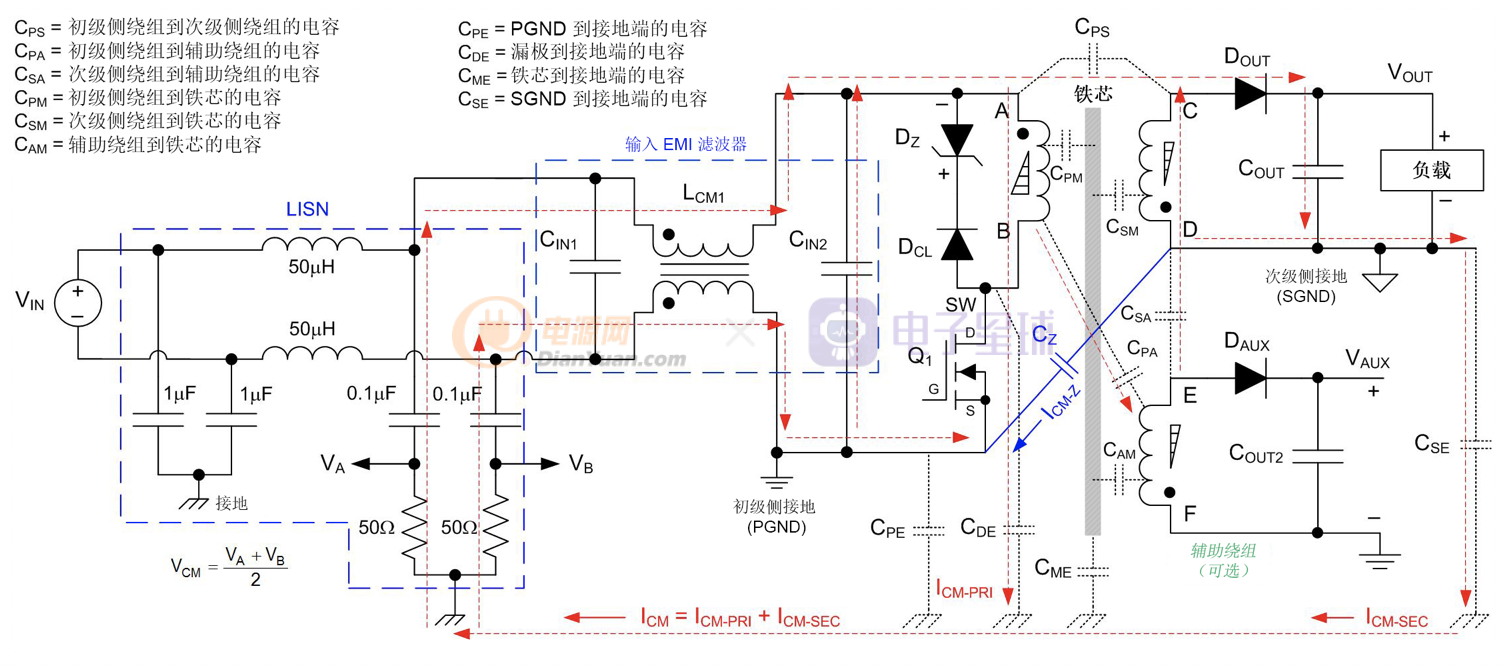

隔离式 DC/DC 反激式转换器中的 CM EMI

图 3 所示为反激式稳压器的原理图,其中连接有用于测量 EMI 的线路阻抗稳定网络 (LISN)。红色虚线表示穿过寄生电容到达接地端并返回到 LISN 的 CM 噪声电流主要传播路径。电容 CZ 从初级侧接地端 (PGND) 连接到次级侧接地端 (SGND),将次级侧的 CM 电流分流回初级侧,其作用是分流流经 CSE 并通过 LISN 返回的 CM 电流。

图 3:双线 DC-DC 反激式稳压器(输入端连接有 LISN)的 CM 噪声电流传播路径。同时,还显示了初级侧基准的辅助输出端

图 3:双线 DC-DC 反激式稳压器(输入端连接有 LISN)的 CM 噪声电流传播路径。同时,还显示了初级侧基准的辅助输出端

尽管初级侧 MOSFET 漏极端子的高转换率电压是主要的 CM 噪声源,但变压器及其寄生电容是传导 EMI 从初级侧传播到次级侧的耦合通道,并且噪声通过阻抗从输出电路传播到接地端。CM 电流主路径(在图 3 中由 ICM-SEC 表示)为,从变压器的初级侧流到次级侧,并通过阻抗从输出电路流到接地端。与非隔离转换器类似,使用较小的开关节点覆铜面积,将 MOSFET 散热器(如果需要)连接到 PGND,同时避免开关节点完全通过过孔连接到电路板底部,这些措施都能消除从 MOSFET 漏极到接地端的耦合(在图 3 中用 ICM-PRI 表示)。

对于此处所述的情况,与变压器相关的以下三大考量因素适用。

首先,紧密耦合变压器绕组可以最大限度地降低漏电感,从而实现高效率和高可靠性,同时降低开关电压应力。交错设计是降低漏电感和绕组交流电阻的常用技术,因此,绕组间电容会相对变大。此外,对于具有印刷电路板 (PCB) 嵌入式绕组的平面变压器,由于各个层堆叠紧密,各层的表面积大,因此,绕组间电容比传统的绕线型设计更高。在任何情况下,将脉冲噪声电压源施加到这种分布式寄生电容,都会产生相对高的位移电流。该电流从初级侧绕组流向次级侧绕组,然后返回到接地端,从而产生较大的 CM 噪声。

其次,与寄生绕组间电容谐振的漏电感可能导致测得的 EMI 频谱中出现明显的高频 CM 噪声峰值。

第三,由于磁芯材料介电常数较高,对电场的阻抗低,因此,由高 dv/dt 节点产生的杂散近电场很容易通过变压器磁芯耦合。然而,如果将磁芯包上铜箔并将铜箔连接到 PGND,则磁芯与地之间的寄生电容 (CME) 会很小。

通常,反激式变压器设计的优化不仅关乎解决方案尺寸、外形、效率和热性能,对 CM 噪声性能也有巨大影响。