一、杂散电容的好与坏

‹ 好,因为它有助于在需要时形成特征阻抗 (Z0)。

‹ 好,因为它有助于在需要时形成特征阻抗 (Z0)。

‹ 不好,因为当不需要特性阻抗时会导致电容。 这会减慢信号或导致放大器振铃或振荡。

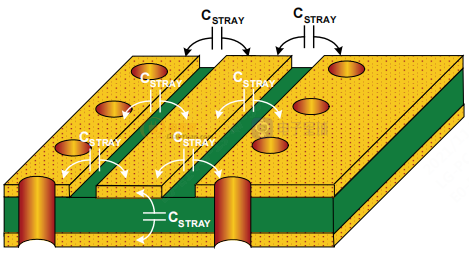

‹由于表面积,以层间电容为主。 走线高度(厚度)非常小(典型值为 0.001 英寸),因此面积和电容很小。

具有杂散电容是为传输线创建特征阻抗的必要条件。 但是,并不总是需要传输线——事实上,系统内部通常不需要它,而仅用于外部接口。如果不需要传输线,那么该电容可能对系统有害。 它会显着降低信号速度,还会导致放大器中出现零点,从而导致振荡。

二、减少杂散电容

可能的解决方案

可能的解决方案

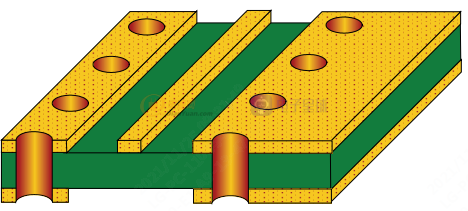

‹如果走线不是特征阻抗,则减小其宽度。 不要太多,否则电感会增加太多。

‹ 移除走线下方的 GND 平面。将这些平面连接到别处。

‹ 增加走线与同层 GND 平面之间的距离。

要将杂散电容降至最低,只需将接地层与信号走线分开即可。 这可能涉及增加顶层的距离,和/或移除信号走线下方的接地层。请记住,电源层被视为交流接地,其行为与接地层完全相同。 因此,移除电源层与移除敏感区域的接地层一样重要。 这通常被称为护城河。

三、测量PCB板上的杂散参数

在构建一块 PC 板后,人们常常不确定走线是否具有正确的电感或电容。 在没有网络分析仪或 TDR 的情况下测量这些值更加困难。

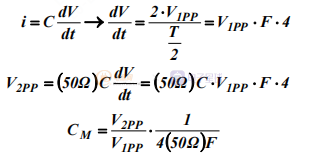

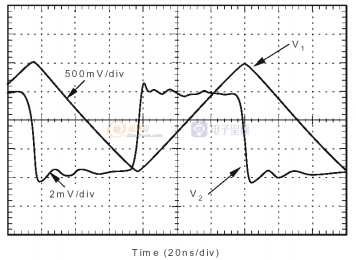

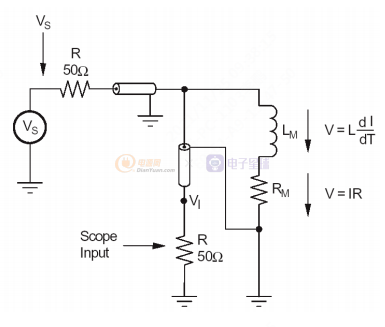

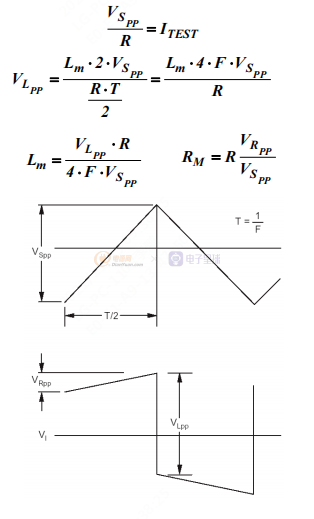

测量走线电容的一种非常简单的方法是使用斜坡发生器和示波器,连接方式如图所示。

测量走线电容的一种非常简单的方法是使用斜坡发生器和示波器,连接方式如图所示。

在某些情况下,需要知道实际走线上有多少寄生(杂散)电容。 这可能有助于确定稳定性问题或验证特性阻抗。测量这一点的相对简单的方法是使用上述测试设置。 此设置使用 HP8116A 函数发生器 (Vgen) 通过同轴电缆驱动三角波,其中一端焊接到电路板走线、地平面等,并使用端接 50Ω 的示波器测量两个相同点。 这种方法可以 以 30f 至 50f 的精度测量电容,并包括与高频场相关的边缘效应。

在某些情况下,需要知道实际走线上有多少寄生(杂散)电容。 这可能有助于确定稳定性问题或验证特性阻抗。测量这一点的相对简单的方法是使用上述测试设置。 此设置使用 HP8116A 函数发生器 (Vgen) 通过同轴电缆驱动三角波,其中一端焊接到电路板走线、地平面等,并使用端接 50Ω 的示波器测量两个相同点。 这种方法可以 以 30f 至 50f 的精度测量电容,并包括与高频场相关的边缘效应。

测量迹线电感的一种非常简单的方法是使用斜坡发生器和示波器,连接方式如图所示。

与测量 PCB 走线的电容非常相似,此设置展示了如何准确测量 PCB 走线的电感。

与测量 PCB 走线的电容非常相似,此设置展示了如何准确测量 PCB 走线的电感。