变压器绕组绕在磁芯骨架上,特别是绕组的层数较多时,不可避免的会产生分布电容,由于变压器工作在高频状态下,那么这些分布电容对变压器的工作状态将产生非常大的影响,如引起波形产生振荡,EMC变差,变压器发热等。所以,我们很有必要对变压器的分布电容狠狠的研究一把,下面我们就对这个分布电容来展开讨论。

分布电容既然有危害,那么我们就要设法减小这个分布电容的影响,首先我们来分析下分布电容的组成,变压器的分布电容主要分为4个部分:绕组匝间电容,层间电容,绕组电容,杂散电容,下面我们来分别介绍。

首先讲讲绕组匝间电容

我们知道电容的基本构成就是两块极板,当两块极板加上适当的电压时,极板之间就会产生电场,并储存电荷。那么,我们是否可以把变压器相邻两个绕组看成连个极板呢?答案是可以的,这个电容就是绕组匝间电容。

以变压器初级绕组为例,当直流母线电压加在绕组两端时,各绕组将平均分配电压,每匝电压为Vbus/N,也就是说每匝之间的电压差也是Vbus/N。当初级MOS管开关时,此电压差将对这个匝间电容反复的充放电,特别是大功率电源,由于初级匝数少,每匝分配的电压高,那么这个影响就更严重。

但总的来说,匝间电容的影响相对于其他的分布电容来说,几乎可以忽略。要减小这个电容的影响,我们可以从电容的定义式中找到答案:

C=εS/4πkd

其中 C:绕组匝间电容量

ε:介电常数,由两极板之间介质决定

S:极板正对面积

k:静电力常量

d:极板间的距离

从上式我们可以看出,可以选用介电常数较低的漆包线来减小匝间电容,也可以增大绕组的距离来减小匝间电容,如采用三重绝缘线。

接下来我们来看看看绕组的层间电容

这里的层间电容指的是每个单独绕组各层之间的电容。我们知道,在计算变压器时,一般会出现单个绕组需要绕2层或2层以上,那么此时的每2层之间都会形成一个电场,即会产生一个等效电容效应,我们把这个电容称为层间电容。

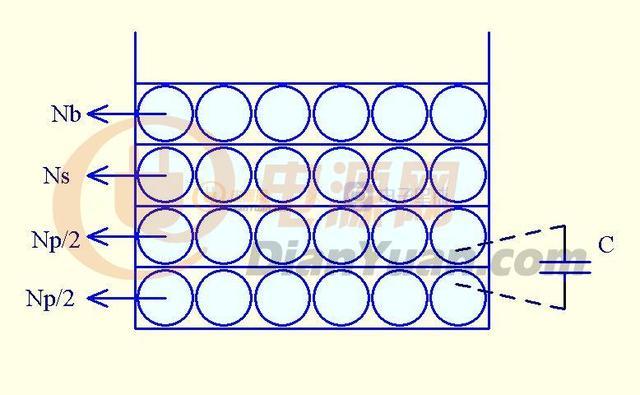

如下图:

电容C就是层间电容

层间电容是变压器的分布电容中对电路影响最重要的因素,因为这个电容会跟漏感在MOSFET开通于关闭的时候,产生振荡,从而加大MOSFET与次级Diode的电压应力,使EMC变差。既然有害处,那么我们就需要想办法来克服它,把它的影响降低到可以接受的范围

方法一:

参照上面给出的公式,在d上作文章,增大绕组的距离来减小层间电容,最有代表性的就是采用三重绝缘线。但这个方法有缺点,因为线的外径粗了之后,带来的后果就是绕线层数的增加,而这不是我们想看到的。

方法二:

可以通过选择绕线窗口比较宽的磁芯骨架,因为绕线窗口宽,那么单层绕线可以绕更多的匝数,也意味着可以有效降低绕线的层数,那么层间电容就有效降低了。这个是最直接的,也是最有效的。但同样有缺点,选择磁芯骨架要受到电源结构尺寸的限制。

方法三:

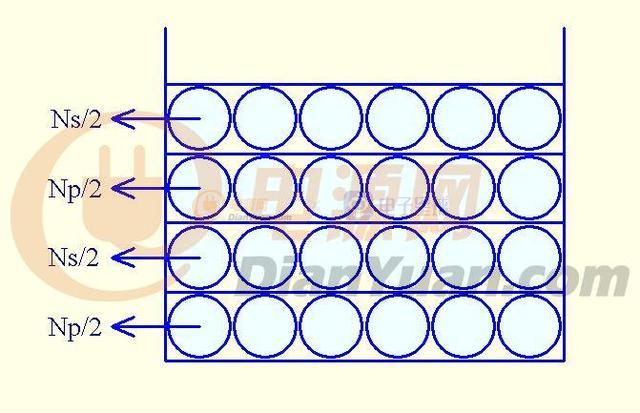

可以在变压器的绕线工艺上来作文章,可以采用交叉堆叠绕法来降低层间电容,如下图

此种绕法有个显著缺点,会增加初次级之间的耦合面积,也就是说会加大初次级绕组之间的电容,使EMC变差,有点得不偿失的感觉。

方法四:

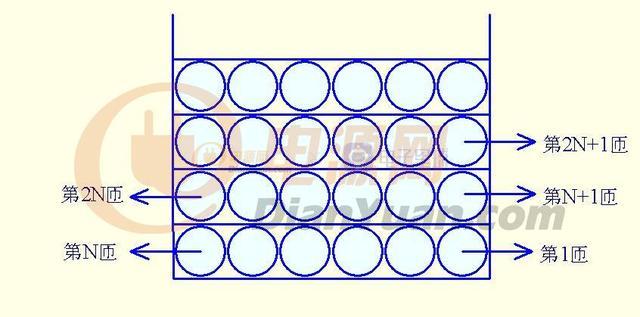

还是在绕制工艺上作文章,先来看普通的绕法

如上图,这个是我们常用的绕法(也叫U形绕法),我们可以清楚的看到,第1匝与第2N匝之间的压差将非常大,在初中我们学过的物理上有讲,Q=C*U,压差越大,那么在这个电容上储存的电荷就越多,那么这个地方的干扰电压斜率将非常大,也就是说在这个地方形成的干扰就越大。

我们可以采用Z形绕法来降低这个影响,Z形绕法(也叫折叠绕法)如下图:

从上图我们可以看到,此种绕法可以显著降低电压斜率,对EMC是非常有利的。缺点就是绕制工艺相对复杂点。

下面我们来说说绕组电容

顾名思义,绕组电容就是指绕组之间产生的电容,比如说初级绕组Np与次级绕组Ns之间的电容。此电容由于存在于初次级绕组之间,对电路的EMI是相当不利的,因为初级产生的共模电流信号可以通过这个电容耦合到次级中去,这就造成了非常大的共模干扰;而共模干扰可能会引起电路噪音或者输出的不稳定。

解决的方法一般就是在初次级之间加一个屏蔽层,并且将这个屏蔽层接到电路中的某点,来降低此电容的影响。一般把这种屏蔽层称为法拉第屏蔽层,一般由铜箔或绕组构成。在用铜箔时,我们一般用0.9T,或者1.1T,不选择1T,因为1T的话,容易短路。

大家思考下,为何不能短路,短路会带来什么样的后果?欢迎在评论区回复交流。