大家好,我是电源漫谈,很高兴和各位一起分享我的第39篇原创文章,喜欢和支持我的工程师,一定记得给我点赞、收藏、分享。

晶振电路是嵌入式系统不可或缺的部分,尤其是一些需要高精度时钟的场合,如CAN通信需求,使用外部晶振是常见的做法。

一.皮尔斯振荡电路基本介绍

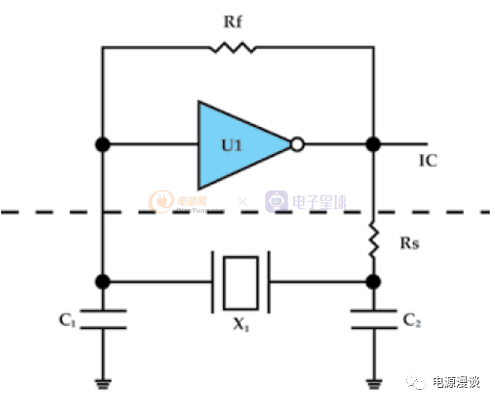

现如今使用最为广泛的晶振电路是所谓的皮尔斯振荡电路,如图1所示。其中的反相器U1通常包含在MCU或者ASIC中。

图1 皮尔斯振荡电路的基本模型

大多数系统设计者不是很注意振荡电路的设计,直到出现问题后才引起重视。接下来,我们从元件级别分析一下皮尔斯振荡电路及其运行的关键点,同时讨论对其典型设计的过程。首先,我们通过Barkhausen准则来说明振荡电路如何工作。在期望的振荡频率处,我们需要其整个环路增益大于等于1,以便维持其振荡条件,另外,整个环路的相移是0或者2*Π的整数倍。

图2 皮尔斯振荡电路的相移分析

二.晶体振荡器各个部分器件的设计影响

整个环路的相位设计:

具体来说,首先U1作为反相器会提供-180C的相移,另外-180C的相移取决于外部器件,以满足Barkhausen准则。如果U1提供的相移是-185C,那么其它部分的电路会自动调整相移为-175C,以满足-360C的相移。

整个振荡环路的增益,是U1的跨导增益,然后再叠加C1,C2的电抗增益,及Rs的增益,三者增益乘积就是整个环路增益。对于初始设计而言,Rs的值可以设计为C2电抗值一样。

对于这些器件的影响来说,减小C1,C2的电容值时,就增加了环路的增益,而增加Rs值就减小了环路的增益,这一点大家需要注意。

反馈电阻的设计影响:

对于反馈电阻Rf来说,它的主要作用是线性化数字CMOS电路反相器。具体来说,Rf在反相器输出端通过电阻给反相器输入电容Cin及负载电容C1充电,这样就把一个逻辑电路转换为一个模拟运放电路。

通常反馈电阻Rf会包含在MCU或者ASIC电路中,同样的,我们可以通过一些测试方法,判断是否MCU或者ASIC集成了相应的反馈电阻Rf。

当将晶体X1以及C1,C2,Rs等全部移除电路后,测量反相器的输入和输出电压值,如果内部集成了反馈电阻Rf,则会看到输入电压和输出电压都是1/2Vcc附近。如果没有集成内部Rf,则输入电压和输出电压值为低电平0或者高电平1.

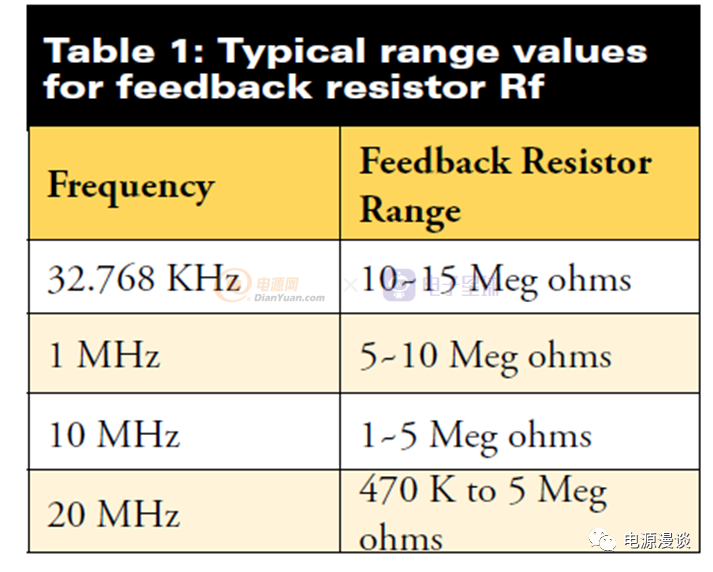

图3 振荡频率和Rf电阻的匹配关系

不同的工作振荡频率,可以匹配不同的反馈电阻,振荡频率越低,则对应的反馈电阻越大,具体关系可以参考图3所示的表格。

通常,我们可以通过调整Rf来优化其设计值,将所有器件包括X1,C1,C2,Rs装上,调整Rf值,画出频率和Rf的关系曲线,会发现牵引振荡频率的点,那么可以选择高于这个点以上的Rf电阻。

输出串联电阻Rs的设计影响:

和反相器相串联的电阻Rs的主要作用,其一,隔离反相器的输出和外部阻抗网络。其二,提供控制晶体的驱动水平的自由度,通过流过晶体的电流来表示,并同时可以调整环路的增益。

通常Rs必须要和音叉晶体来使用,因为音叉晶体有一个最大驱动水平1微瓦,如果此时没有一个大于10k的电阻的话,那么晶体很可能会被物理损坏。

一般的,Rs和C2可以组成一个滞后网络,以便增加相应的相移,当某些条件下,尤其是低于8M时,如果有这部分额外相移,可以减小时域的抖动或者频域的相噪。有些时候,尤其是高频下,由于反相器的输出阻抗和C2电容组成的网络产生的相移已经足够,这时,虽然不需要提供额外相移,但是还是需要减小晶体驱动水平。

U1反相器的设计影响:

U1反相器的主要作用,是提供必要的增益去保持振荡,同时产生-180C的相移。如果U1是MCU或者ASIC的一部分,那么生产商需要指定一些晶体的关键参数,如可以工作的最大ESR等。

如果U1不是MCU或者ASIC的部分,那么设计时需要选择合适的增益和相位调整的反相器,以便工作在特定频率或者范围,有必要时,可以进行仿真。

有一点需要注意的是,并非所有的数字反相器都可以作为振荡器场合使用,有些数字反相器的传输延时非常大,即使在低频下也是显得大。在过去,通常需要选择无buffer的反相器,但是随着高速应用的需求及技术的发展,反相器的延时都已经减小了,所以这通常不是问题,具体可以参考相应的产品的特性。

负载电容的设计影响:

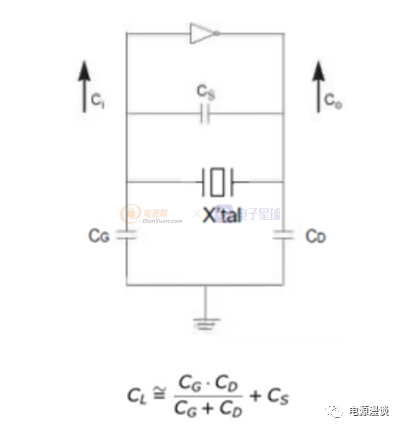

X1晶体,和C1, C2负载电容可以构成一个外部网络,提供-180C的相移,以满足Barkhausen准则,以持续振荡。

大多数情况下,C1和C2可以设置为一样的值,如果有需要,C2可以比C1大一些,设置中心频率,并增加环路增益,环路电压增益是和C2/C1的值相关的。

最后提一下,晶体振荡器电路需要的是一个,并联模式的基本的振荡器,在皮尔斯振荡器中,它工作在电抗曲线的感性区。

三.具体振荡电路设计案例说明

图4 设计20M时钟的基本要求示例

如图4所示,我们介绍一个20M时钟,+-50ppm频率温度稳定度的需求,常温为+-50ppm的容差,工作温度为-20C到70C的范围,其它要求比如低成本,SMT等。

我们首先给出一些已知条件,反相器是MCU的部分,且我们可以查到Cin=4p,Cout=9pF。Rf的反馈电阻不是内部的。MCU规定允许的最大晶体的ESR为40ohm,以稳定运行在指定频率。

最终我们要把C1,C2,Rs,Rf求出来,并且指定晶体。

首先,我们先选择一个Rf,根据前述的频率要求,我们选择1M电阻。C1,C2,Cin,Cout将设置所需要的负载电容,一般来说,对于一个时钟设置,我们需要负载电容是一个标准电容值,以方便购买,如18pF或者20pF等,这也是两个晶体行业最普遍的负载电容值。

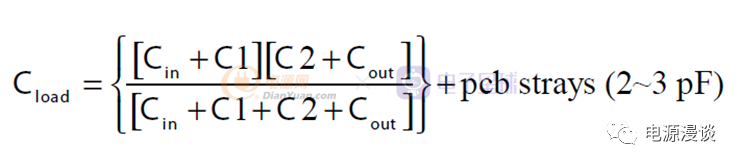

图5 负载电容计算

在皮尔斯振荡电路中,负载电容可以求解如上图5所示的公式。大多数设计者可能不知道Cin,Cout这两个参数的存在,或者不知道如何得这两个参数。

Cin和Cout的值相比外部电容C1,C2的值,也是很重要的值。当我们不确定这两个参数时,可以猜测估算它为5pF,后续可以通过改变C1,C2的设计起始值来进行优化。

图6 确定负载电容

通过几次迭代,根据PCB杂散电容为3pF,Cin=4pF,Cout=9pF,则可以求得负载电容为19.7pF=20pF。C1=C2=27pF。

指定晶体的负载电容是20pF,我们需要频率满足常温的容差是+-50ppm。通常容差可以在板上校准,但是我们的需求是在生产中无需trimming,即可达到期望的精度。为了设计这个无校准容差规格,我们需要知道在负载电容20pF附近,晶体频率如何随着负载电容变化而变化。

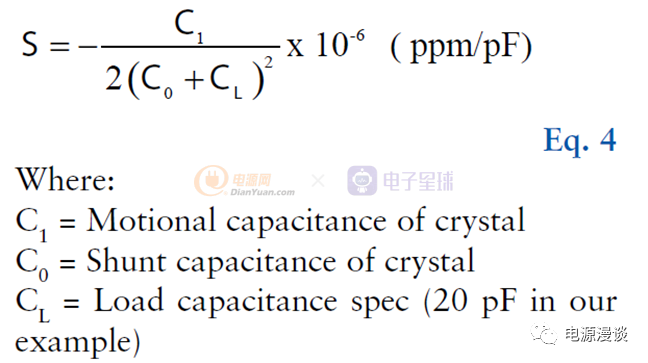

图7 Trim敏感公式

上述公式中,C1为晶体的动态电容,C0为晶体的寄生电容,CL为负载电容,此处案例中为20pF。

上述方程表达了在负载电容20pF附近,每移动1pF,常温下输出频率变化的范围,首先我们需要知道动态电容和寄生电容。当然,在没有得到晶体产品之前,我们可以假定一个值,然后得到产品后再去确认这个参数,来决定我们假定的范围是否足够。

典型的标准晶体的Trim敏感度指标是-15ppm/pf到-30ppm/pF。因此我们设定晶体的容差规格为+-20ppm。

一旦你确定了实际的晶体的C0,C1数据,你可以确定我们所设定的margin是否足够,中心的频率的生产数据也需要分析一下,是否有必要调整C1,C2的值。

一般来说,容差规格越紧,则晶体价格越高,标准晶体的容差范围一般是+-25ppm,或者是+-50ppm。同时负载电容CL会直接影响容差规格和价格,在Trim敏感度方程中,CL越小,则敏感度越大。最终C2设置为27pF,根据前述设计准则,会将Rs设计为和C2电抗一致的阻抗值,频率越高,则Rs越小。

对于晶体的类型来说,一般来说需要AT-cut类型,因为BT-cut不能满足40ppm的频率-温度稳定度。此时我们就可以把这些基本规格给到晶体厂家。

汇总一下,我们的初始参数设计规格如下:

Rf=1Mohm

Rs=390ohm

C1=27pF

C2=27pF

晶体的基本要求如下:

振荡频率20MHz

类型为AT-cut

负载电容CL为20pF的并联晶体

常温容差+-20ppm

频率稳定性+-40ppm(-20-70C)

ESR为40ohm max

Shunt电容C0为7pF

一般的,产品的量越大,越要小心评估晶体的设计及性能,主要需要注意的测试项如下:

测试增益裕量

执行频率对稳温度的变化测试考虑全范围运行电压

执行在温度极限下的启动测试考虑全范围运行电压

通过晶体的驱动电流测试

到此为止,我们就完成了一个典型的皮尔斯振荡电路的设计,并提供了晶体的基本要求信息。

四.石英晶体的一些典型参数解释

通常石英晶体会在规格书上标出,标称频率,频率稳定性,工作温度,负载电容CL等,同时会提供寄生电容Shunt电容,动态电容motional电容等。

图8 典型晶体规格书参数

负载电容通常是指,以晶体为核心的整个振荡回路的全部有效电容的总和,CL值的大小决定着振荡器的工作频率,可以通过调整CL的值,来调整系统的工作频率调到标称值。

图9 晶体电路典型说明

负载电容的典型标称值,一般由厂家给出,如12.5pF,16pF,20pF,30pF等,当CL减小时频率偏差变大,通过我们前边图7的公式也可以看出。

另外一个典型电容参数Cs,就是晶体的并联电容,如图9所示,它是并联在晶体上的寄生电容,这个参数一般可以在晶体规格书中查询到。上述示例中显示为1.2pF。

动态电容Motional电容,在上述示例中也可以看到是6fF,这是一个非常小的电容值,通常可以忽略。

总结,我们通过分析皮尔斯振荡电路的基本原理,并探讨了各个部分组成元件的设计影响,同时给出一个设计示例,最后通过一个典型的晶体规格书,来了解了几个典型的电容参数概念。

参考文献:Pierce-Gate Crystal Oscillator, an introduction