大家好,我是电源漫谈,很高兴和各位一起分享我的第55篇原创文章,喜欢和支持我的工程师,一定记得给我点赞、收藏、分享。

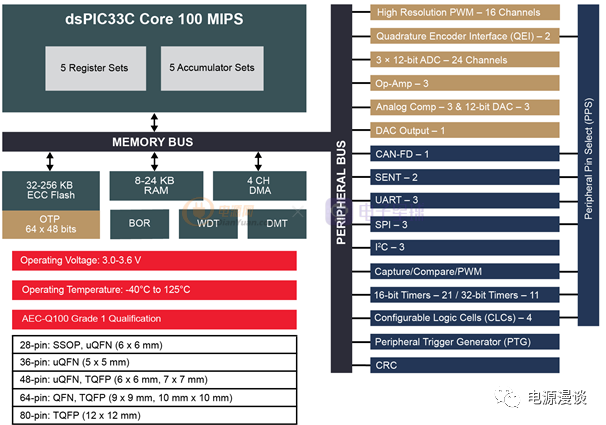

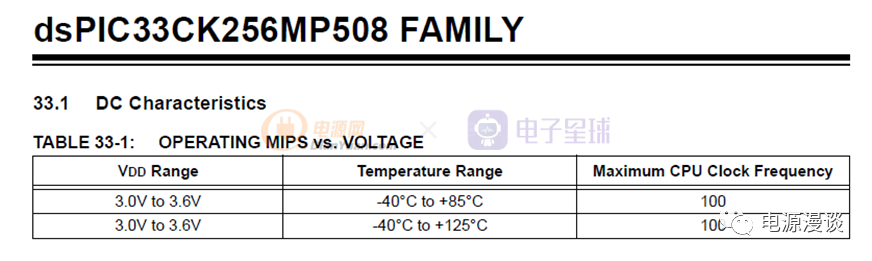

在数字电源应用中,不管是车载OBC还是无线充电电源等,都是比较典型的重要应用,项目开发过程中,时钟模块配置正确与否,不仅涉及到代码的执行,也涉及到诸多外设的性能,其中dsPIC33C系列芯片主频最大可以达到100MIPS,如图1所示,而在500M辅助时钟频率驱动下,PWM模块的分辨率可以达到250ps,所以我们通过这篇文章来对dsPIC33CK单核及dsPIC33CH双核的时钟模块的MCC配置进行简要说明。

图1 dsPIC33CK系列典型资源图

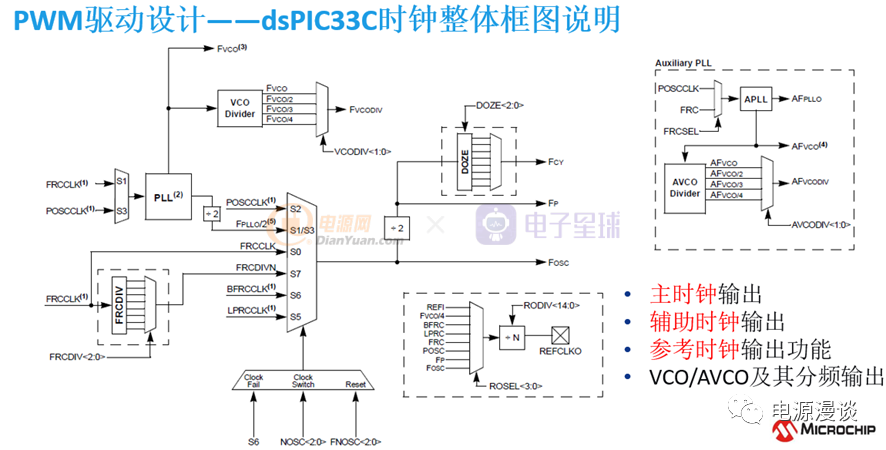

图2 dsPIC33C时钟系统整体框图

在图2所示的时钟系统整体框图中,我们可以看到PLL时钟部分,左侧输入时钟FRCCLK或者POSCCLK进入系统后,可以经过主锁相环PLL产生FOSC,对于dsPIC33CK单核系统,我们最高将它配置为200M的FOSC,对应100MIPS的指令时钟。

除了这个系统主时钟外,我们还有一个辅助锁相环APLL时钟,如图2中右上所示,输入时钟FRC或者POSCCLK进入辅助锁相环APLL系统后,最终可以产生AFVCODIV分频输出时钟,或者AFPLLO时钟输出,这个AFPLLO时钟一般配置为500M以满足PWM模块的高精度运行要求,或者作为其它外设的驱动时钟。

一.单核dsPIC33CK系列的时钟模块配置(FRC为输入时钟)

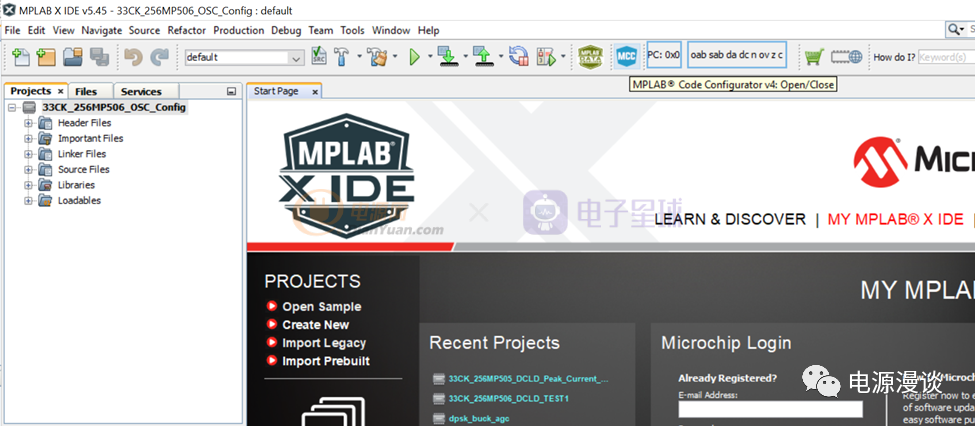

图3 新建项目工程文件

当建立好工程文件后,并且也安装好了MCC插件,如图3所示,可以看到工具栏中MCC图标是蓝色的可以操作的状态。

图4 保存MCC配置文件

当点击工具栏中MCC的图标后,可以看到如图4所示的对话框,在这里,你可以输入MCC配置文件的名字,也可以按照默认名字保存文件,则.mc3的配置文件就保存在了工程文件目录下了。

图5 MCC配置界面

当保存配置文件后,则可以打开MCC的配置界面,如图5所示,相当清爽的一个界面。在左下侧,你可以看到器件资源区域,当点击资源区域的外设后,它就进入左侧上部的项目资源区域中,右侧是你当前选择的模块的配置界面显示。System Module,pin Module,Interrupt Module是默认放在项目区域的三个模块。

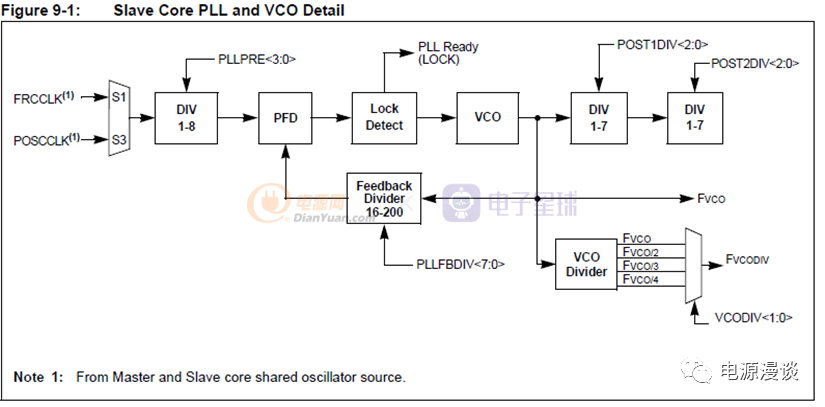

在配置主锁相环PLL的系统输出时钟之前,我们先看一下其主要结构。

图6 主PLL的基本结构

如图6所示,内部的FRC振荡器FRCCLK,或者外部晶振时钟源POSCCLK都可以作为PLL的时钟源输入,经过一系列倍频及分频操作后,产生PLLO或者FVCODIV的输出.

图7 PLL配置的一些限制要求

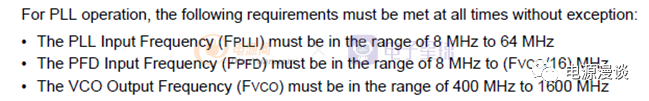

对于具体配置来说,并不是随意的,按照FRM手册的要求,如图7所示,我们需要满足PLL输入时钟频率为8M-64M之间,PFD输入频率为8M-FVCO/16之间,VCO输出频率为400M-1600M之间,我们需要在MCC配置时进行检查确认,其中,在芯片电气规格中也列出了相应的指标,如图8所示。

图8 PLL电气规格要求

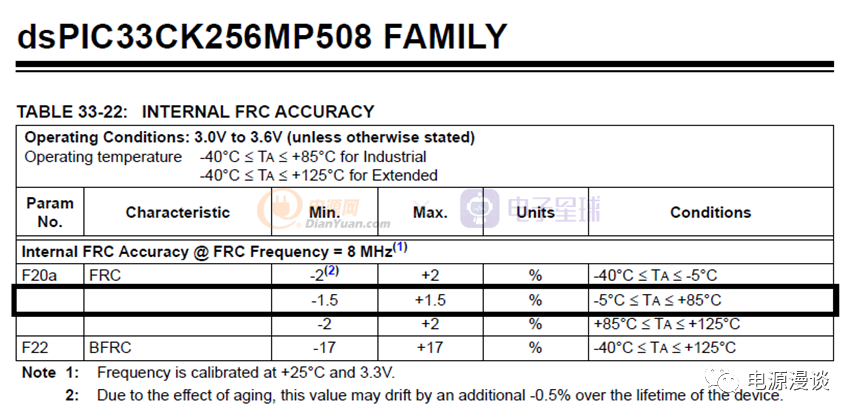

当点击左侧System Module后,可以看到和系统相关的设置界面,我们首先进行系统时钟的设置,这里,我们选择芯片内部的8M FRC振荡器为输入源,并使能PLL,这个振荡器精度虽然比不上外部晶振,但是一般的电源应用都可以满足要求,如图9所示,其典型温度范围的精度为+-1.5%。

图9 FRC的主要精度指标

图10 系统时钟FOSC的配置示例

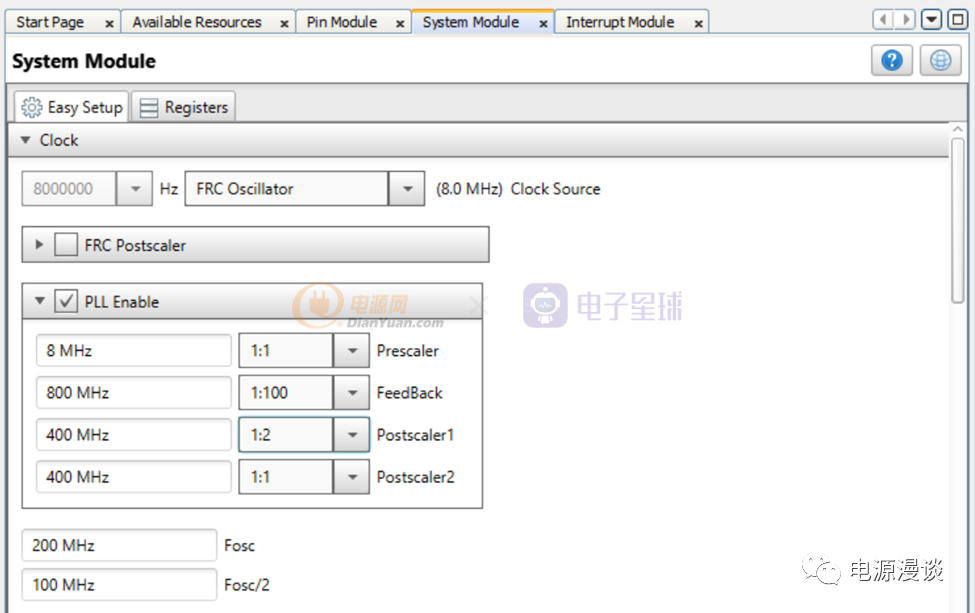

在图10中,我们给出了一组典型的配置供参考,可见FOSC配置为了200M,对应指令时钟FCY为100M,在dsPIC33CK器件上,它可以在125C时运行在100MIPS,如图11所示。

图11 dsPIC33CK温度范围和时钟频率的关系

在dsPIC33C系列芯片上,除了系统时钟源FOSC,还提供一个辅助锁相环时钟APLL,它主要用于为各种外设提供时钟源,并独立于系统时钟,其结构框图如图12所示。APLL的输入时钟也是由FRCCLK或者POSCCLK组成,经过一系列分频和倍频,产生AFPLLO,或者AFVCODIV两种输出频率。

图12 辅助时钟APLL的结构框图

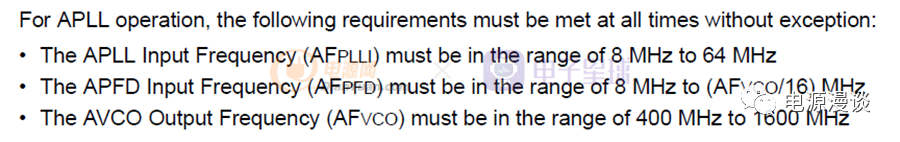

APLL的配置类似于PLL的配置,需要满足一定的限制条件,我们在图13中列出,其输入时钟需要在8M-64M之间,其PFD输入频率要在8M-AFVOC/16之间,AFVCO输出频率需要在400M-1600M之间。

图13 APLL配置的限制条件

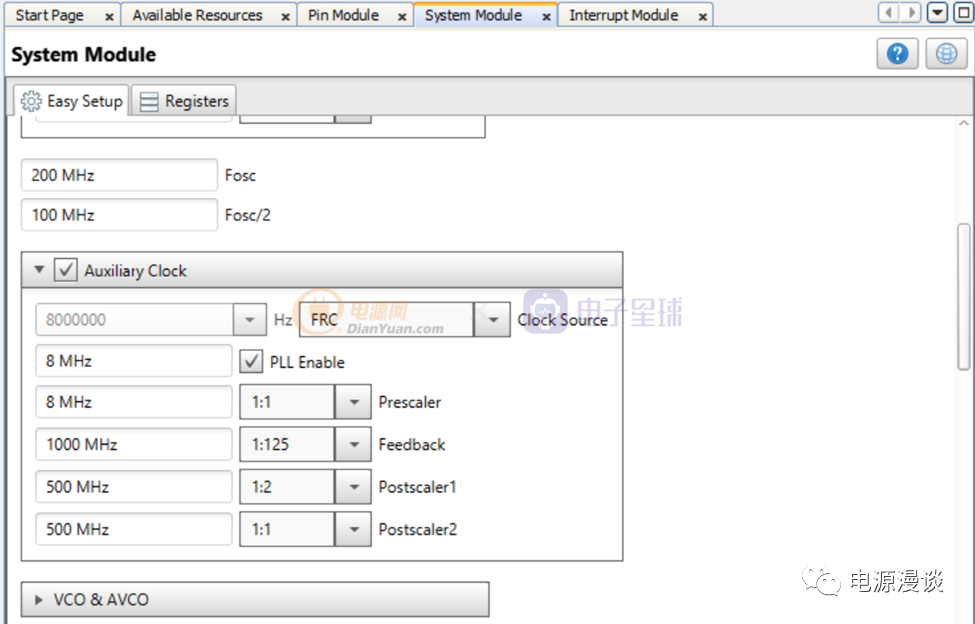

图14辅助时钟APLL的配置示例

在图14中,我们给出一个典型的APLL配置示例,同样采用了8M的FRC作为输入时钟,最后得到500M的APLLO时钟,这个时钟可以作为PWM模块的输入时钟,产生高精度PWM波形。

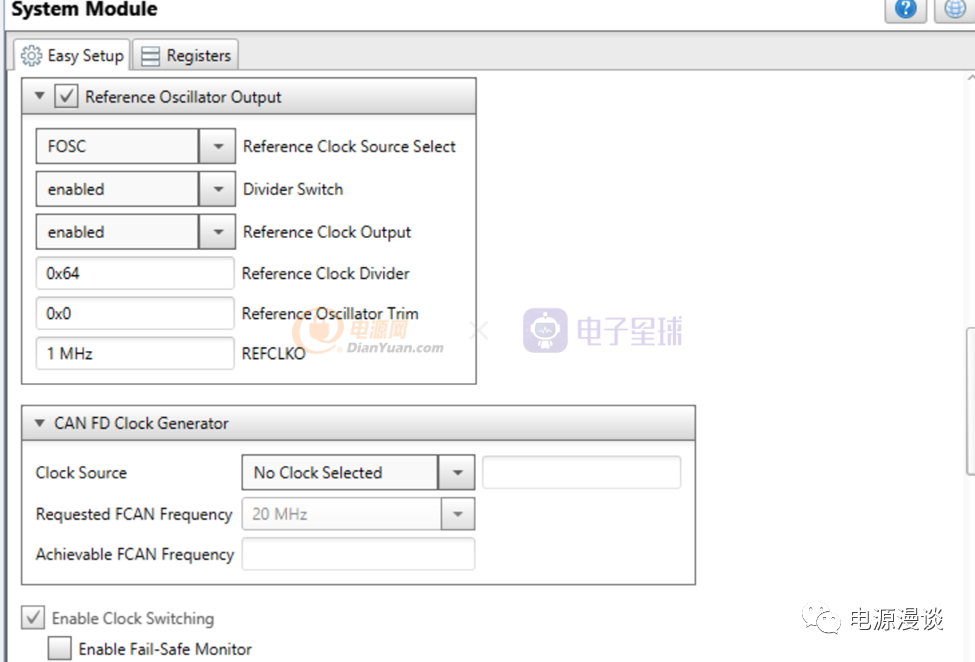

图15 参考时钟输出配置示例

在配置时钟源后,我们希望确认一下相应的时钟输出是否达到我们的期望,是否有正确的波形,所以,我们通过参考时钟输出模块的配置来实现这个目的,在电路debug过程中这一点对于分析电路也很有意义。

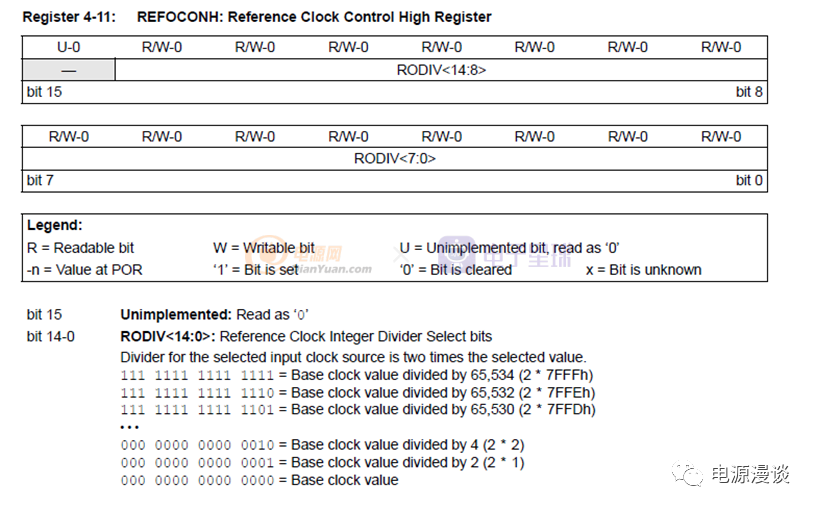

图16 参考时钟分频设置

因为内部PLL或者APLL输出的时钟频率非常高,很难在测试设备观察到,在图16中所示的REFOCONH寄存器中可以设置参考时钟的输出分频,比如,设置为1,就代表2分频。

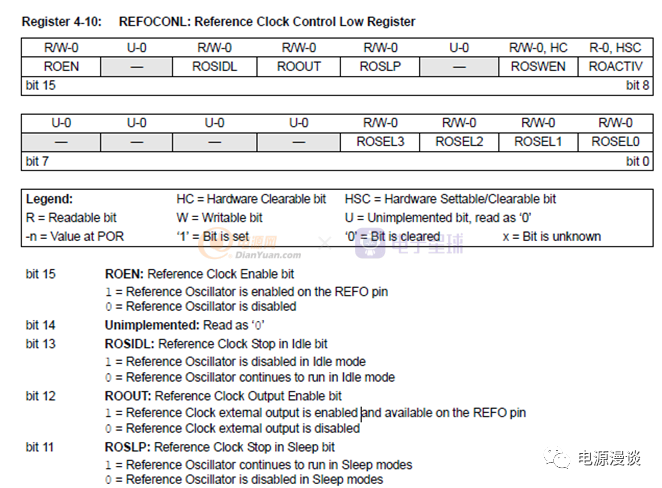

图17 参考时钟输出使能及源选择

在图17所示的REFOCONL寄存器中,我们可以设置是否使能参考时钟,及选择相应的时钟输出,比如FOSC或者FRC等,在图15的配置示例中,我们选择FOSC输出,并且分频值设为100,即分频比为200,因为我们设置为最高主频100MIPS,所以FOSC为200M,分频后频率为1M.

图18 参考时钟输出说明

在图18所示的FRM对参考书时钟输出说明中,指出参考时钟REFO可以在任何可以映射的RP pin上输出,方便用户选择。

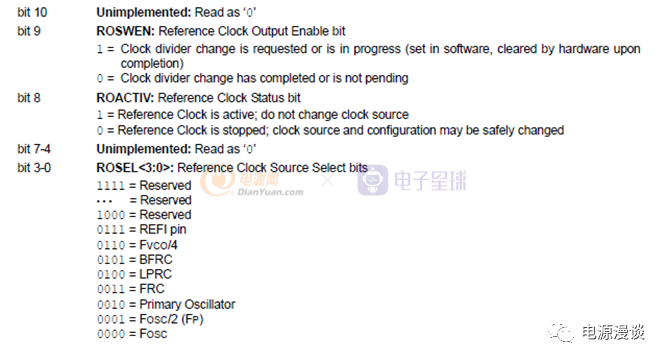

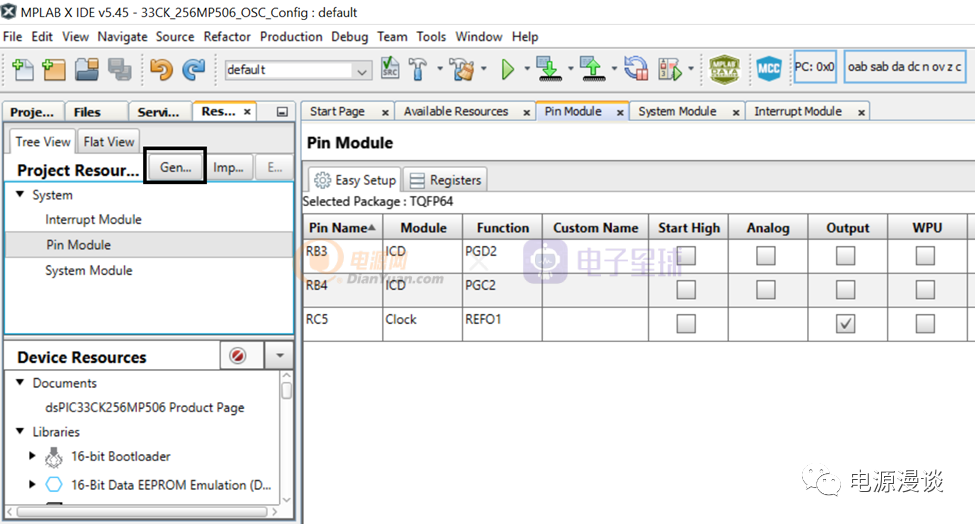

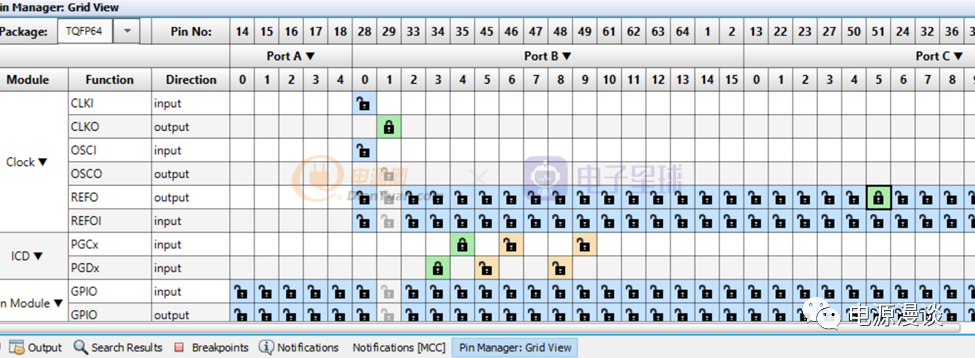

图19 编程端口的选择

在图19所示截图中,设置正确的编程端口,以保持和硬件电路一致,确保能正确的编程和Debug芯片,这里我们根据开发板硬件选择PGD2和PGC2.

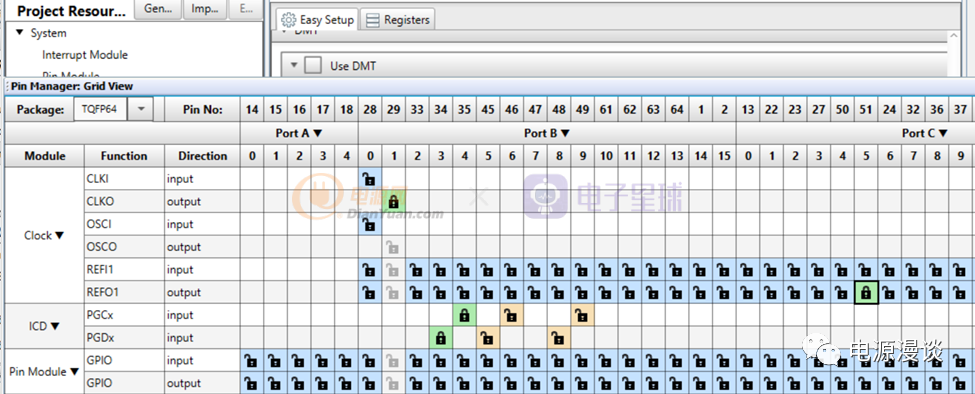

图20 参考时钟输出的PPS选择

由于参考时钟需要在RP pin输出,我们在图20所示的截图中,根据需要我们设置在RC5上输出参考时钟,对应pin51.

图21 pin module的确认

在图21所示截图中,我们检查相应的pin的设置是否正确,如果需要对pin做进一步设置,可以在这里设置,尤其是输入和输出的功能,或者模拟和数字的功能等。

图22 产生代码

所有设置完成后,我们就需要产生代码,按图22所示按钮,就可以产生相应的代码。

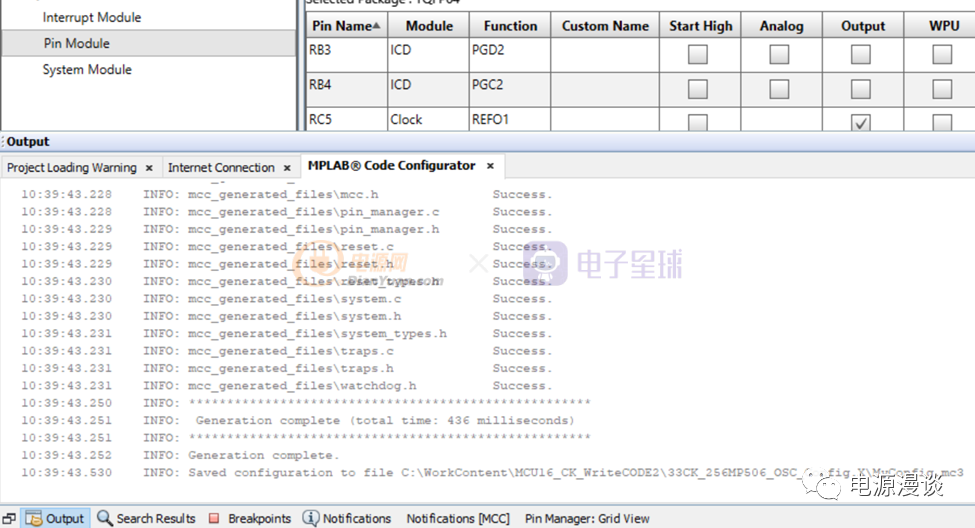

图23 代码产生过程信息

在图23所示窗口中,你可以看到MCC产生代码的过程及状态,最后会显示代码产生结束,并且配置文件保存到了.mc3文件。

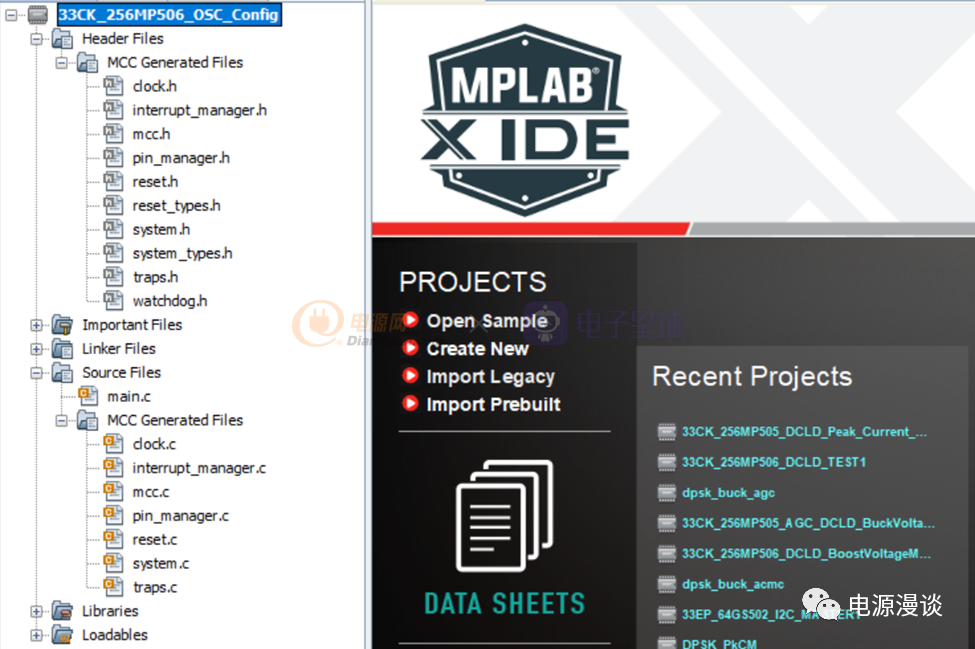

图24 代码文件结构

产生代码后,点击工具栏MCC图标,退出MCC,review一下代码文件结构,如图24所示截图,可以看到相应的.h头文件和.c文件的组成。

图25 main函数结构

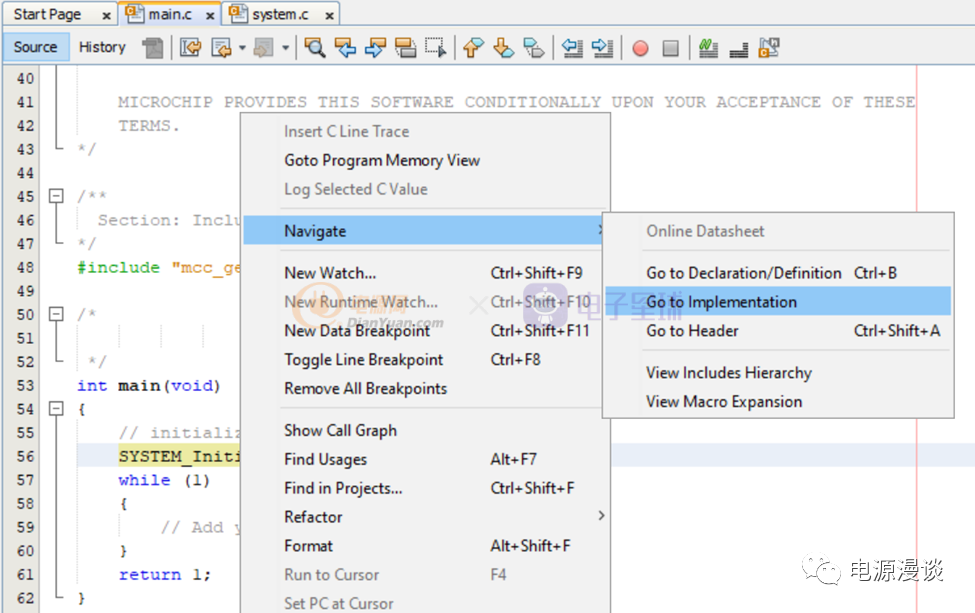

在图25所示的main函数结构中,我们可以看到除了初始化文件外,主程序没有任何任务执行,通常这些是需要根据用户的需求来添加相应的主程序软件任务。

图26 初始化函数结构

在图26截图中,我们通过右键查看初始化函数line 56的内部子函数。

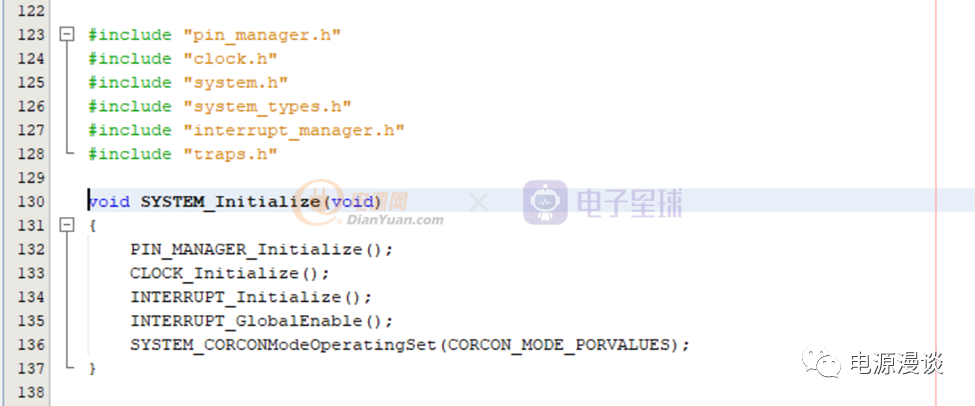

图27 初始化函数内部子函数

在图27中,我们打开了这个初始化函数,可以看到MCC自动生成了pin脚初始化,时钟初始化,中断初始化等,虽然我们在这里没有使能中断功能。

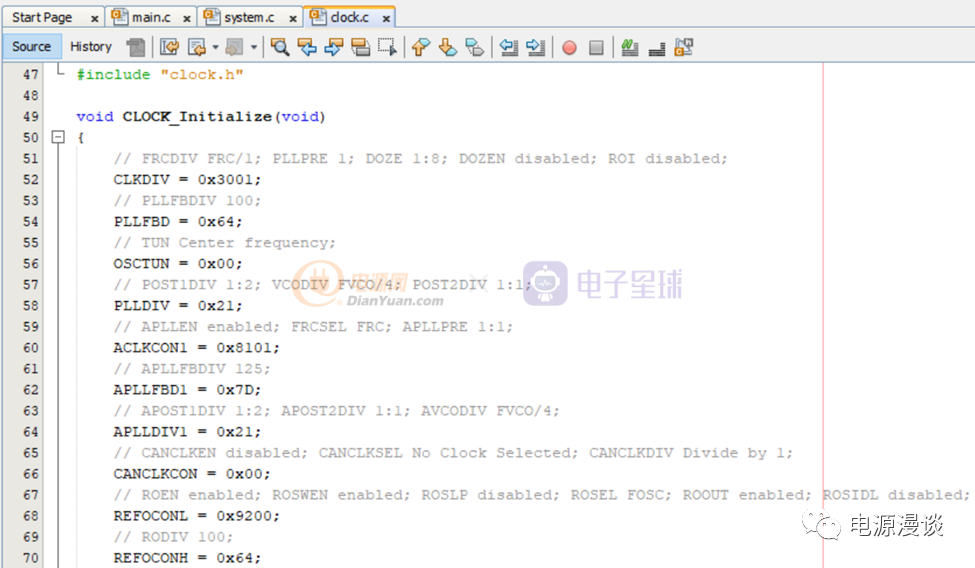

图28 时钟初始化函数

图28所示为我们配置的时钟初始化函数具体代码,它实现了PLL和APLL的配置,参考时钟输出等功能。

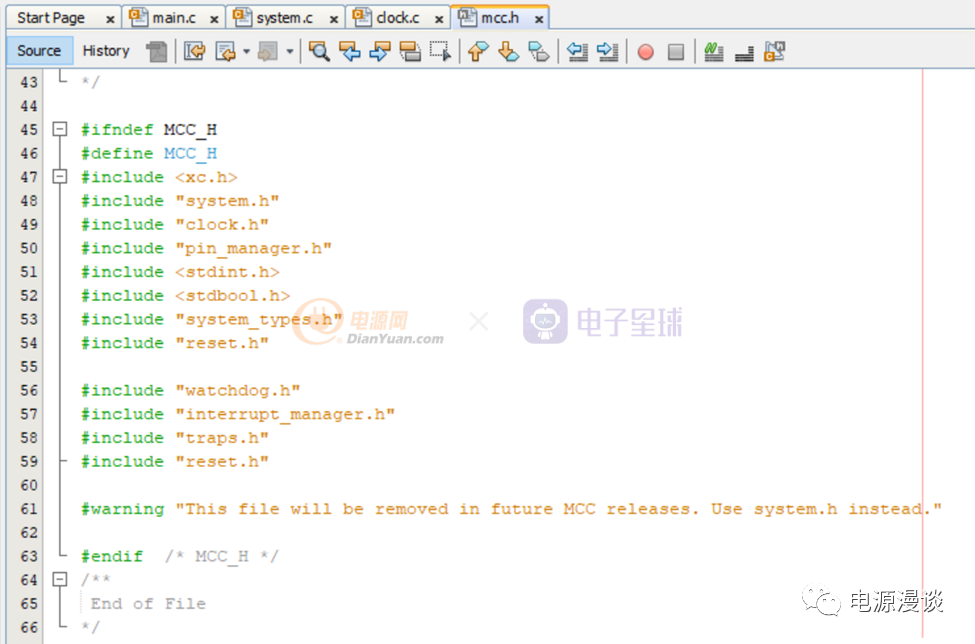

图29 MCC头文件

图29中,在mcc.h中包含所有的头文件,在需要包含时,可以包含这个mcc.h文件,而不用去分别包含每一个头文件。

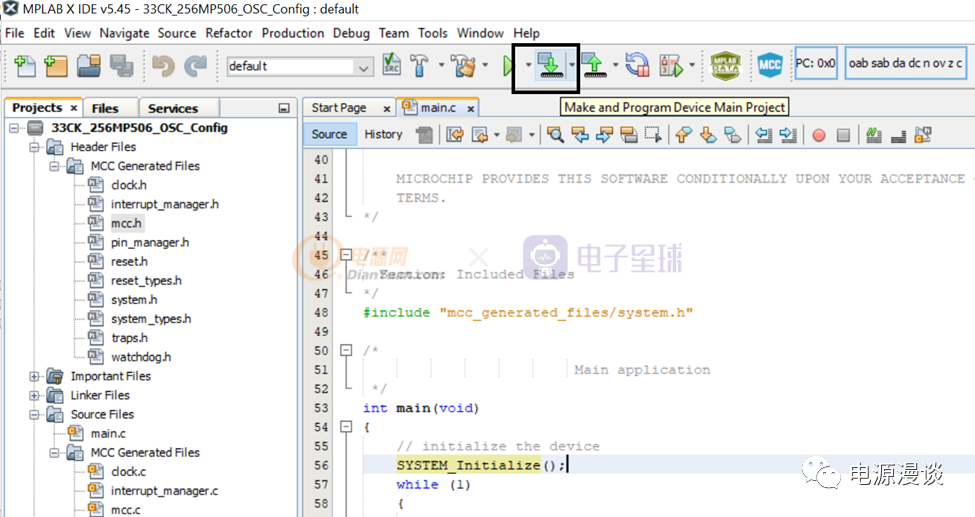

图30 烧入代码

点击图30所示的编程选项,将执行编程动作,将代码烧入芯片中去。

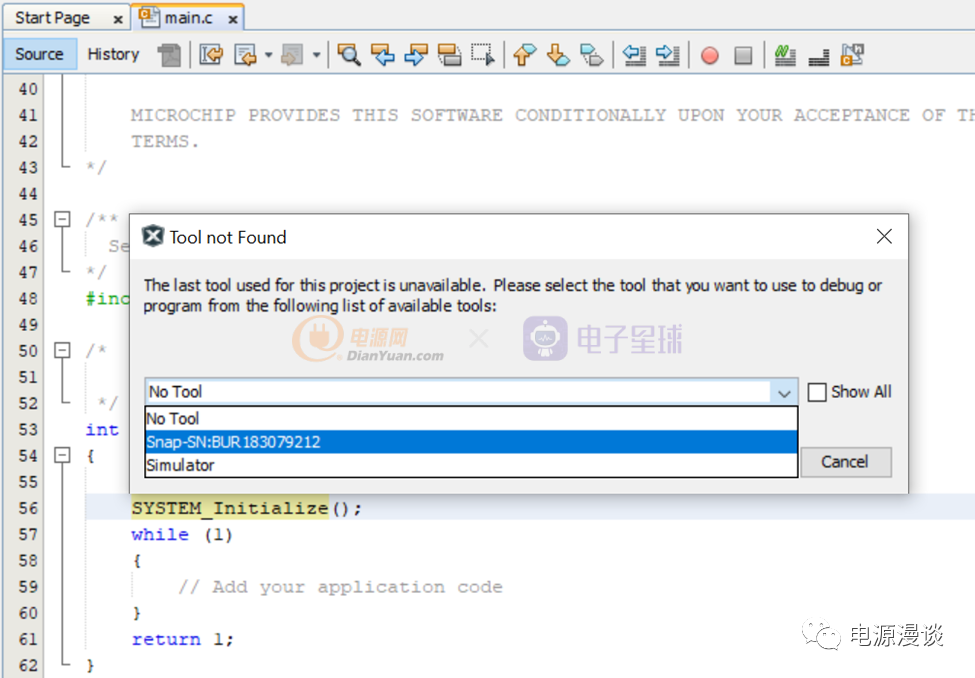

图31 编程硬件工具选择

在图31中,可以看到,当点击编程按钮后,对话框需要你选择编程工具,我这里连接了Snap工具,所以我选择Snap来实现编程。

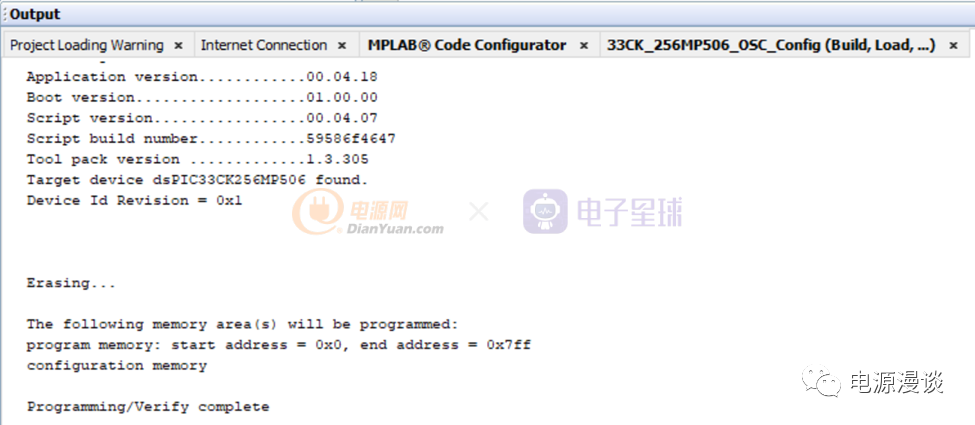

图32 编程完成

在图32所示的截图中,我们看到编程完成,可以观察波形。

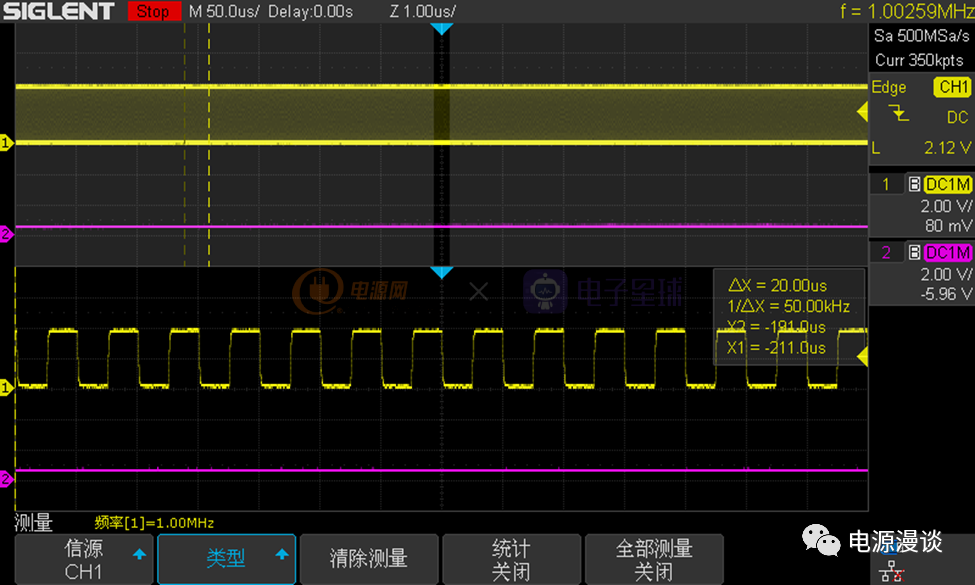

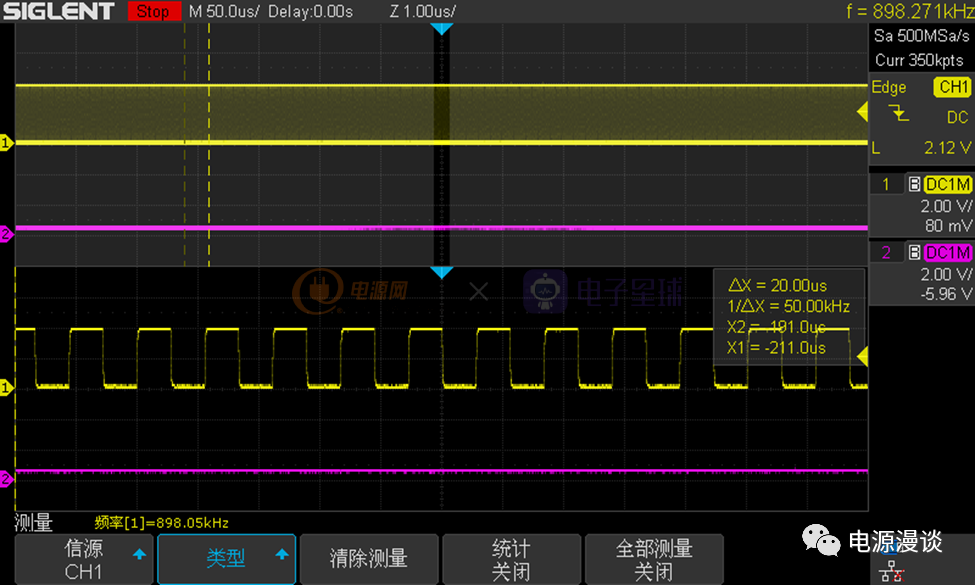

图33 参考时钟输出波形

从图33所示的参考时钟波形中可以看到,它是1个1M频率的方波,符合我们的预期,这正是200M的FOSC经过200分频比后的波形,系统时钟FOSC运行正常。

二.单核dsPIC33CK的时钟模块配置(外部20M晶振输入)

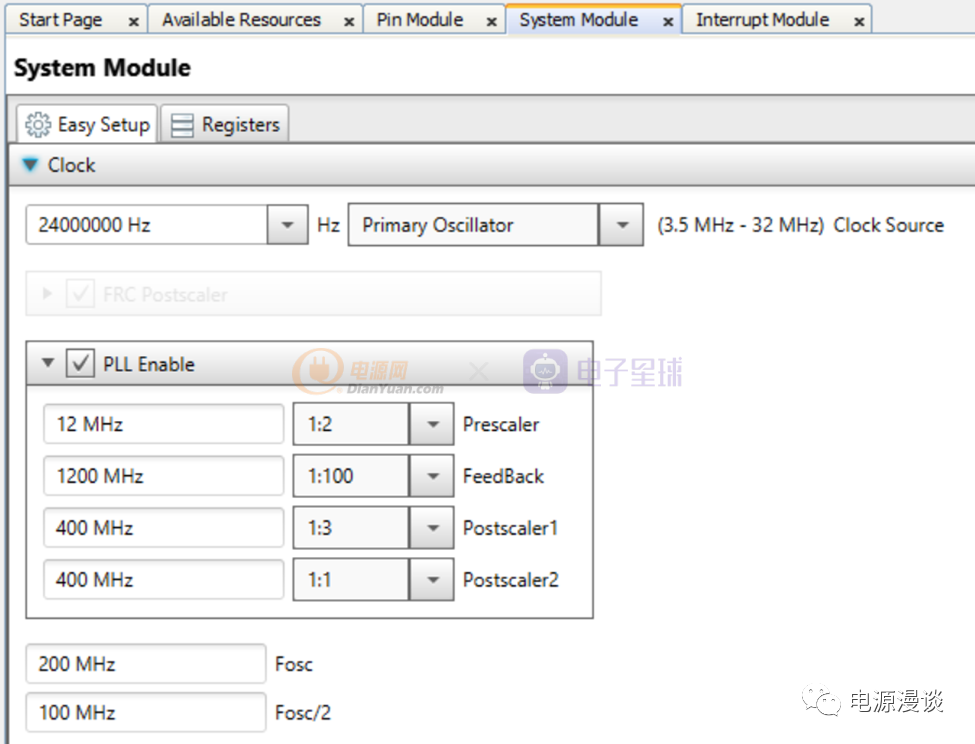

图34 外部晶振输入时PLL配置示例

当需要使用更高精度时钟源时,比如在一些需要CAN通信功能的应用中,可以使用外部晶振时钟作为PLL输入,图34所示,举例来说,采用24M频率晶振作为时钟源,则典型配置如图所示,最终得到200M的系统时钟FOSC,对应100M的指令时钟频率。这里时钟源选择Primary Oscillator,表示使用了外部振荡器为时钟源。

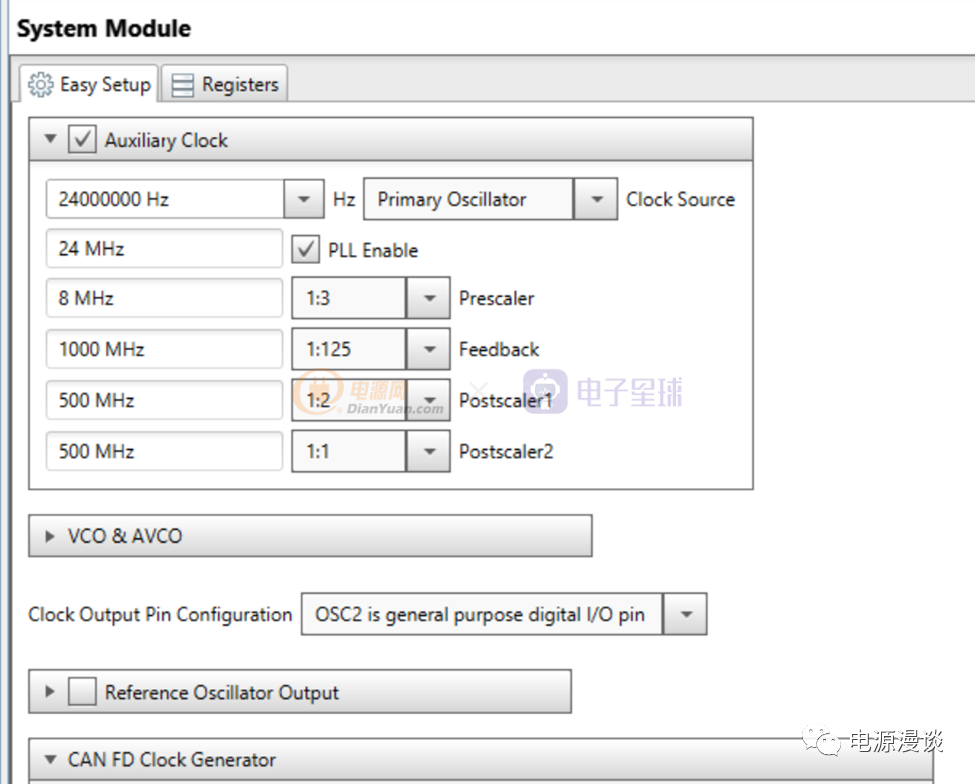

图35 外部晶振输入辅助时钟APLL配置示例

采用24M晶振输入时,同样通过一定的分频和倍频配置得到500M的APLLO输出频率,供PWM等外设使用。

此部分我们不做测试,其它配置部分参考FRC振荡器作为输入时钟时的配置。

三.双核dsPIC33CH的时钟配置(FRC作为时钟输入源)

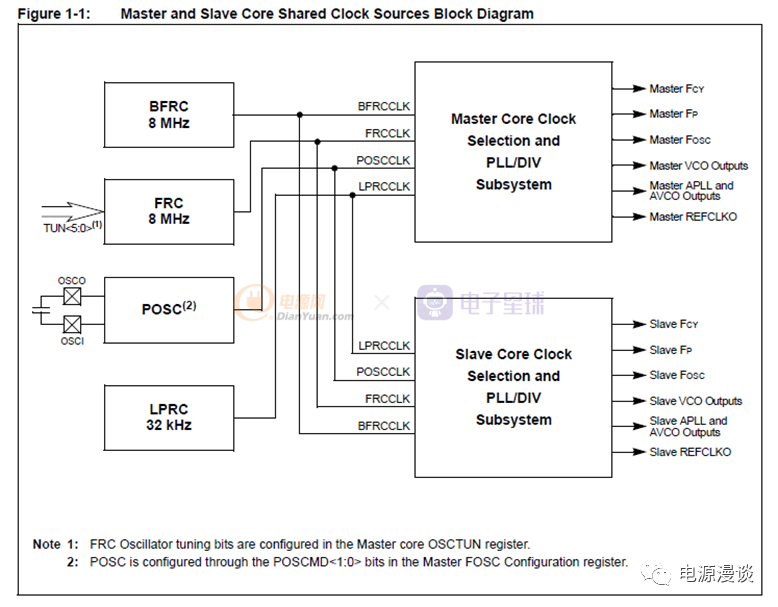

图36 dsPIC33CH双核系统的时钟架构

在图36所示的dsPIC33CH的双核时钟架构中,slave core的时钟和单核dsPIC33CK的一样,所以这里我们只对master core的时钟做一个配置介绍。

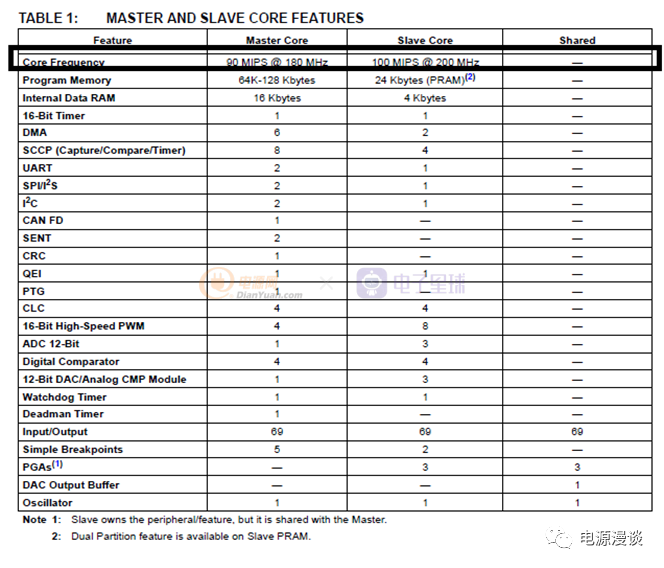

图37 dsPIC33CH的master core主频说明

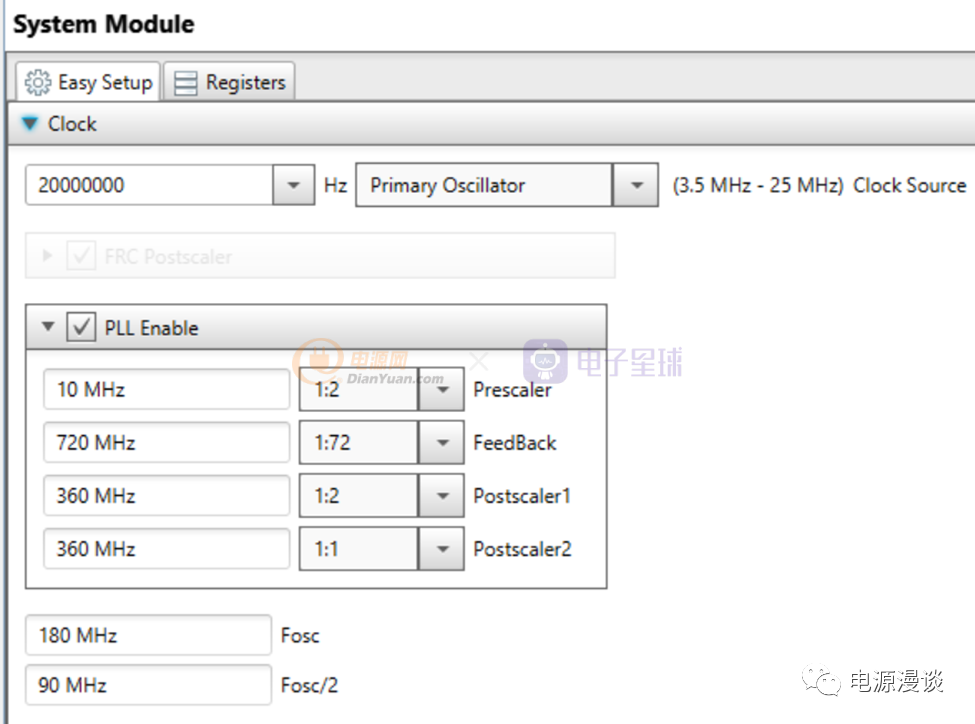

在图37 中,可以看到dsPIC33CH的master core的系统时钟FOSC最大为180M,对应90MIPS指令时钟。

图38 FRC输入master Core PLL时钟配置示例

图39 FRC输入master Core APLL输出配置示例

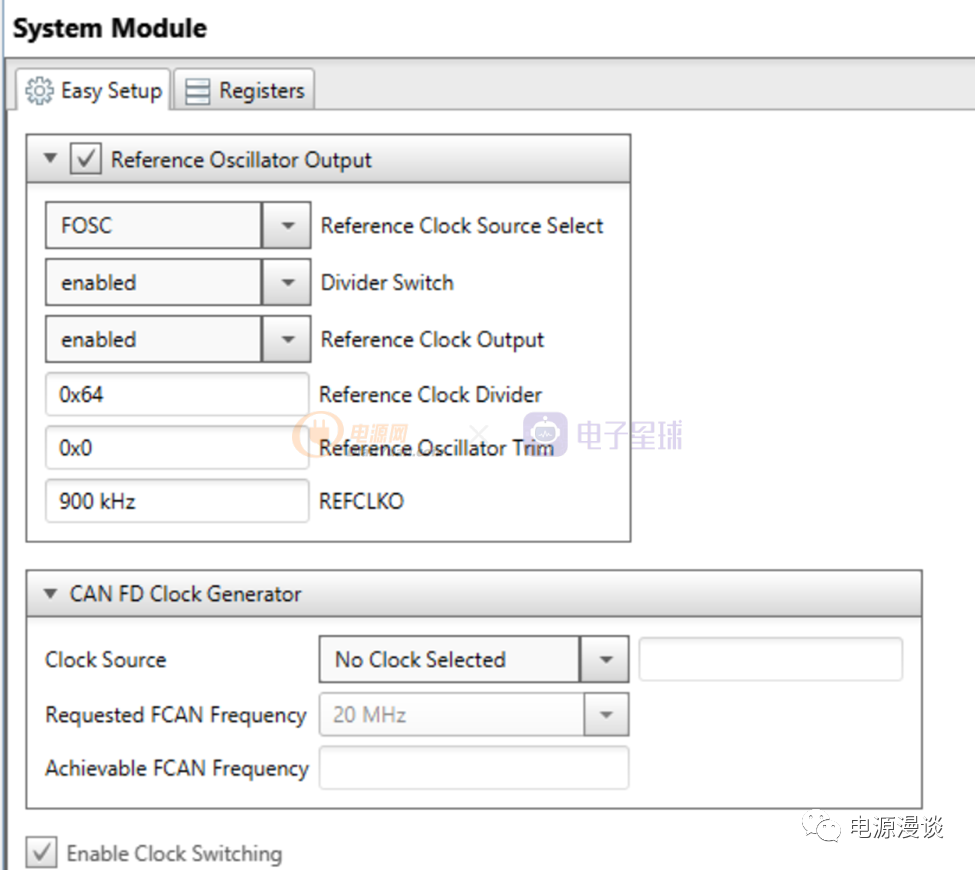

图40 FRC输入master Core参考时钟输出配置示例

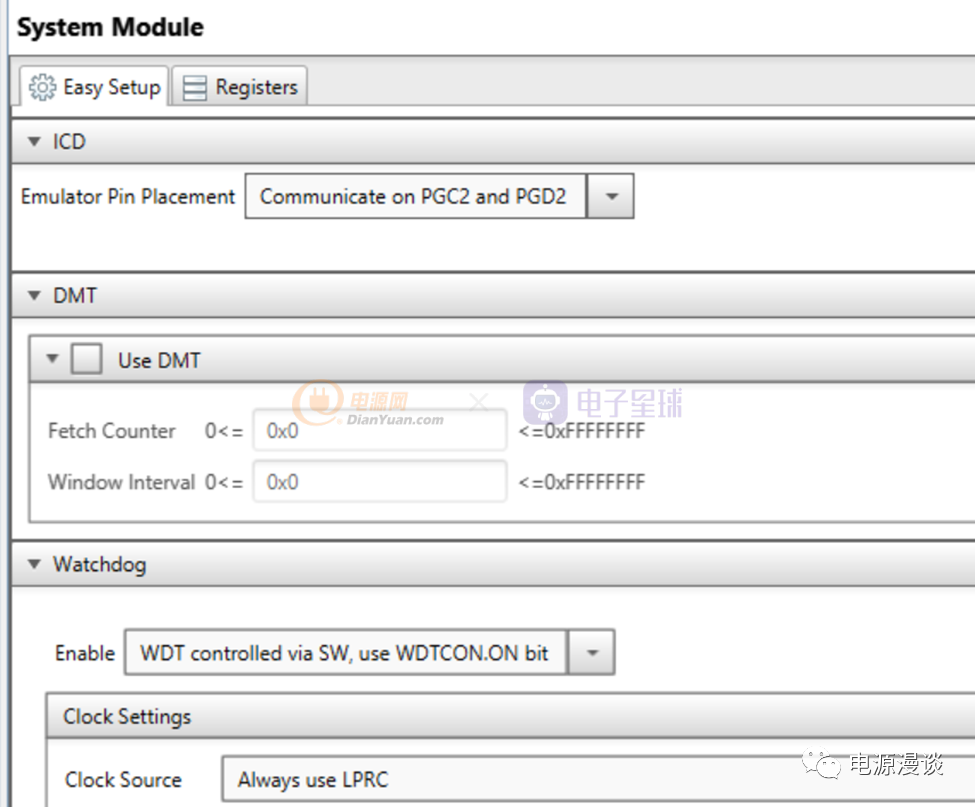

图41 FRC输入master Core编程接口配置

图42 FRC输入master Core参考时钟输出pin选择

图43 FRC输入master Core 分频后FOSC输出波形

通过以上图38-42的配置示例,在基于我们的dsPIC33CH128MP506的开发板上测试,我们同样在RC5上得到图43所示的分频后的FOSC的波形,因为FOSC为180M,经过分频比200后,得到900k频率。

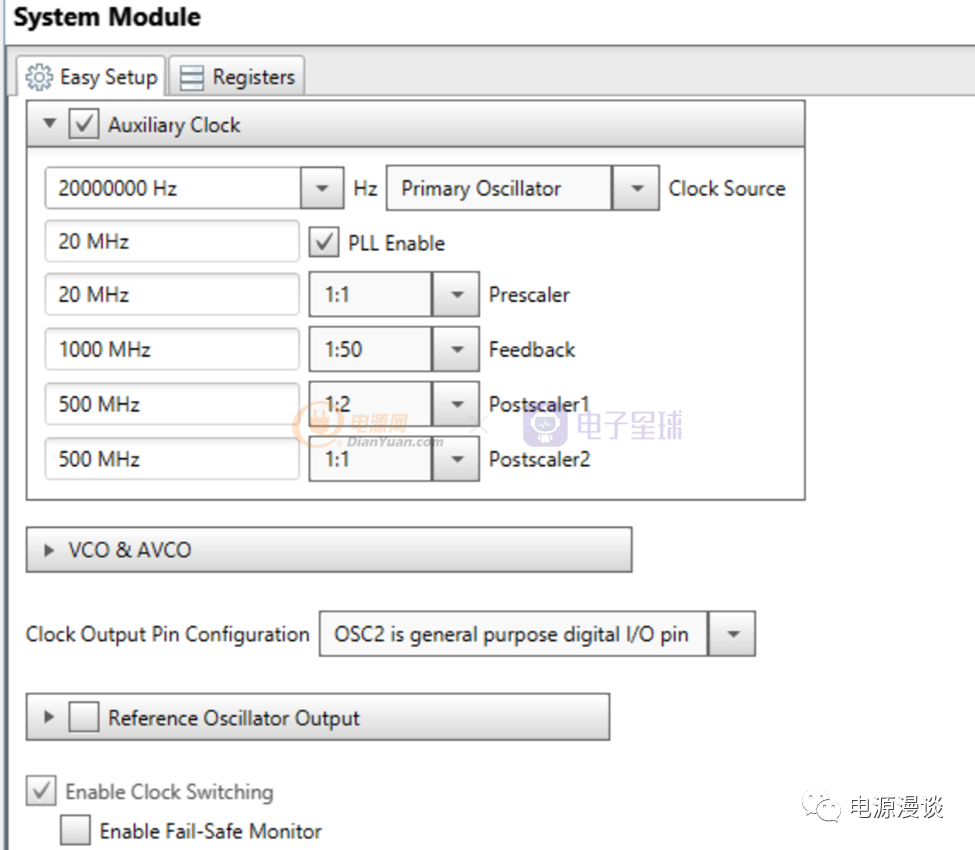

四.双核dsPIC33CH的masterCore时钟配置示例(外部晶振20M输入时)

图44 外部晶振输入双核dsPIC33CHmaster Core系统时钟配置

当需要使用更高精度时钟源时,比如在一些需要CAN通信功能的应用中,可以使用外部晶振时钟作为PLL输入,图42所示,举例来说,采用20M频率晶振作为时钟源,则典型配置如图44所示,最终得到180M的系统时钟,对应90M的指令时钟频率,这里时钟源选择Primary Oscillator,表示使用了外部时钟源。

图45 外部晶振输入双核dsPIC33CH master Core APLL时钟配置

采用20M晶振输入时,同样通过一定的分频和倍频配置得到500M的APLLO输出频率,供PWM等外设使用,如图45所示。

此处我们不做测试,其它配置部分参考FRC振荡器作为输入时钟时的配置。

总结,时钟模块是运行代码的基础,也是诸多外设运行的基础,所以我们花一定的篇幅进行说明。我们通过对数字电源控制芯片dsPIC33CK系列和dsPIC33CH系列的时钟模块进行配置及参考时钟输出测试,以说明系统能正常运行,同时也给出了外部晶振输入时的典型配置参考。