上一篇我们讲解了camera的一些基础概念和知识。 我们说了,现在的手机由于高分辨率的要求,现在基本上都是基于MIPI、CSI协议来实现的, 本篇讲解MIPI、CSI的一些基础知识。

摄像头常用术语

下面这些术语是camera驱动中经常用到的缩略语。

AE(Auto Exposure):自动曝光。

AF(Auto Focus) :自动对焦。

AWB(Auto White Balance):自动白平衡。

3A :指自动曝光(AE)、自动对焦(AF)和自动白平衡(AWB)算法。

Async Sub Device:在Media Controller结构下注册的V4L2异步子设备,例:Sensor、MIPI DPHY。

Bayer Raw(或Raw Bayer) :Bayer是相机内部的原始图片,一般后缀为.raw。.raw格式内部的存储方式有:RGGB、BGGR、GRBG等。

CIF :Rockchip芯片中的VIP模块,接收Sensor数据并保存到内存中,仅转存数据,无ISP功能。

DVP(Digital Video Port) :一种并行数据传输接口。Entity :Media Controller架构下的各节点。

Frame :帧。

HSYNC :行同步信号,HSYNC有效时,接收到的信号属于同一行。

IOMMU(Input Output Memory Management Unit):Rockchip芯片中的IOMMU模块,用于将物理上分散的内存页映射成CIF、ISP可见的连续内存。

IQ(Image Quality) :指为Bayer Raw Camera调试的IQ xml,用于3A tunning。

ISP(Image Signal Processing) :图像信号处理。

Media Controller :Linux内核中的一种媒体框架,用于拓扑结构的管理。

MIPI-DPHY :Rockchip芯片中符合MIPI-DPHY协议的控制器。

MP(Main Path):Rockchip芯片ISP驱动的一个输出节点,一般用来拍照和抓取Raw图。

PCLK(Pixel Clock) :指Sensor输出的Pixel Clock。

Pipeline :Media Controller架构的各Entity之间相互连接形成的链路。

SP(Self Patch) :Rockchip芯片ISP驱动的一个输出节点。

V4L2(Video4Linux2) :指Linux内核的视频处理模块。

VICAP(Video Capture) :视频捕获。

VIP(Video Input Processor):在Rockchip芯片中,曾作为CIF的别名。

VSYNC :场同步信号,VSYNC有效时,接收到的信号属于同一帧。

一、基础概念

1. MIPI

MIPI:移动产业处理器接口(Mobile Industry Processorinterface) 是MIPI联盟发起的为移动应用处理器制定的开放标准。

MIPI官网

https://www.mipi.orgMIPI联盟 即移动产业处理器接口(MIPI)联盟,由美国德州仪器(TI)、 意法半导体(ST)、 英国ARM和芬兰诺基亚(Nokia)4家公司共同成立, 旨在定义并推广用于移动应用处理器接口的开放标准。

2. CSI

MIPI-CSI-2协议是MIPI联盟协议的子协议,专门针对摄像头芯片的接口而设计。

由于其高速,低功耗的特点,MIPI-CSI2协议极大的支持了高清摄像头领域的发展.

正是由于它的普及,手机上五百万像素的摄像头才得以变为前置摄像头,该类接口技术主要掌握在日本东芝,韩国三星以及美国豪威三家公司。

- CSI协议有两个版本协议,分别为CSI-2和CSI-3;

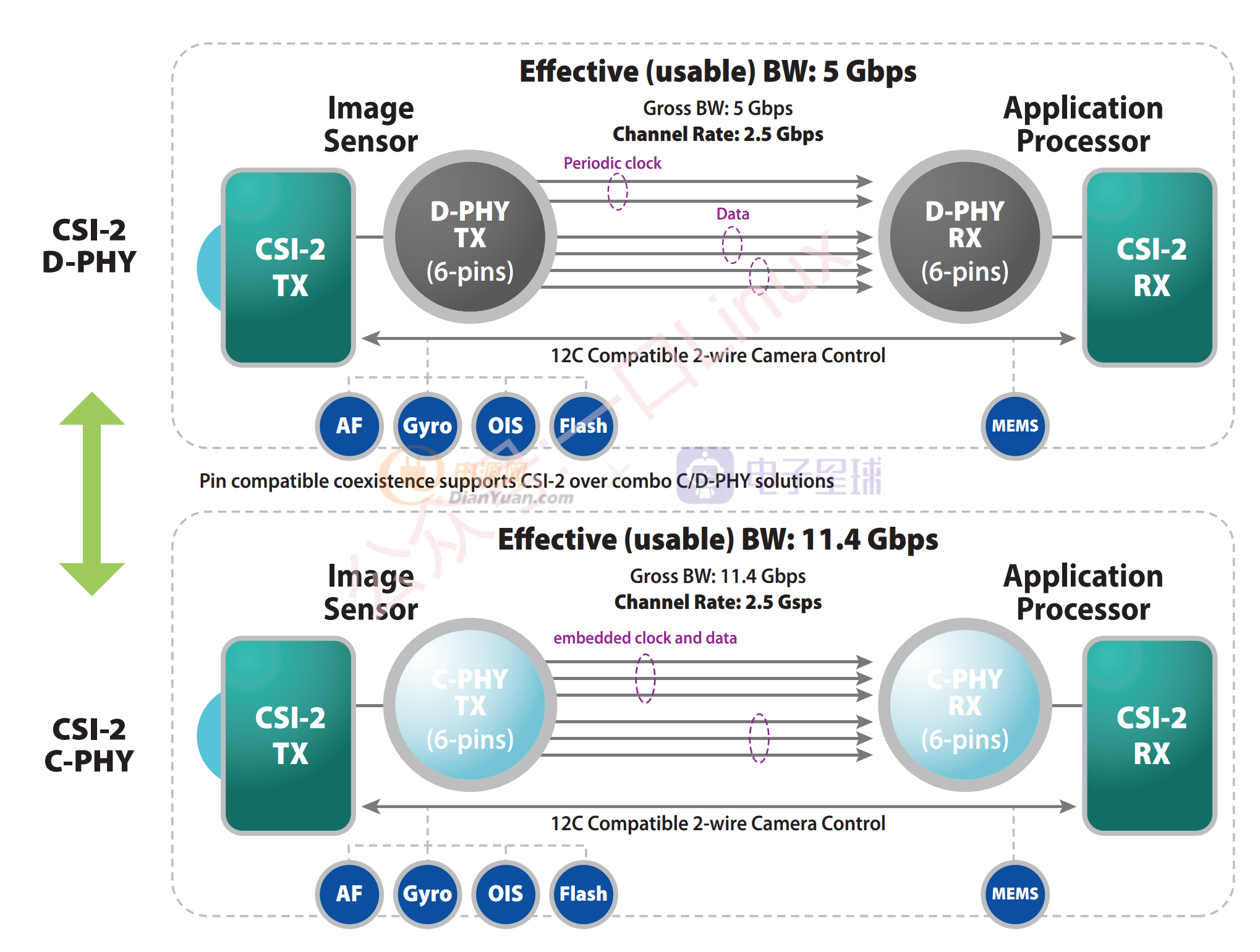

- CSI-2协议遵循的物理标准有两个,分别为C-PHY和D-PHY;

- CSI-3协议的物理标准对应M-PHY,且应用层协议栈还需要连接Uni-Pro层。

D-PHY与C-PHY区别: 从实用角度来看,主要是数据线和时钟线的区别,还有传输速率,C-PHY通过某些技术改良,使数据传输速度更快。

瑞芯微3568用的CSI-2 && D-PHY

所以内核中,我们会看到CSI2 和 D-PHY相关代码。

二、MIPI协议

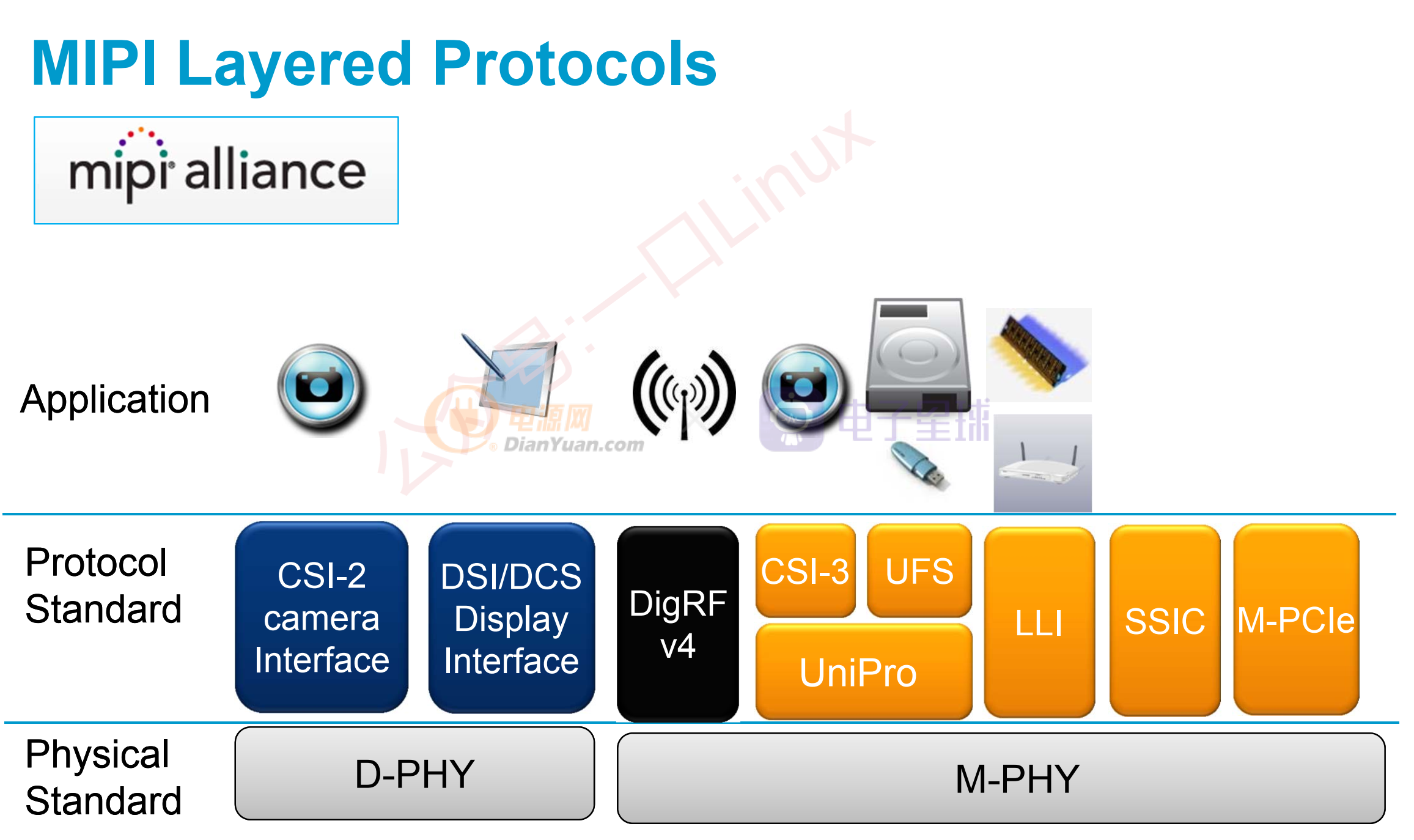

MIPI并不是一个单一的接口或协议,而是包含了一套协议和标准,以满足各种子系统独特的要求。MIPI的标准异常复杂,包含非常多的应用领域。

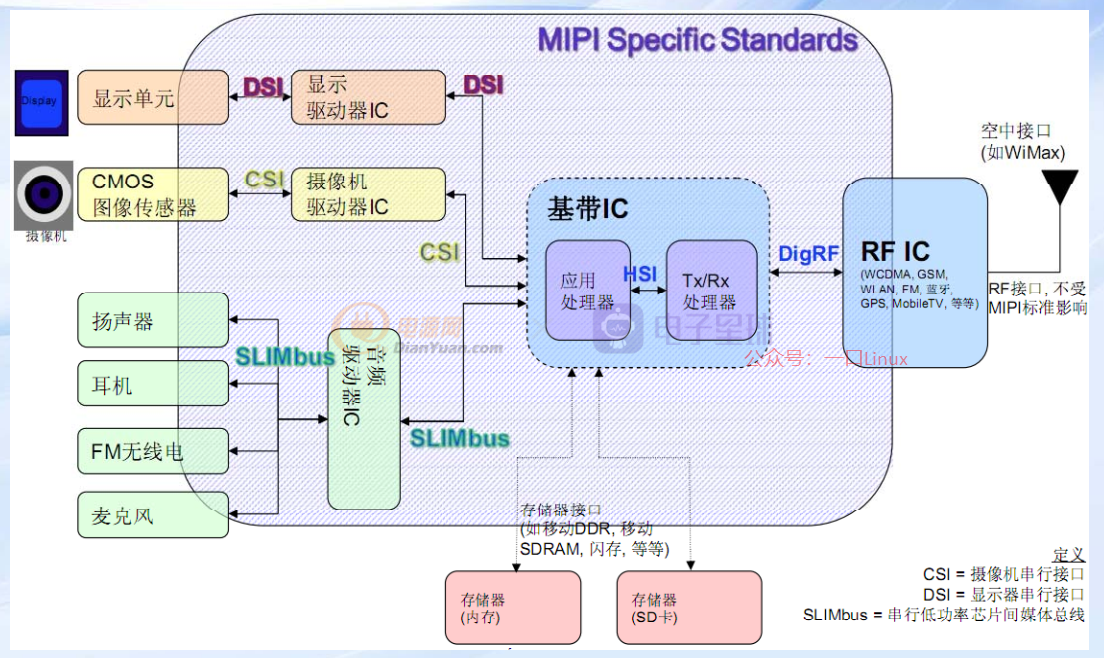

由上图可得:

- 显示设备采用的DSI协议

- 摄像头采用的CSI协议

- RF IC采用的DigRF协议

- 存储设备采用的UFS

1. DCS(Display Command Set)

用于显示模块命令模式下的标准化命令集;

2. DBI, DPI (Display Bus Interface, Display Pixel Interface)

DBI:与具有显示控制器和帧缓冲器的显示模块的并行接口。 DPI:与显示模块的并行接口,不带显示控制器或帧缓冲器。

3. DSI, CSI (Display Serial Interface, Camera Serial Interface)

DSI:主机处理器与显示模块之间的高速串行接口; CSI:主机处理器与摄像头模块之间的高速串行接口;

4. D-PHY

为DSI(显示屏)和CSI-2(摄像头)提供物理层通路定义。

5. M-PHY

为DigRF、CSI-3、UFS、LLI、SSIC、M-PCIE提供物理层通路定义。

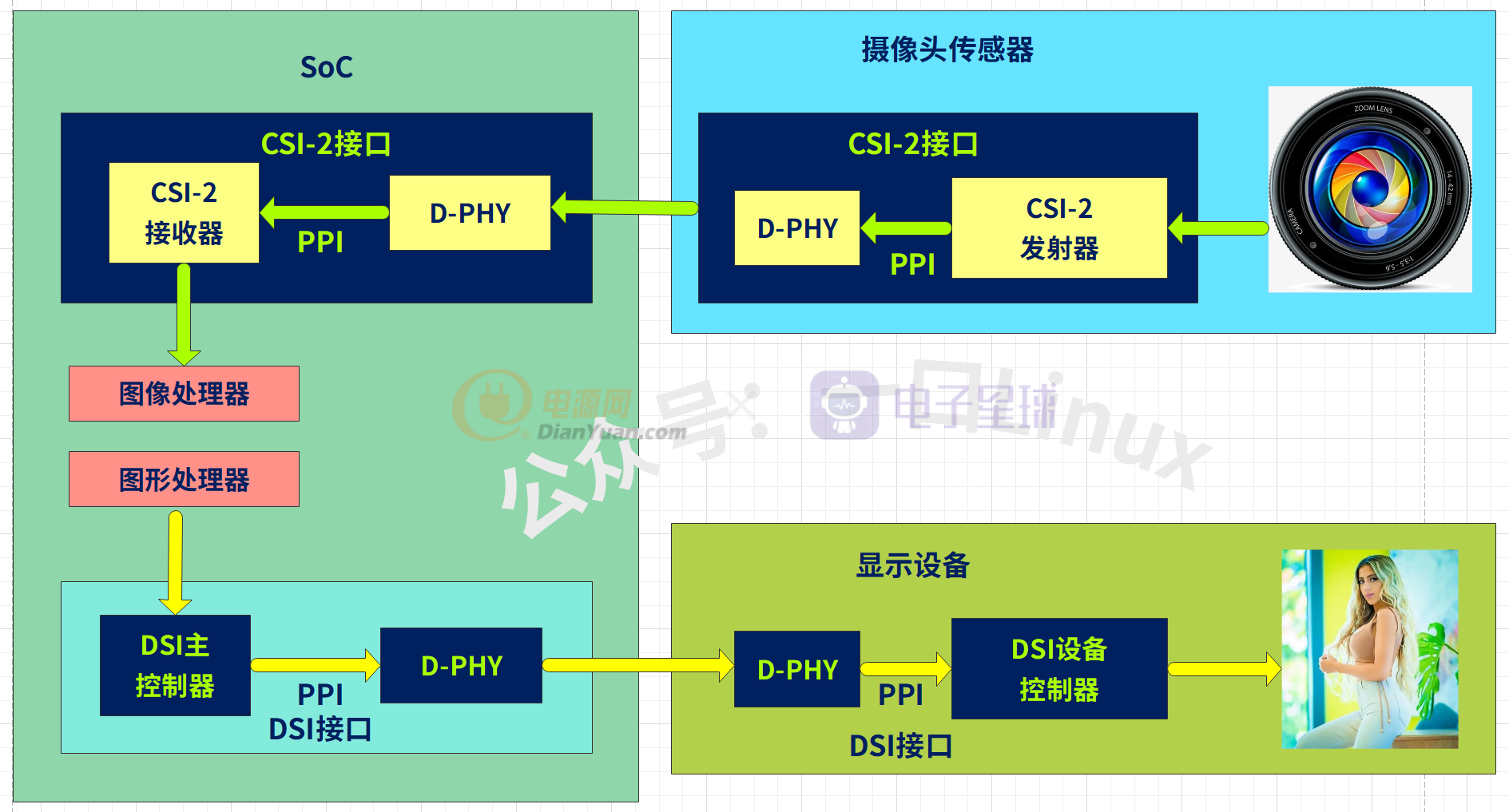

目前比较成熟的接口应用有**DSI(显示接口),和CSI(摄像头接口)**,都具有比较复杂的协议结构,下图表示某一个SOC可以作为一个CSI的接收器,同时也可以作为一个DSI的输出器。

其物理层使用到了D-PHY,目前新的物理层C-PHY也逐渐被采用,我们常说的Camera I2C接口在MIPI中有专门的一个CCI(Camera Control Interface)来对应。

三、CSI

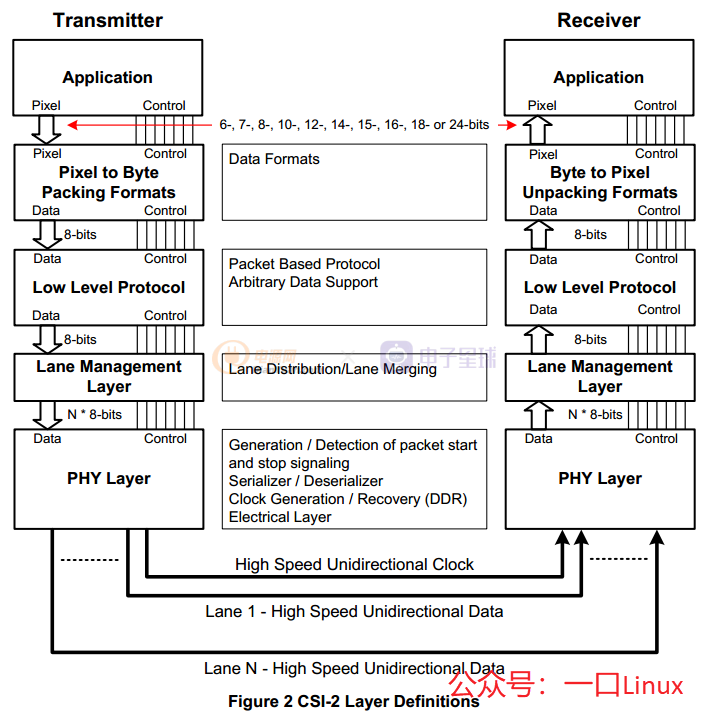

根据层级,CSI协议分为五层:

名称 解释 Application 应用层 处理原始图像数据的各种算法模块 Packing Formats 组包层 负责将数据按照一定的次序,切割成8bite数据 Low Level Protocaol 协议层 为新生成的数据加上爆头包尾,形成符合协议要求的数据流 Lane Management 通道管理层 将生成的数据流按照一定次序和要求,进行读写管理,输出数据流 PHY Layer PHY层 生成MIPI最后的信号波形 Pixel 像素数据 经过图像模块处理过的数据流,或者原始的图像数据流 Data 传输数据 经过MIPI模块切割或者加上包头包尾数据 Control 控制信号 模块间的控制数据流 Transmitter 发送端 包括了MIPI数组部分,转接板等实现MIPI信源传输的部分 Receiver 接收端 包括了转接板和商用接收端模块,负责解析收到的MIPI信源

工作顺序:

- 将原始的图像数据在应用层做相应的图像处理,包括白平衡/噪声去除和色彩还原等;

- 将处理的数据进入组包层做数据分割以及重组,然后将其传输给底层协议层;

- 底层协议层会根据数据类型产生包头,根据数据内容产生构成包围的校验序列,再将包头、数据本身和包尾组成起来发送给通道管理层;

- 通道管理层模块按照通道的选通情况,合理分配数据到每个通道,之后数据经过数模转换进入到物理层传输;

- 接收端在收到物理层数据后,再按照之前的逆序解包出原始的图像数据。

1. 应用层(Application Layer)

该层主要用于不同场景对数据的处理过程,对于发送方,多为camera生成数据,对于接收方,多为SOC对数据进行处理。

2. 协议层(Protocol Layer)

CSI-2协议可以使用SOC上的一个物理接口实现多条数据流的传输。协议层规定了如何对多条数据流进行标记和交织,从而使每条数据流能够正确地重建。

1)像素字节转换层(Pixel/Byte Packing/Unpacking Layer)

CSI-2能够支持多种多样的像素格式,对于发送方,在数据发送之前,需要根据像素格式,将像素数据转换为对应的字节流;对于接收方,在将数据提供给应用层之前,需要将字节流数据转换为像素数据。

2)低级协议层(Low Level Protocol)

LLP指的是SoT与EoT之间的数据包字节流协议,LLP的最小单元为字节。

3)Lane管理器(Lane Management)

为了适应不同场景下对带宽的要求,CSI-2规定了Lane的数量是可拓展的。因此,在面临多Lane同时传输时,发送方需要对字节流进行公平分流(distributor),接收方则需要对多Lane数据进行合并(merger)。

3. 物理层(PHY Layer)

PHY层指定了传输媒介,在电气层面从串行bit流中捕捉“0”与“1”,同时生成SoT与EoT等信号。 CSI的硬件部分包括C-PHY、D-PHY,实际上使用的主要是D-PHY。

四、物理层 DPHY

D-PHY 描述了一同步、高速、低功耗、低代价的PHY。

D-PHY的最初版本设计目标是500M bits/s,而D是罗马数字的500,故而叫D-PHY。

1. D-PHY规范的2.0版的标准:

- 在高速模式下的同步传输,比特率为80-2300Mb/s,具体取决于设备和速度等级;

- TX经典配置为一个时钟Lane和最多四个数据Lane组成;

- Rx经典配置为一个时钟Lane和最多八个数据Lane组成;

- 在低功率模式下的异步传输,比特率为10Mb/s;

- 物理协议接口(PPI)连接CSI-2和DSI的应用;

- 可选的AXI4-Lite接口,可进行注册访问。

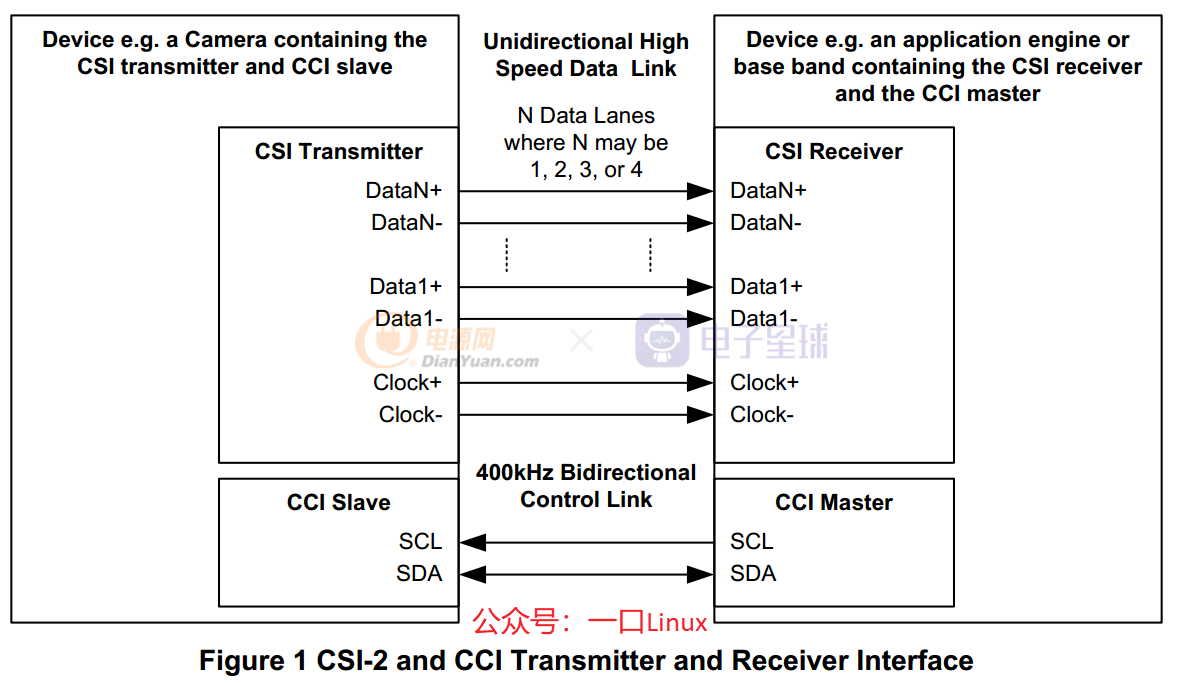

上图表明使用DPHY作为物理层时,Camera与SOC之间的硬件关系。

MIPI CSI设备由两部分构成,分别为CCI(Camera Control Interface)和CSI(Camera Serial Interface)。

- CCI:摄像头控制接口。(在MIPI中,充当着控制接口的作用,提供mipi接口sensor的控制传输通道)

- CSI:主机处理器与摄像头模块之间的高速串行接口(传输图像数据)。

- SOC的CCI组件通过I2C完成对Camera的配置,使其输出mipi信号

- 其中一对Clock+/-则由Clock Lane标示,

- 一对DataNBA+/-则由Data Lane标示。

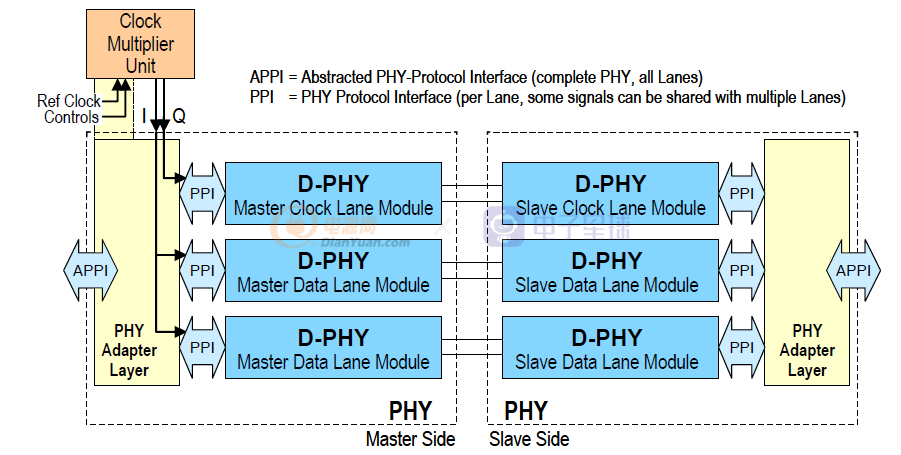

两个Lane的 PHY配置如下图 :

2. CCI (Camera Control Interface)

CCI是一个双线、双向、半双工、串行接口。是I2C协议的子集,与I2C基本一致。

CCI是兼容I2C接口的快速模式变体。CCI应支持400kHz操作和7位从属寻址。

对于那些只支持RAW Bayer输出格式的摄像头,其CCI地址必须为011011xb(x=0,1);对于其他的摄像头,其CCI地址必须为011110xb。

CCI可选择支持速率: 1Mbps (Fm+), 12.5Mbps (SDR), or 25Mbps (DDR).

CCI接口命名如下:

- CCI (I2C) : CCI 支持I2C

- CCI (I3C) :CCI 支持I3C

- CCI (I3C SDR) :CCI 支持I3C SDR

- CCI (I3C DDR) :CCI 支持I3C DDR

- CCI :表示同时支持 CCI (I2C) 和CCI (I3C).

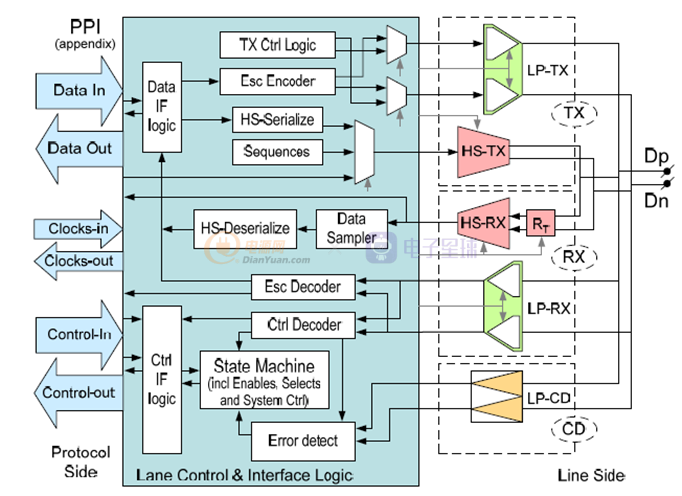

3. DPHY工作于两种工作模式:

- HS(High Speed Mode) 这种模式用于传输高速的数据信号,如视频流;高速模式下,每对Lane都是工作在低电压摆幅的差分状态下,数据速率为80Mbps到1500Mbps。

- LP(Low Power Mode) 这种模式则可以用来传输控制信号;低速模式下,每对lane的2根导线都转变为单端状态,数据速率为10Mbps。

上图为单个Lane模块的内部组成,包含了CIL(Lane控制器与借口逻辑器),LP驱动器,HS驱动器,LP冲突检测。

CIL负责控制各个驱动器的工作状态,使得Dp、Dn的工作状态可以在HS与LP之间进行切换。

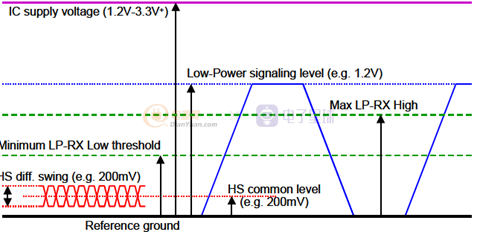

处于HS模式下,差分信号电平摆幅约为200mV;处于LP模式下,单端信号电平摆幅约为1.2V。 在LP模式下,根据各个Line的电平可以确定当前Lane的State。

Data Lane差分线电平的高低表明了当前处于何种状态,发送方通过驱动差分线一系列的状态变化,进入不同的工作模式。

- Burst Mode: High-Speed下的唯一模式,高速数据传输模式,此时各个Lane的Line工作在差分模式

- Control Mode: Low Power下的一种模式,可以通过变化不同的state进入其他模式。

- Escape Mode: Low Power下的特殊模式,在这种模式下可以使用一些特别的功能。

4. CSI-2数据帧格式

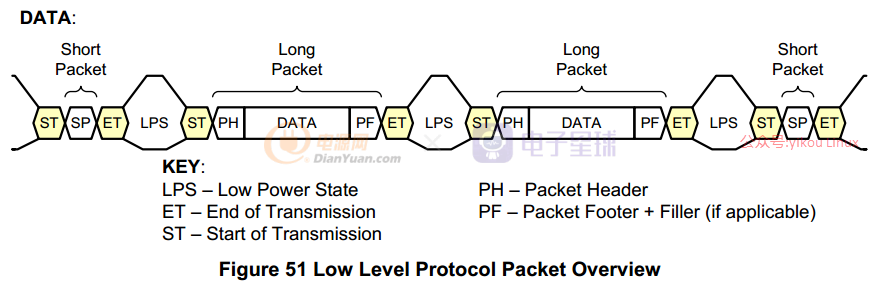

CSI-2的数据包有两种:长帧和短帧。无论长帧还是短帧,帧开头都是SoT,帧结尾都是EoT。在两次HS传输过之间,插入的是LP状态,一般是LP11等Control状态,当然也可以进入Escape状态、进入LPDT或者是进入UPLS。

1) 长帧结构如下

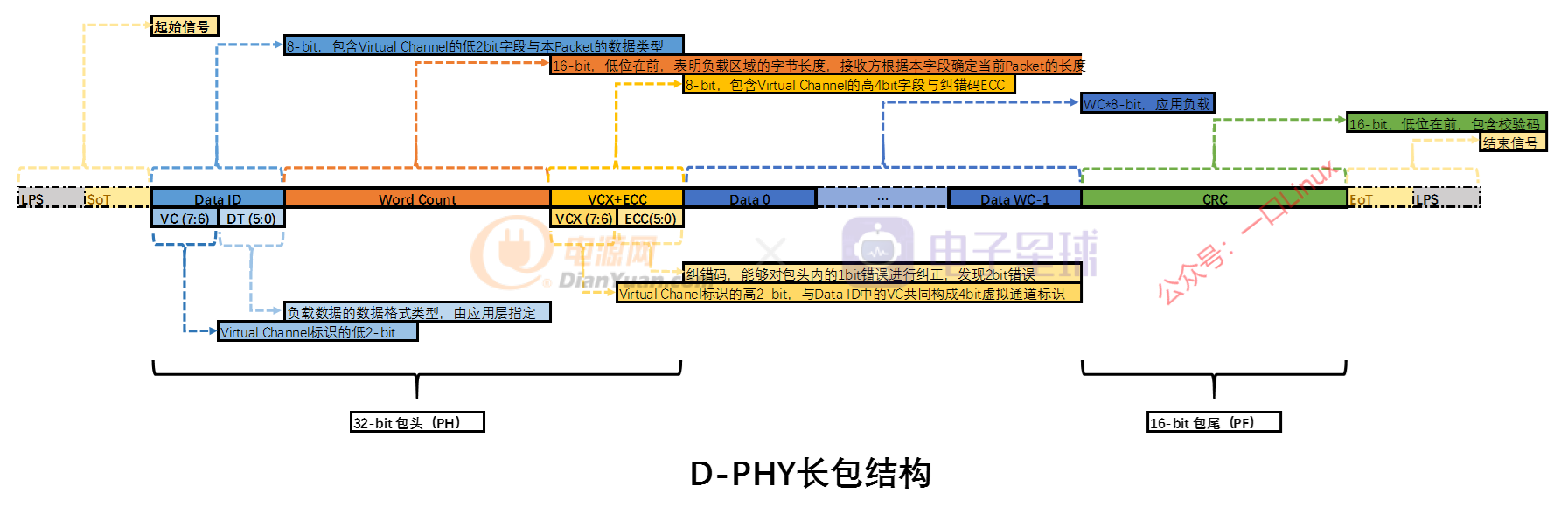

以DPHY为例来分析具体的协议格式,DPHY长包主要由包头、包负载、包尾三部分组成,具体如下图:

长帧包括32bit的包头(Packet Head,PH)、有效数据填充以及16bit的包尾(Packet Foot,PF)。

- PH包括:

数据标识(Data Identity,DI):1个字节,包括VC(Victual Channel)低两位和DT(Data Type)的低六位; 数据计数(Word Count,WC):2个字节。从PH结尾到PF的开头中间的填充数据的长度,单位为字节。接收端通过WC来判断报的结尾位置。 错误检测(ECC):1个字节。包括VC的高两位,与DI中的VC低两位构成4bit虚拟通道标识;低6位为纠错码,采用Hamming(汉明码)的方式,用来纠正PH中一位的错误或者发现两位的错误;

-

有效数据填充: 长度=WC*8bit。低位在前,对内容没有任何限制(0~65535字节)。

-

PF包括: 检验(CHECKSUM):两个字节。低位在前,CHECKSUM采用CCITT的16-bit的CRC校验,即X16+X12+X5+X0。CRC只能检测出一个或多个错误,并不能纠正错误。

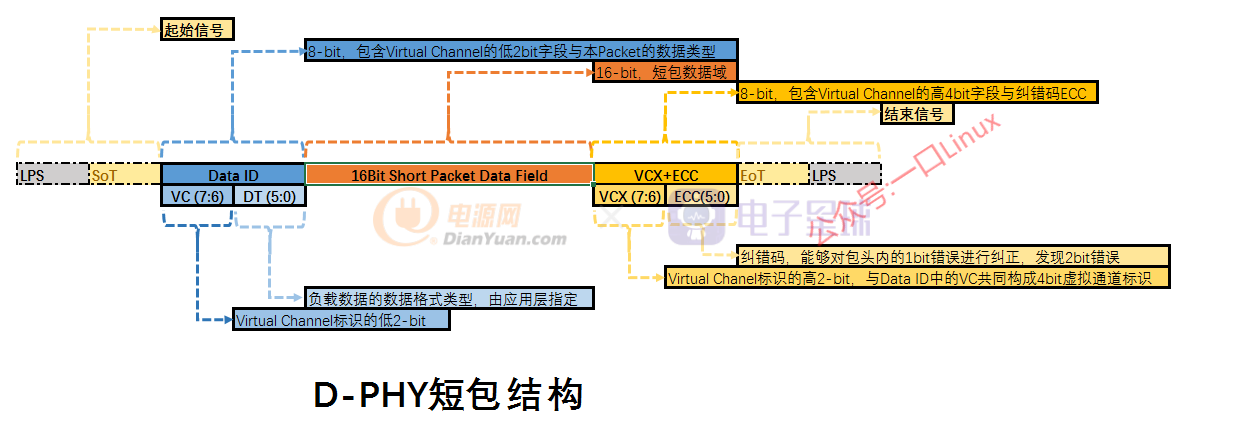

2) 短帧结构如下:

DI:1个字节,包括VC的低两位,和DT(5:0);

短包数据域:2个字节,如果该短帧为Data Type的帧同步(Frame Synchronization),则数据域表示帧数;如果短帧的Data Type为行同步(Line Synchronization),则数据域表示行数。

错误检测(ECC):1个字节,包括VC的高两位和六位纠错码。

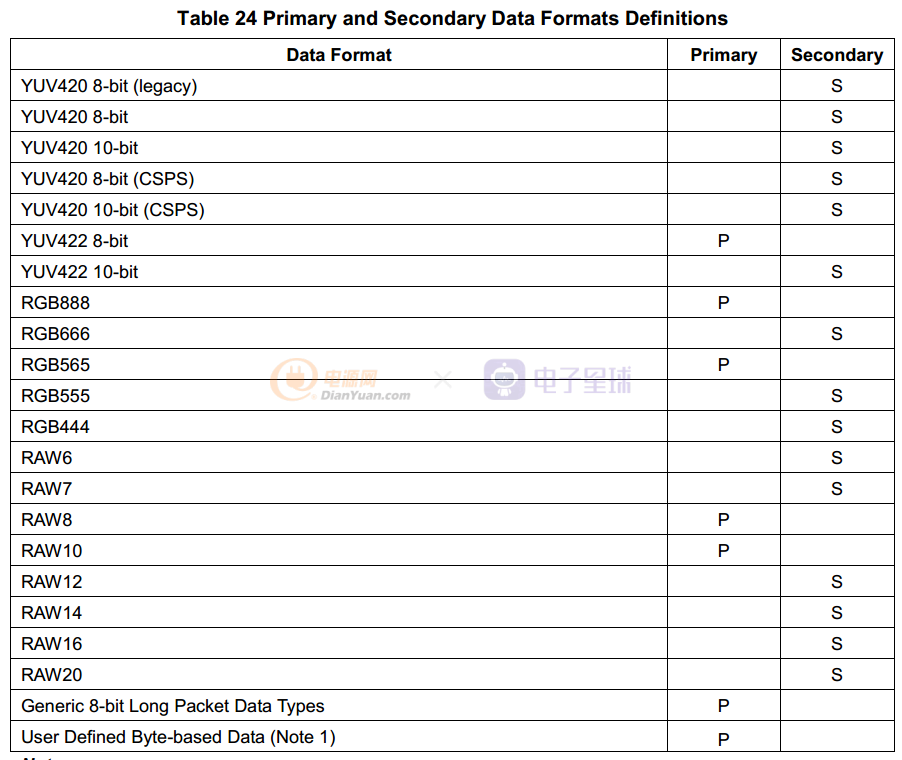

- 数据类型 数据类型表明了负载数据的格式和内容,上文提到,根据长短包的不同,数据类型共有8种不同的分类。短包数据类型的详细信息在上文已经介绍了,这里说明下长包的5种数据类型,详见下表:

数据类型举例:

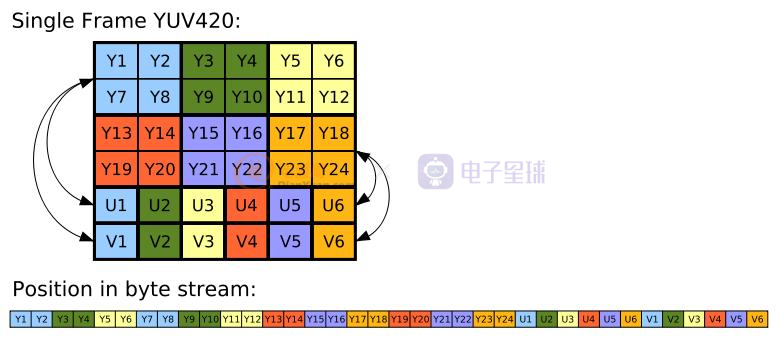

比如YUV420格式: 4:2:0表示2:1的水平取样,垂直2:1采样(每四个Y共用一组UV分量) 数据格式如图所示:

关于DPHY层,我们并不需要关注太多,就像网卡的PHY层一样,我们只需要知道,通过CCI接口发送配置信息给Camera,通过CSI接口传输数据。

五、MIPI协议在手机中应用

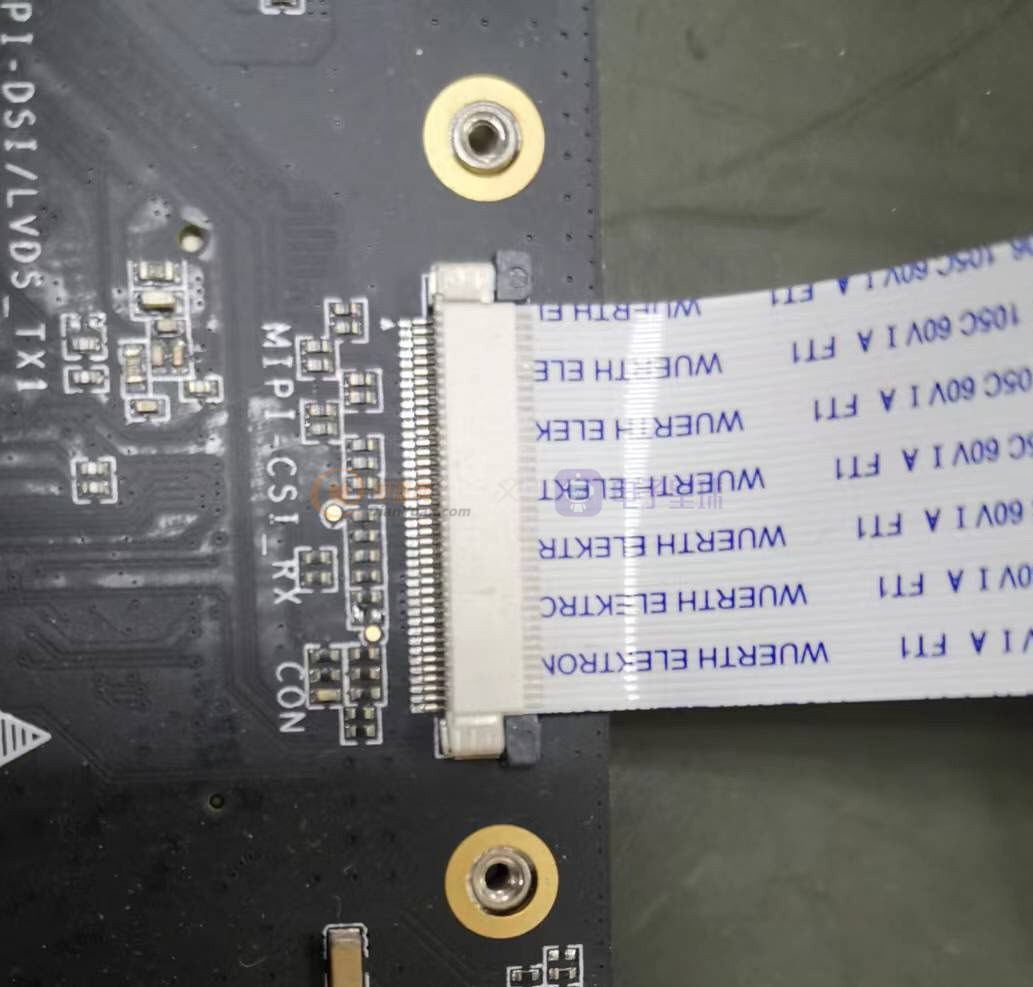

1. mipi插槽

MIPI摄像头:

通常手机不会设计这个扩展槽,一般都会直接在板子上预留小的排线接口,直接将摄像头模组插上去即可。

2. MIPI接口的手机内部功能框图

在手机内部,各个部件与MIPI协议栈的关系如下图:

其中摄像头通过CSI与处理器相连。

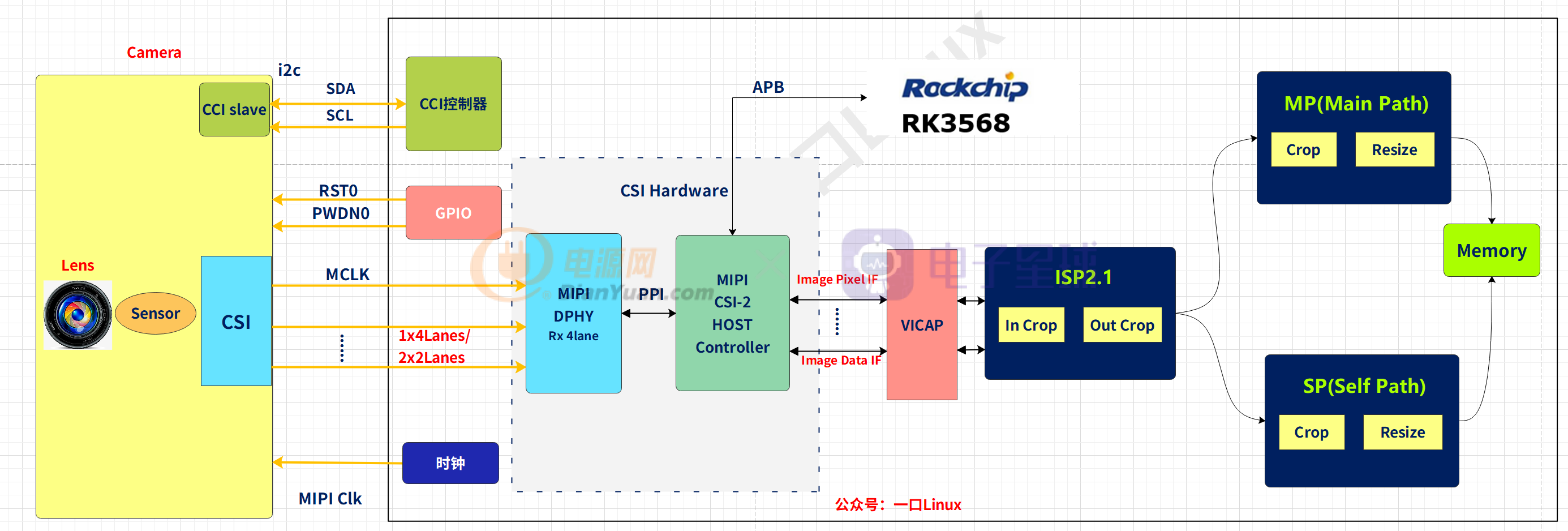

我们再细化下摄像头与cpu的模块图【以瑞芯微rk3568为例】:

MIPI接口在系统的实现如上图所示,

- 通常一个camera的模组如图所示,通常包括Lens、Sensor、CSI接口等,其中CSI接口用于视频数据的传 输;

- SoC的Mipi接口对接Camera,并通过I2C/SPI控制camera模组;

- MIPI DPHY提供了4 Lane的Rx接口,由Sensor提供Clock,并通过四条数据Lane输入图像数据;

- DPHY与CSI-2 Host Contrller之间通过PPI(PHY-Protocol Interface)相连,该接口包括了控制,数据,时钟等多条信号

- CSI-2 Host Contrller通过PPI接口收到数据后进行解析,完成后通过IDI(Image Data Interface)或者IPI(Image Pixel Interface)输出到SoC的其他模块(VICAP或ISP,rk3568是送至VICAP模块);

- ISP将处理过的图片输出到MP主通道或SP自身通道,SP一般用来预览图片,SP图片的最大分辨率比MP低;

- SoC通过APB Slave总线控制CSI-2 Host Contrller的相关寄存器。

ISP含义

ISP(Image Signal Processor),即图像信号处理器,用于处理图像信号传感器输出的图像信号。

它在相机系统中占有核心主导的地位,是构成相机的重要设备。ISP 通过一系列数字图像处理算法完成对数字图像的效果处理。

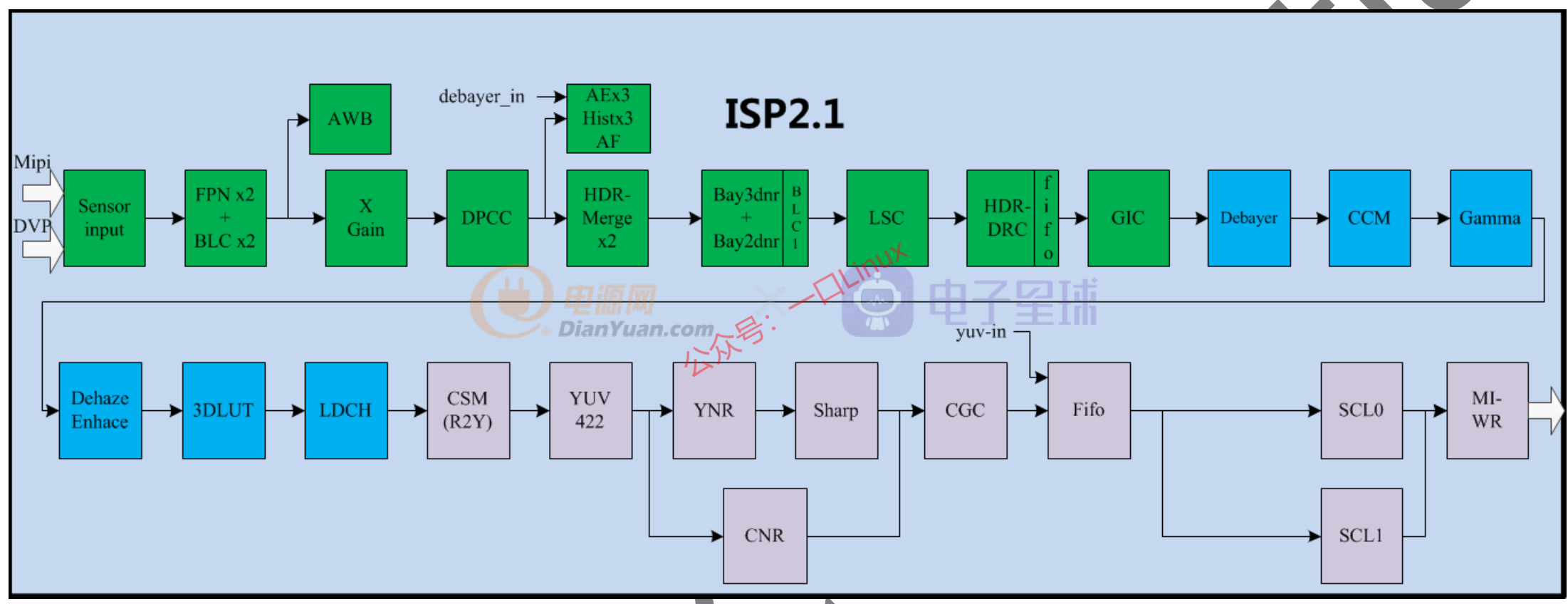

瑞芯微rk3568平台的ISP2.1 处理图像数据的基本流程如下:

ISP 包括:

- MIPI serial camera interface(MIPI)

- RAW Processing

- RGB Processing

- YUV Processing

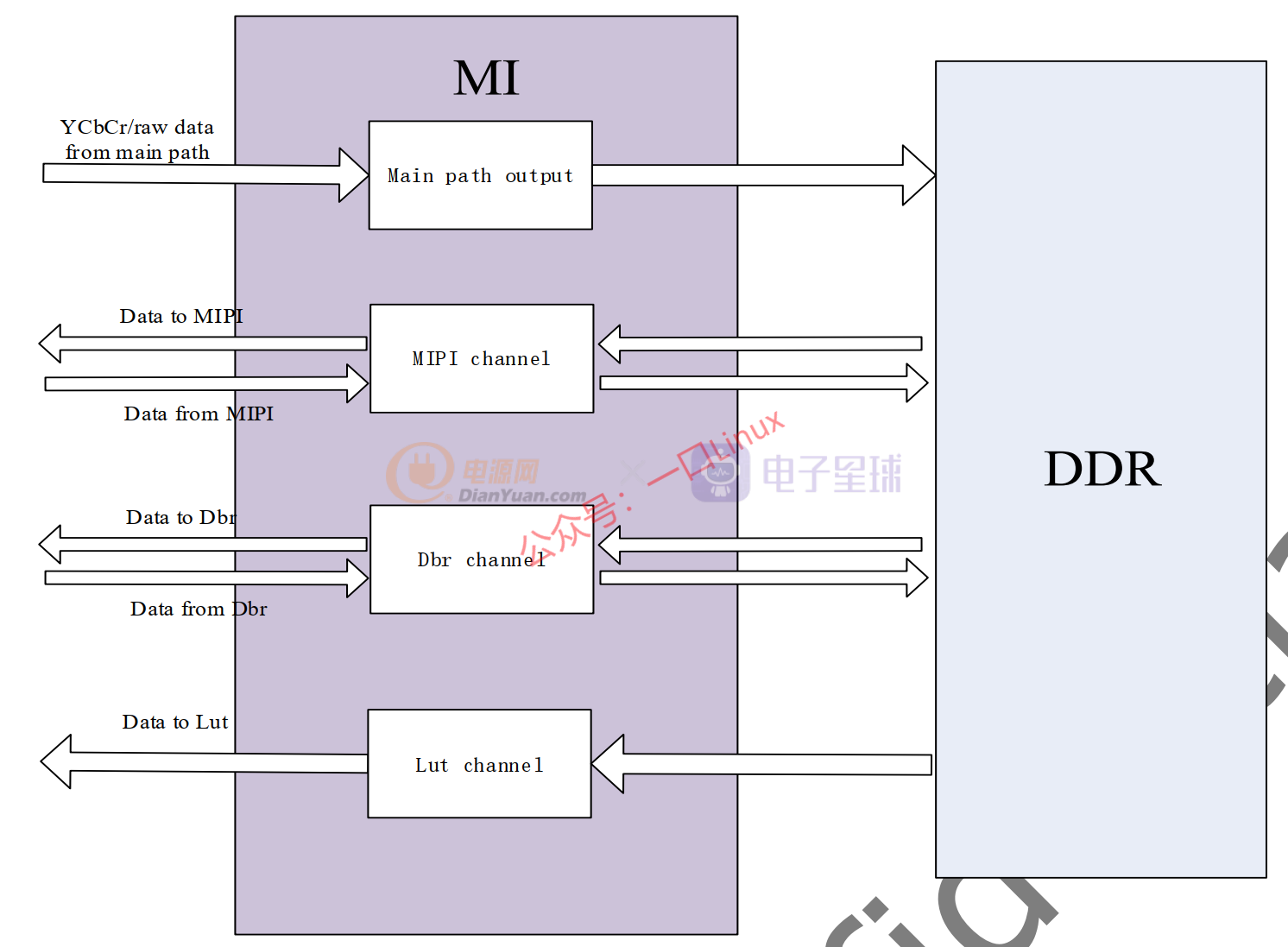

- Memory Interface(MI)

MI接口如下:

一般抓图的顺序:

- 摄像头的初始化(输出格式、分辨率、输出速率)

- 使能摄像头接入主控板卡中的物理通道

- 使能主控板卡中的ISP(图像信号处理模块)、并让ISP知道当前有效接入的摄像头是哪一个(因为可以多个接入,但只能一个有效)。

- 告诉ISP输进来的数据如何处理(颜色空间转换、缩放、裁剪、旋转等)、经由那个通道输出到内存/显存(MP主通道、SP自身通道)。

- 输出到内存

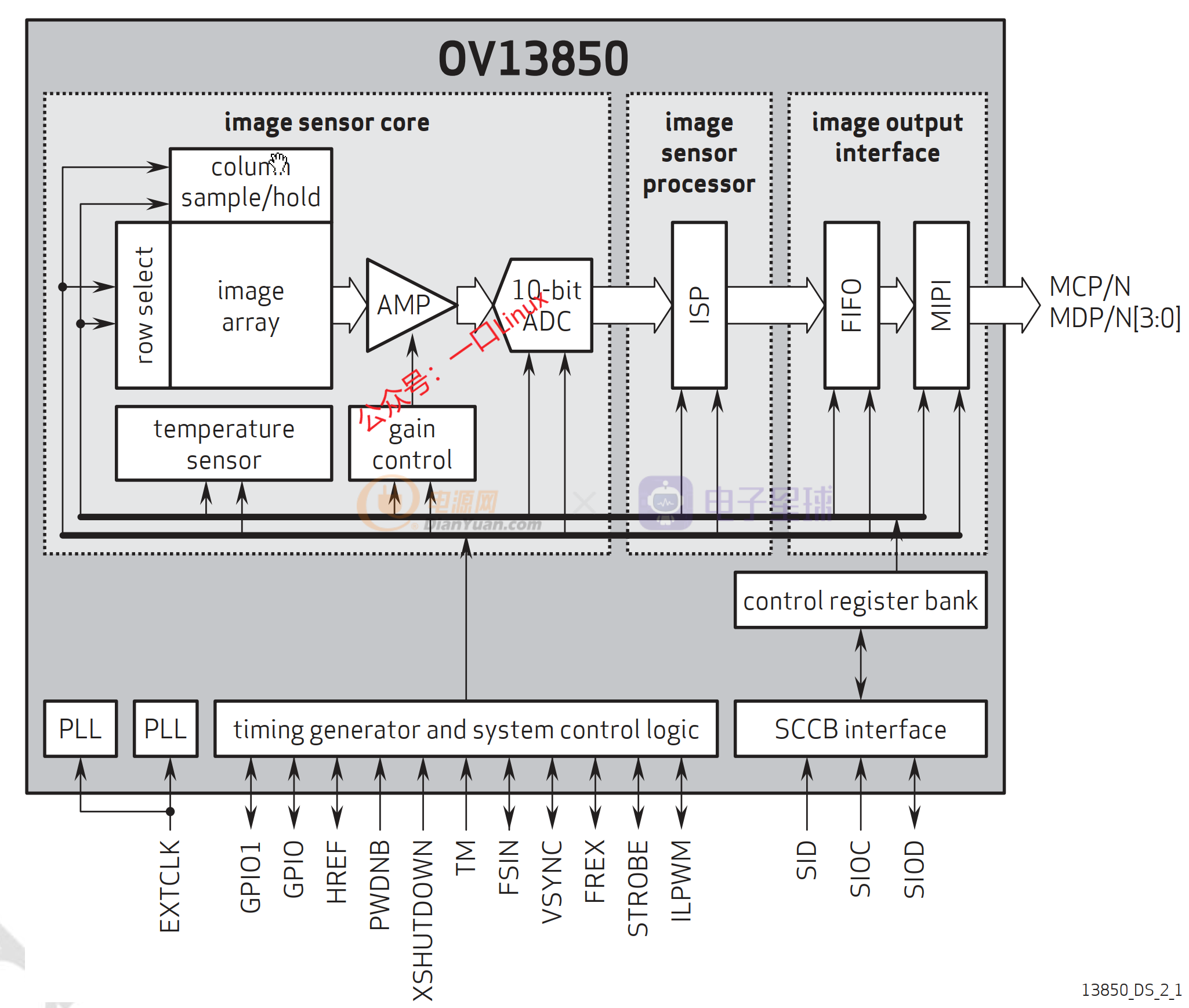

3. Camera-OV13850内部结构

下面看一款摄像头模组OV13850的内部结构图:

定时脉冲发生器输出时钟来访问成像阵列的行,预先填充电荷并且按顺序对数组的行进行采样。

在预先填充电荷和采样的时间间隔内,每个像素点的电荷曝光时减少入射光。

这是在滚动快门的体系结构的曝光时间。

曝光时间通过调整预先填充电荷和采样之间的时间间隔控制。

在每一行的像素数据采样后,通过模拟电路(AMP)进一步处理:纠正偏移量和将数据乘以相应的增益。

模拟处理后通过10位ADC的输出数组中的每个像素的数据。

ISP(image sensor processor)通过图像输出接口单元,经过MIPI接口(MCP/MDP)将图像数据发送出去。

好了,本文暂时讲到这里,

后面会继续更新几篇Camera文章,

建议大家订阅本专题!

也可以后台留言,加一口君好友,拉你进高质量技术交流群。