大家好,我是硬件微讲堂。这是我的第50篇原创文章。为避免错过干货内容,一定记得点赞、收藏、分享哟。加微信hardware_lecture进群沟通交流。

上篇文章中,关于米勒效应仿真时,在米勒平台期间漏极电流Id持续上升的问题,目前还没有找到合理的解释(或者哪里出了问题)。已经把问题信号释放出去,也请教了业内的朋友。现在是2023/2/26 23:12,我们暂且“让子弹飞一会儿”,稍后再看效果。我们今天聊一位同学在群里问的问题,我觉得有意思,拿出来和大家分享下。

1、一道问题

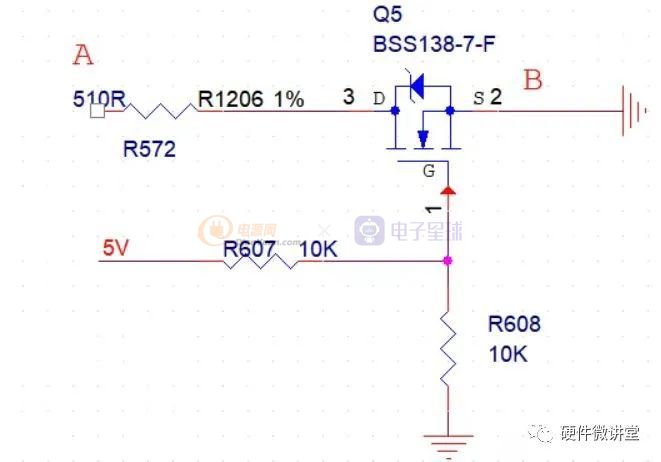

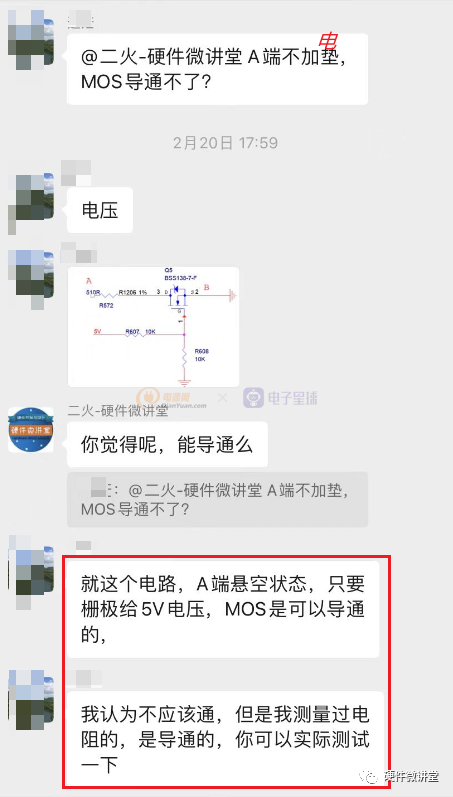

如上图所示,小明问:该电路,在A-B点间测量电阻,阻值应该是多少?

具体电路如上图所示,你觉得应该是都是?最好能说出你的理由。

2、第一回合:众说纷纭

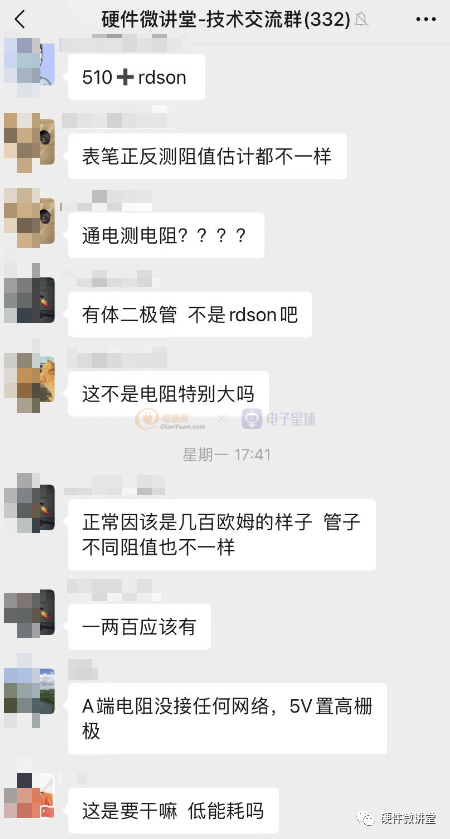

起初,小明抛出问题后,群里讨论的很热闹,众说纷纭。有说一两百的,有说几百的,也有说510+Rdson,当然也有质疑通电不应该测电阻的……

当然,我也给出了“自以为的正确”答案:

①首先,明确题目所给条件不够充分,没有明确该MOS管的Vth。不确定栅极分压后的2.5V,是否大于开启电压Vth;

②其次,按照常规应用的思路,漏极不应该悬空,应该接有电压。这个电压会影响MOS管所处的工作区。

其实,按常理说我提的第二条也没毛病。漏极电压确实会影响MOS管的工作状态。不清楚的同学可以翻看上一篇文章《关于MOS管的米勒效应的疑问--求实锤》中的“MOS管3种工作状态”小节。

但是,注意题目设定就是这样。人家就是要漏极悬空,就是这么任性!

3、第二回合:意见聚拢

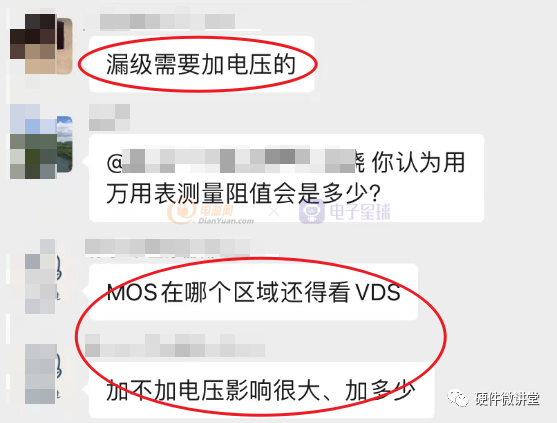

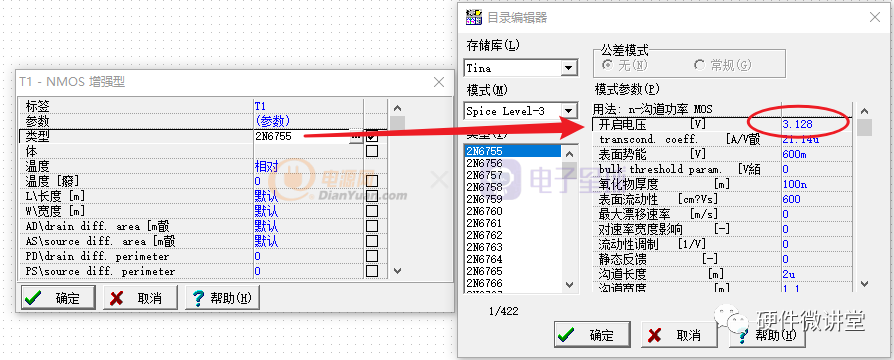

通过第一回合的讨论,小明同学觉得有必要释放一些关键信息。如下图,给出MOS管的Vth参数典型值为1.2V,即栅极2.5V的分压是足够的。

在排除了Vgs<Vth的可能后,大家一直把争议的聚集点聚焦在漏极电压上:认为漏极需要加电压,会影响MOS的工作区。这点和我的思路类似。

这就像我们的生活,没有那么多的应该和不应该,没有那么多的如果和假如,有的只是现实。我们所能做的就是接受现实,并努力去改变,去提升!

这道题的题目设定就是悬空,那就需要按照悬空来考虑。而不是说,应该给漏极加电源。这里,我和其他同学一样,进入了误区,而且还不自知!

4、第三回合:揭晓谜底

小明见我们讨论的方向要跑偏,把这个问题换一种问法:漏极(A端)不加电压,MOS管导通不了?

自以为正确的我,此刻还在反问。小明此时给出了答案,A端悬空,MOS管可以导通。

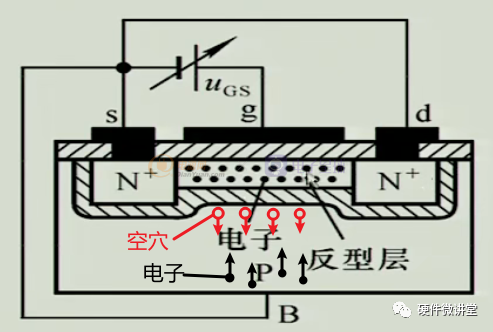

此刻,我恍然大悟!这不就是在《Rdson对应MOS管的哪个工作区?》(点击文章标题可直接访问)文章中讨论的抛开漏源电压Vds,研究栅源电压Vgs对导电沟道宽度的控制作用么?

在这个过程中,在Vgs驱动下,反型层已形成,导电沟道已存在。Vgs加大,导电沟道宽度增加;Vgs减小,沟道宽度就减小。栅源电压Vgs对导电沟通到宽度有控制作用。而这个导电沟道就表现为一个电阻特性:Vgs变化,电阻变化;Vgs不变,电阻不变。

所以,这道题的正确答案应该是510+Rdson(Ω)。

5、仿真数据

上面的讨论,如果你觉得到此就结束,那你可能不太了解硬件微讲堂的调性,咱们给出的结论必须要有数据支撑,所以仿真走一波!

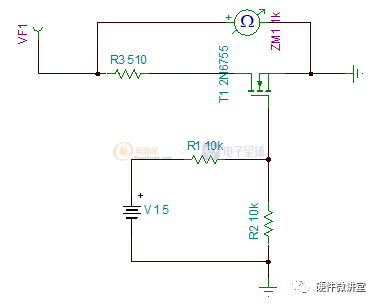

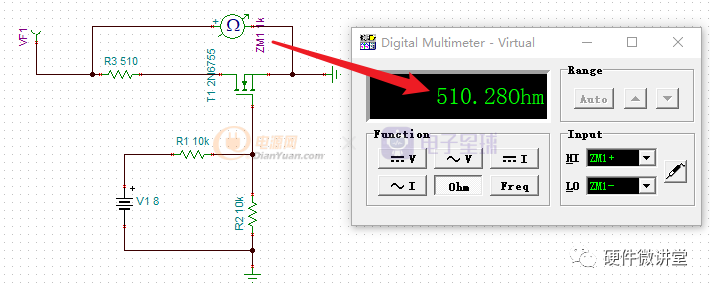

如上图,先搭建个电路。R3(510Ω)左侧悬空,栅极由一个5V的电压源做(10k/10k)分压。A-B两端挂一个欧姆表ZM1。

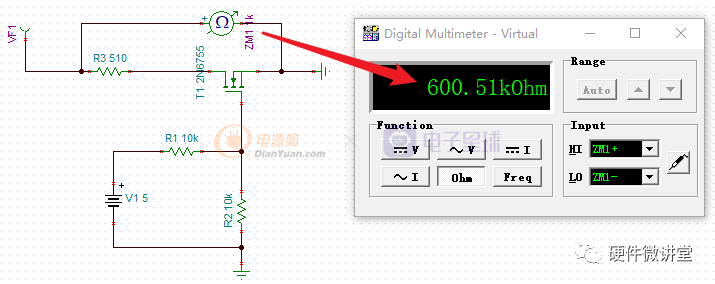

仿真电路搭建好后,开始仿真。在“T&M”--选择“万用表”--选择“Ohm”档,在Input会自动跳出来ZM1+和ZM1-。可是,结果怎么是“600.61kohm”?

哪里出问题了?

经过分析,原来是我选择的MOS管的Vth超过了2.5V。经过一番搜索,在器件库里没有找到Vth低于2.5V的MOS管,于是就把栅极挂的电压从5V调整为8V。

再次进行仿真,欧姆表读数为510.28Ohm,符合理论分析。

7、总 结

先聊到这里,梳理下今天讨论的内容:

今天主要是针对小明提出的关于MOS管实际电路应用问题进行了讨论,梳理了前后讨论过程,并进行了理论分析和仿真验证。所涉及的知识点难度不高,但却具有一定的隐蔽性。

总的来说,这是一个不错的问题。也欢迎小张、小李、小王以及屏幕前的你……能多提类似的问题,相互交流,共同进步。

怎么样?一个简短的问题,给出的回答可浅可深。我的助攻只能到这里,能否晋升到陆地神仙境,一剑开天门,就看你的造化了!

关注“硬件微讲堂”,硬件路上不慌张!