大家好,我是小小的电子之路,这是我的第31篇原创文章,很高兴与大家一起分享~

原文出自微信公众号【小小的电子之路】

数字电路的结构虽然复杂多变,但是从本质上来讲,数字电路只有组合逻辑电路和时序逻辑电路两大类。

组合逻辑电路不具备记忆功能,其输出只取决于输入,与电路所处的状态无关;

时序逻辑电路具备记忆功能,其输出不仅与输入有关,而且还与电路所处的状态有关。

在Verilog HDL语言中,组合逻辑电路与时序逻辑电路有着不同的描述方法。

组合逻辑的描述方法一般有两种,分别是:

(1)always @(电平敏感信号)、always @(*)

(2)assign

时序逻辑的描述方法一般是:

(1)always @(边沿敏感信号)

下面通过具体的代码与仿真来演示一下Verilog HDL中组合逻辑与时序逻辑的描述。

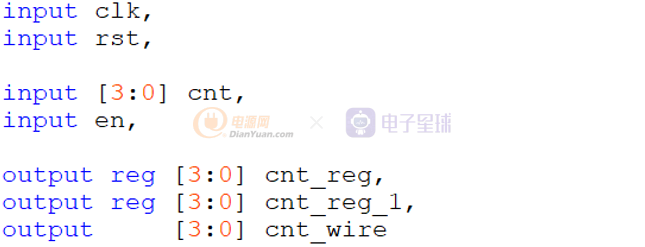

1、Verilog HDL代码

该代码描述了一个时序逻辑电路和两个组合逻辑电路,具体分别是:

(1)时序逻辑:敏感边沿为clk的上升沿与rst的下降沿,只要其中任何一个边沿出现,就会执行一次always过程块。

(2)组合逻辑一:敏感信号为cnt,只要cnt发生变化,就会执行一次always过程块。

(3)组合逻辑二:连续赋值,赋值表达式始终处于执行状态,输出cnt_wire始终随着cnt的变化而变化。

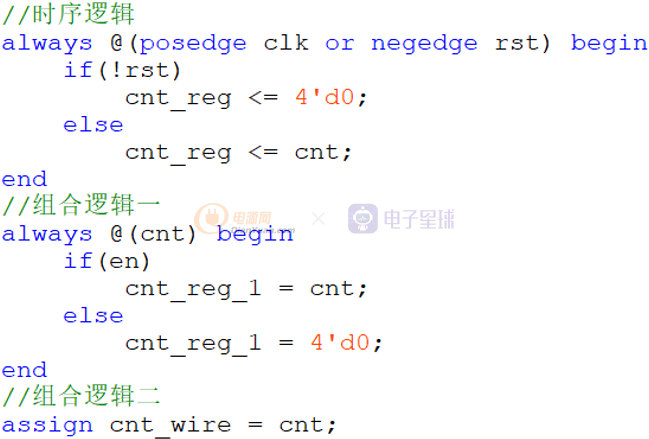

2、RTL电路

观察该代码对应的RTL电路,同样的,电路包含了一个时序逻辑电路和两个组合逻辑电路。

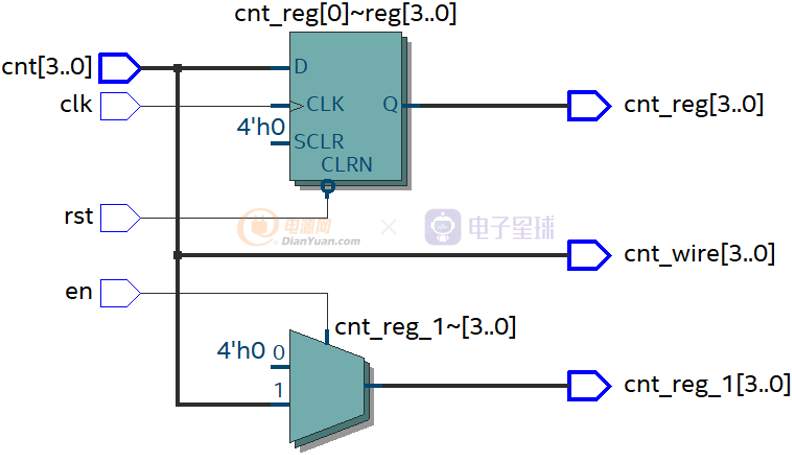

3、仿真结果

观察仿真结果可以发现,时序逻辑电路的输出cnt_reg不仅与输入信号cnt有关,而且还与clk信号与rst信号的边沿有关,相比之下,组合逻辑电路一的输出cnt_reg_1只取决于其输入信号cnt和en,组合逻辑电路二的输出cnt_wire只取决于其输入信号cnt。