I2S总线一般由1根系统时钟线和3根信号线组成:

MCLK:称为主时钟,也叫系统时钟(Sys Clock),一般为了使系统间能够更好地同步时增加MCLK信号,MCLK的频率 = 128或者256或者512 * 采样频率;

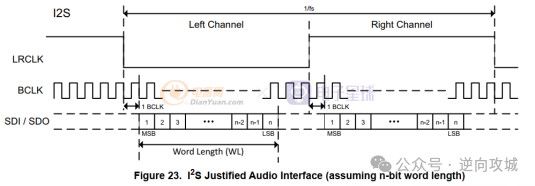

SCLK(BCLK):串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCK的频率 = 声道数 * 采样频率 * 采样位数;

LRCK:帧时钟LRCK,(也称WS),用于切换左右声道的数据。LRCK为“1”表示正在传输的是右声道的数据,为“0”则表示正在传输的是左声道的数据。LRCK的频率等于采样频率;

SDATA(SD):就是用二进制补码表示的音频数据。最高位拥有固定的位置,而最低位的位置则是依赖于数据的有效位数。

我们基本都是按照Philips为蓝本,看下I2S时序:

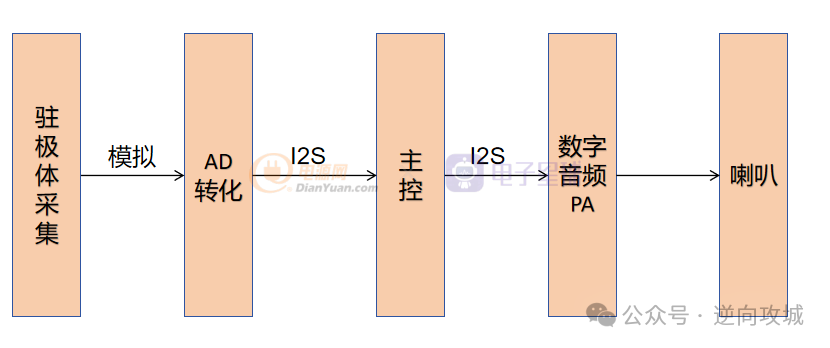

下图是我之前做过的一个项目

框图如上图所示:

具体芯片就不说了,做的是个麦克风,然后固定位数频率输出,大家应该能看到电脑,这个参数跟声卡有关,由于本人3T硬盘损坏了,导致电路没找到,这里就贴不了电路图,等后面在讲解SOC的时候在补上吧。

我们对音频的处理一般是通过DSP进行算法处理,得到我们人耳最舒服的状态,所以目前市面上的耳放区别都不大,但是能做的很好的,很少很少不同年龄段的人要求不一样,但多数人听到的也就习惯了(人的年龄越大听到声音的范围越小,常理刚出生的小孩确实能听到我们听不到的声音),个人觉得音频比视频要做好更难,其他具体的就不赘述了。

个人观点:

-

音频前端电源一定要保证纹波足够小,噪声也要足够小,纹波和噪声有很大区别,要分别处理好,特别是高频电路中,做好滤波;

-

好的麦克风和功放效果不仅仅是硬件的工作,软件要做的也很多,前后端的滤波,声音采集处理算法;

-

PCB设计的时候,做好包地的处理,不要让地的底噪过大(名义上的GND不是大地,会存在底噪,各种干扰都会影响音频信号)。