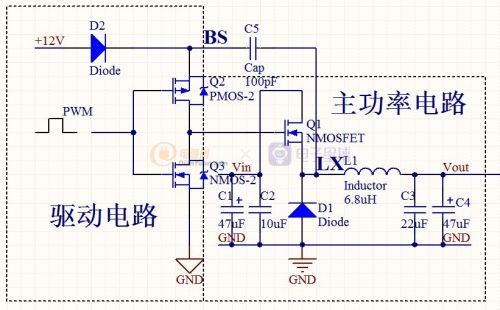

一种非隔离MOS管驱动电路-模仿电源管理芯片驱动结构

我是根据电源管理芯片内部MOSFET驱动结构修改的。

大家看看!

原理图附件:Protel 99 SE 版本: ![]() 99 SE [2013-9-2更新]

99 SE [2013-9-2更新]

Altium Desiger summer 09 版本:![]() AD 09 [2013-9-2更新]

AD 09 [2013-9-2更新]

欢迎大家提意见,吐槽!

解释说明:

『主功率管Q1截止时』:LX端为零电位,此时BS端(C5的左端)为12V-0.3V,此时如果PWM为低则有Q2 P管导通,Q3 N管截止,则主功率管Q1的栅极为11.7V高于源极LX,管子导通,同时C5充电至11.7V。

『主功率管Q1导通后』:LX端的值为Vin,这里假设为40V,此时BS端(C5的左端)就变为11.7+Vin=51.7V,此时仍保持主功率管Q1的栅极高于源极LX 11.7V,Q1保持导通。由于二极管D2的单向导电性,BS端不会向+12V电源灌电流,保证+12V安全。

当PWM为高时,比较简单,不做详细分析,大家都懂得。

这也是该设计的巧妙之处,用于『非隔离』的驱动。所以这里的『C5』是非常重要的(D2也是必须的),并不是简单的滤波这些的。但同时也有一个问题就是,C5 的容值需要根据开关频率进行选择。如果开关频率低,C5 容值小的情况可能造成C5放电使栅极源极压差小于导通电压而使主功率管Q1提前关断,所以如果开关频率低则选择大点的C5,如果开关频率高则选择小点的C5节约成本。

您好!abccba 团长,我不太认同您的观点,详情请您看我的2帖解释,你看看是否有道理!

我这里设计的是『非隔离式』的,如果按照您的画法则+12V的地必须与主功率电路的地隔离(不共地),否则二极管被地短路。我的电路是可以共地的,所以才需要C5以及D2的。

我的驱动电路的GND与主功率的GND图标不同是为了画PCB时提醒自己分开布线减小干扰最后一点相接,并不是GND标错了。