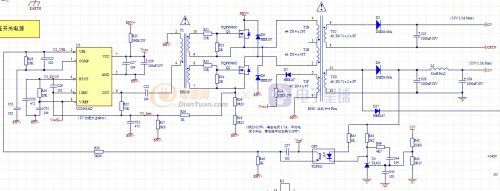

先上电路图,详细问题在跟贴里说明。

整体电路:

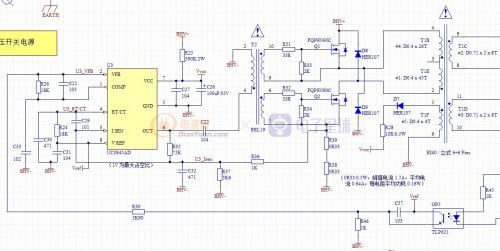

控制芯片部分:

变压器及整流部分:

变压器结构:

(变压器的实际气隙为 1.2mm,得到电感量为 1150uH)

问题在于,起动时不断打嗝。分两种情况:

1. 完全空载时起动打嗝

两路输出都完全不接任何负载。电源两路输出均为 32V,但不断打嗝起动。查得原因是由于没有负载,输出电压过冲后(高于431设定的电压)长时间不能回落,反馈回路使控制芯片长时间处于 0 占空输出状态,因此辅助电源无电压输出而使控制芯片掉电,从而引起打嗝。我想这个情况应该属于正常现象。

2. 有负载时起动打嗝(负载不重)

仅在其中一路输出上接一个150欧电阻作为负载,假如电源正常,则此电阻应该流过 0.2A 电流,消耗 6.4W 功率。而本电源设计目标功率为 90W,每路输出最大 1.5A。

但事实上,接上这个电阻后,电源仍然起动打嗝,原因与第一条完全是另一码事。经检查,电源的两路输出和辅助电源输出的电压均极低,辅助电源只有 4V 不到、主输出只有 8V 不到。因为辅助电源不能提供足够电压,造成芯片欠压而打嗝。

=============

我想知道是什么原因造成输出电压如此低!

检查项目有:

A 芯片振荡正常,输出脉冲频率 75KHz。

B 两功率管的驱动正常。驱动相位是正确的,两管同步开通和关断,上升、下降速度均属正常范围。

C 变压器的各绕组相位正确,波形是正确的反激波形。

D 测量电流传感电阻上的电压波形很好,起动占空比约 40%,最高点电流峰值约 1.25A。

E 由漏感引起的初级绕组反射电压(经D8 D9反馈到主电容)被正确钳位,D8 D9 的导通时间短于 150ns(电流峰值1.2A)。证明此部分能量是很小的,没有造成太多的能量反馈回电源电容。

================

好了,经过以上检查,我的疑问是:

功率管开通期间确实是储存了能量(第 D 检查项),而且占空时间是 40%、电流峰值 1.2A,说明储存的能量应该不小。但功率管关断后,释放到次级只有 8V 不到的电压,在 150欧电阻上只流过了 0.05A 的电流。(事实观测反激期间的次级波形,确实只有8V左右的平直波形,而且持续时间比较长,大约 50% 占空比,是 DCM 工作模式)

磁芯中储存的能量那里去了?是根本没有储存足够能量么?电路有问题还是变压器有问题?

我第一次做双管反激。单管反激、单管正激都做过的,基础的东西懂一点,但经验还是不足。谢各位指正指正,感激不尽。

3845是否可以不用斜坡补偿?C29

“经检查,电源的两路输出和辅助电源输出的电压均极低,辅助电源只有 4V 不到、……”——辅电VCC这么低,按理说3845是欠压闭锁的,不会有占空比输出。![]()

就是因为 VCC 的原因才打嗝的。芯片起动前主电容经过 R25 对 C26 充电,达到 8.5V 左右芯片开始输出,由于辅助电源电压不足,C26 的电压逐渐被消耗,当电压下降到 7.4V 左右芯片欠压保护,然后重新开始对 C26 充电。如此重复就形成打嗝。

从 8.5V 下降到 7.4V 这段期间,芯片可输出数百个脉冲,如果电源正常,则此期间辅助电源早就提供了足够的电压给 VCC,就不会发生这情况了。可惜了,辅助电源电压太低,不满足条件。

(补充一下,主电容没有出现在图中,是 33uF/700V 电解电容)

是这样,由于 C22 的存在,MOS 栅极只有 +5V -4V 左右,MOS 开通速度比较慢,波形不好,但主变压器还是有输出的。

基于此情况,我短接了 C22,因此 MOS 栅极没有负压,开通时 +9V 左右。开通速度和关断速度均很好。由于此驱动变压器体积比较大,取消 C22 也没有饱和现象。检查了栅极波形,波顶平直,确实没有驱动变压器磁芯饱和的情况出现。

(补充:MOS 栅极电压很是诡异,芯片输出脉冲电压只有 6V-6.5V 左右,但经过驱动变压器后就变成了 6V-9V 不等,且有时是正负对称波形,有时只有正脉冲波形。)

多谢。我刚找到了问题所在,正如你所说的情况。![]()

多谢 abccba,其实他应该一开始就发现了此问题,只是被我的前提说明给忽悠了。![]()

===============

我将 Q1 去掉并加上了 RCD 钳位,临时改成了单管反激,并跳过了 EE19 以芯片直推 Q2,电路马上就正常工作了。

在维持单管反激的拓朴下,重新经过 EE19 推动 Q2,立即恢复到原本的打嗝状态。证明是因为经过 EE19 后不能可靠推动功率管而引起此问题。

================

我详细对比了直推和经过 EE19 推动两种电路下的波形。经过 EE19 后 MOS 开通延时了大约 250ns,漏极电压总下降时间接近 500ns(已包括开通延时在内),但 MOS 确实是开通了足够长的时间。单从漏电压波形和源电流波形确实不能分析出问题的本质。

我重新查看了 FQP9N90C 的手册,并对比波形,确认了 MOS 可靠开通的栅压不应低于 6V。在栅压低于 4V 时 MOS 不能开通,4V-5.5V 之间通态电阻比较大。从波形看我的电路在起动期间栅压在 5V-6V 之间不断变动,所以应该是栅压不足引起的问题。(芯片直推可一直维持栅压在 6.5V)

===============

因此我判断将 UC3845 换成 UC3844 应该就能解决问题。待我买到件换上后试一试就可以作出定论。

另外我估计芯片不外加图腾而直接驱动 EE19 应该不是大问题,因为在多个板上应用了这个方法都是正常的。它最多是引起功率管增加点热量,我的散热器足够大,这个不是问题。

用于驱动的脉冲变压器,次级输出可看做是交流,正负压的面积相等,随着占空比变化,正负峰值也发生变化,占空比越大,正峰值越小-负峰值越大。而栅极驱动时,我们希望正峰值稳定以确保安全和可靠,负峰值防范栅源过压击穿。

在想,可否考虑增添元件,改善栅极驱动电路,以弥补正负峰值随占空比变化的不利?![]()

有 C22 时驱动变压器工作在交流变压器状态,从我观察的波形来看正如你所说,占空比越大负峰值越大。

但有个怪异的情况,正峰值没变小。无论芯片输出占空比是多少,次级波形总是 50% 占空比的波形,但正脉冲部分是个阶梯波。例如假设芯片输出脉冲占空比为 20%,脉冲电压为 7V,那么次级正脉冲 0-20% 部分电压为 7V、20-50%部分大约 4V、50-100%部分为 -4V。差不多就是这样。

无 C22 时驱动变压器工作在正激变换器状态(双向),次级波形大致与初级相同,关断部分有很小的一个负压。

驱动变压器的电感量要大些,改用磁导率大的磁芯可以降低驱动电流要求。最好用磁环。

驱动变压器的结构对驱动波形的好坏有较大影响,用三明治打法会好些,如:

1/2Np:Ns1//Ns2:1/2Np

那么 C10 和 R30 的值应该选择多大呢?

如果 R30 用我电路里的 33 欧,我怕 C10 上存不了多少电压,那它的自举作用就不大了。毕竟初级的隔直电容在脉冲输出期间存不了多少电量,仅稍大于 MOS 的栅电容电量。在脉冲关断期间,这些电量以负脉冲传输到次级,那么 D12 和 R30 组成的负载已经消耗掉大部分这些电量,在 C10 上应该存不了多少。

另外 Q6 应该选择什么型号?Q6 的 E 极直连栅极,中间没有栅电阻,栅电容的电量要全部在 Q6 内消耗掉,如果 Q6 容量太小,我怕它不耐用。