在上一帖子《MOS的选择》中说到了MOSFET芯片的参数指标,这一贴想和大家讨论一下MOSFET的封装。

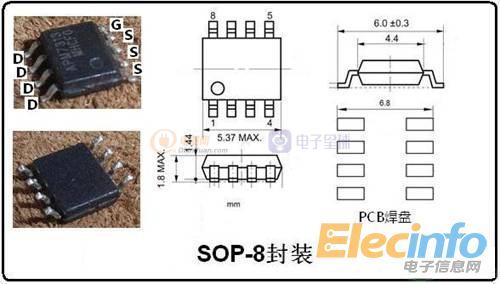

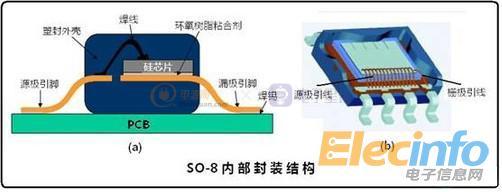

MOSFET的封装,简单说,就是在MOS芯片制作完成之后,给芯片加上一个外壳。

在开始的时候,各方面性能要求不高,只要求外壳具有支撑、保护、冷却的作用,同时还要为芯片提供电气连接和隔离,以便MOSFET 器件与其它元件构成完整的电路。

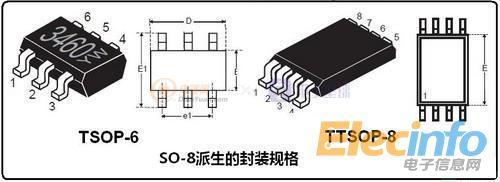

后来,随着电子产品越来越小的趋势,有了不断减少尺寸的要求。

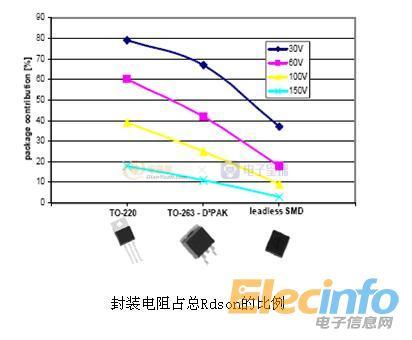

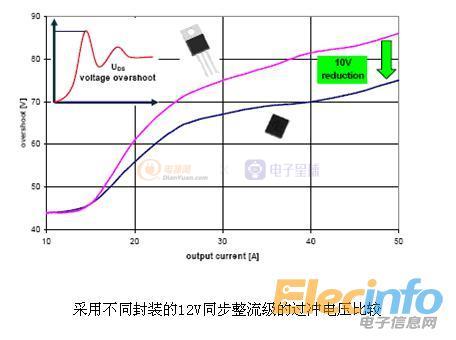

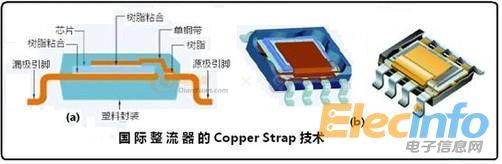

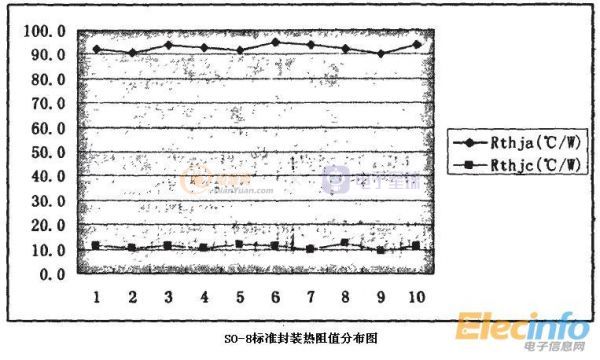

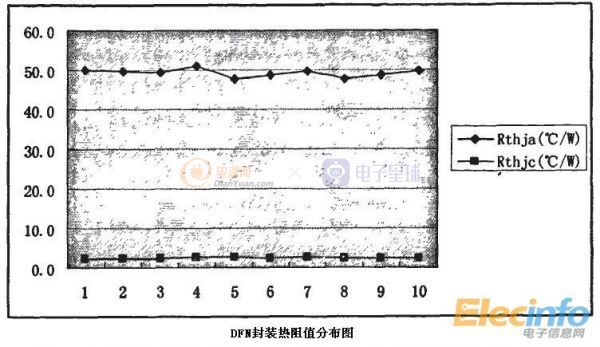

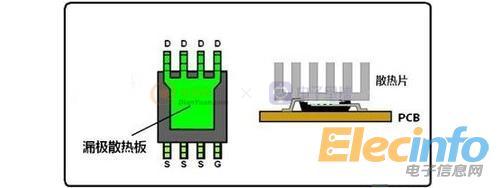

近年,对功率密度的不断追求,MOSFET作为主要的功率器件,正朝着更大功率、更小尺寸、更快速、散热更好的趋势在发展。因此,也对MOSFET的封装,在寄生的电阻、电容、电感等电性能和结构、封装热阻等热性能方面,都有了更多的要求。

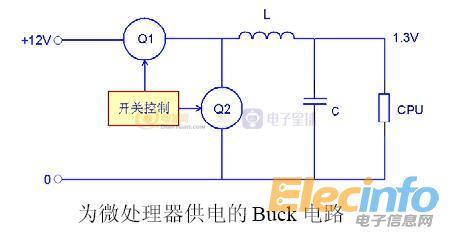

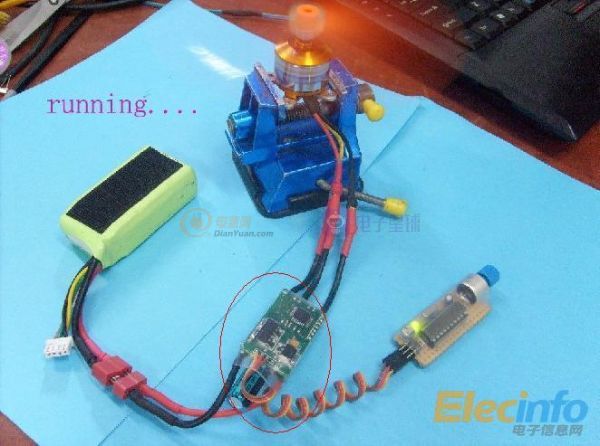

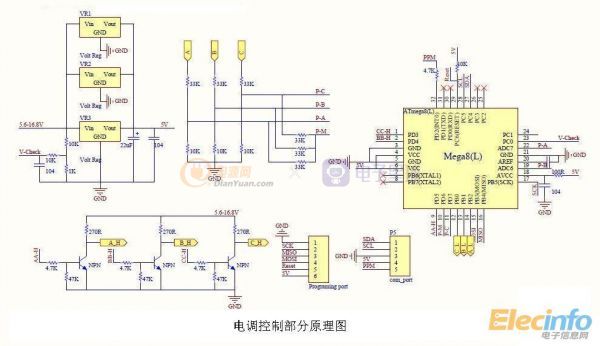

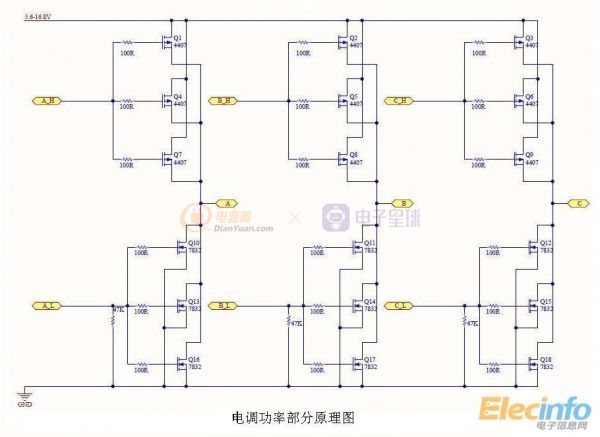

本贴准备和大家,在封装的发展历程、结构形式对电热性能的影响、以CPU供电为例的同步整流和航模用电子调速器等应用实例中MOSFET对封装的要求,等方面进行探讨。

先起个头,慢慢加。

如对芯片尺寸、选择BV、Rds、Qg等参数平衡点、封装的考虑方向等问题感兴趣,请积极发表见解,

有兴趣欢迎加Q探讨,Q:369364322