前言

本文將針對62000P系列機種的電壓下降斜率(Voltage Slew Rate)之使用方法和原理作一詳細的介紹。因為62000P系列為一開關式直流電源且輸出有一電容做穩壓濾波,因此,只對於電壓上升斜率(Voltage-Slew-Rate-Up)的設定是有效,這是由於”使電壓上升”為一個Source的行為,而”使電壓下降”為受限此電容放電及內部DummyLoad影響,故本文將提出以外加Electronic Load的方式,來說明如何使用62000P系列電源達到電壓下降斜率的設定?

1. 原理說明

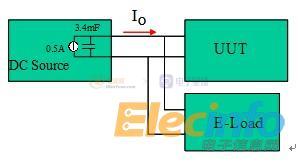

不管哪一類的DC Source,其內部輸出級都有輸出穩壓電容,如圖1所示。因此,電壓往下設定時,必須對內部電容作放電,才有可能達到所設定之斜率(Slew Rate)。

圖1. DC Source內部輸出電容和放電定電流源,以及UUT(Device Under Test).

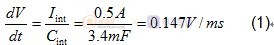

以Chroma 62012P-80-60而言,其內部輸出電容Cint約為3.5mF(+-20%),而電壓往下設定時,機器內部會有0.5A定電流對電容作放電,因此,若UUT為空載時,則DC Source之下降斜率(Slew Rate)為

因此,在空載之情況下,只要電壓斜率(Voltage Slew Rate)設定大於0.15V/ms,則輸出電壓將無法達到所設定之下降斜率。

若要達成設定之電壓SR(Slew Rate)有兩種途徑:(a)為UUT本身需拉載,如圖2所示,(b)為DC Source輸出需拉載,如圖3所示。

圖2. DC Source連接UUT,且UUT有拉載.

圖3. DC Source連接 UUT,並且DC Source有拉載E-Load.

由於UUT是否拉載,關於UUT本身之測試項目,故無法決定,因此,以下將介紹第二種途徑。如圖3所示,其DC Source輸出電容的Slew Rate為

其中,VS.R.:DC Source設定之Slew Rate.

IO:Electronic Load拉載之電流

因此,以62012P-80-60而言,要達到下降之SR,Electronic Load應拉載電流為

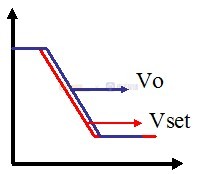

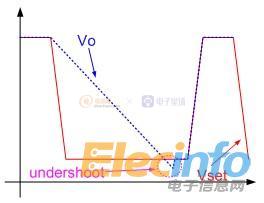

接著,舉例四種情況來加以說明Electronic Load拉載電流對電壓SR之影響。情況一,如圖4所示,為Electronic Load拉載電流足夠之情況,即Electronic Load拉載電流滿足(3)式,如此DC Source的實際輸出電壓Vo之SR,會和DC Source的設定輸出電壓Vset之SR相同。

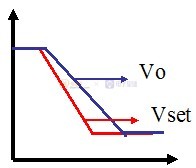

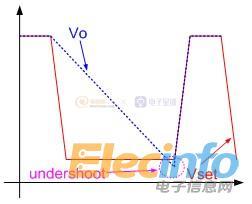

情況二,如圖5所示,為Electronic Load拉載電流不足之情況,即Electronic Load拉載電流不滿足(3)式,因此,DC Source內部輸出電容僅能靠內部的0.5A對電容作放電,故由(1)式可知最大電壓SR=0.15V/mS,如此DC Source的實際輸出電壓Vo之SR,將與DC Source的設定輸出電壓Vset之SR不相同,此乃因為電容的放電電流不足所導致。

圖4. 情況一, Electronic Load拉載電流足夠.

圖5.情況二, Electronic Load拉載電流不足.

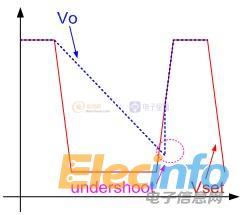

情況三,如圖6和圖7所示,為Electronic Load拉載電流不足,並且Vo在達到Vset之後,Vset才執行了下一個電壓上升(Programming Upward)之情況,此時由於Electronic Load拉載電流不足,所以即使duty cycle=0亦無法使Vo追蹤(track)到Vset(即Vo>Vset),故會發生控制飽和現象,因此在下一次電壓上升時,Feedback Control Operating Point無法立刻從控制飽和區回到控制線性區,而使得Vo出現undershoot,直到Operating Pint回到控制線性區後,其Vo會立即追蹤Vset,而有導致overshoot之可能。

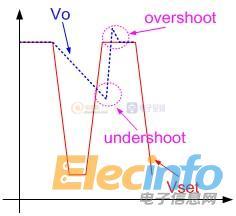

情況四,如圖8和圖9所示,為Electronic Load拉載電流不足,並且Vo在尚未達到Vset之前,Vset就執行了下一個電壓上升(Programming Upward)之情況,此時由於Electronic Load拉載電流不足,所以即使duty cycle=0亦無法使Vo追蹤(track)到Vset(即Vo>Vset),故會發生控制飽和現象,因此在下一次電壓上升時,Feedback Control Operating Point無法立刻從控制飽和區回到控制線性區而使得Vo出現undershoot,直到Operating Point回到控制線性區後,其Vo會立即追蹤Vset,而導致overshoot之可能。

圖6. 情況三, Electronic Load拉載電流不足,並且Vo在達到Vset之後,Vset才執行了下一個電壓上升

圖7. 情況三, Electronic Load拉載電流不足,並且Vo在達到Vset之後,Vset才執行了下一個電壓上升

圖8. 情況四, Electronic Load拉載電流不足,並且Vo在尚未到達Vset之前,Vset就執行了下一個電

壓上升.

圖9. 情況四, Electronic Load拉載電流不足,並且Vo在尚未到達Vset之前,Vset就執行了下一個電壓上升.