上拉和下拉电阻在电阻中的使用频率可以说是相当的高,我们通常在设计电路时候习惯性的会使用上拉或者下拉电阻,可能并没有深究其作用,认为加不加对电路的性能并无多大影响,其实不然。对于上拉和下拉电阻的使用知其然还需知其所以然,下面帮大家分析下:

1)上拉电阻与下拉电阻用在什么场合?

用在数字电路中,存在高低电平的场合。

2)上拉电阻与下拉电阻怎么接线?

上拉电阻:电阻一端接VCC,一端接逻辑电平接入引脚(如单片机引脚)

下拉电阻:电阻一端接GND,一端接逻辑电平接入引脚(如单片机引脚)

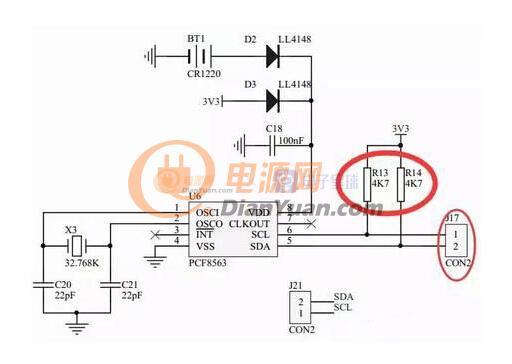

如上图,R13和R14,一端接到了3.3V,一端通过J17连接到单片机引脚,这两个电阻就是上拉电阻。

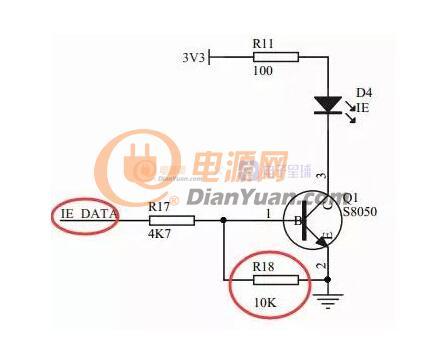

如上图,R18的一端连接到了GND,一端连接到了单片机的引脚(只不过是串了一个电阻后连接到了单片机引脚)。所以这个就是下拉电阻。