当高的dv/dt供给漏极时,在功率MOSFET中有一个电流传导的可能性,在一些情况下,这可以损毁器件。下面给出一些由于dv/dt器件导通的实例。

(1)静态dv/dt

1. 假导通

2. 寄生晶体管导通

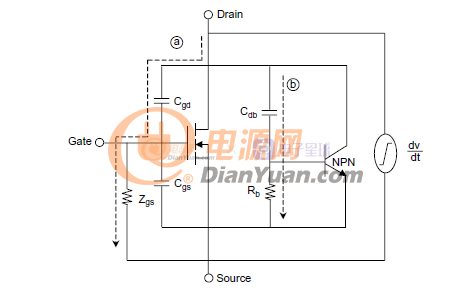

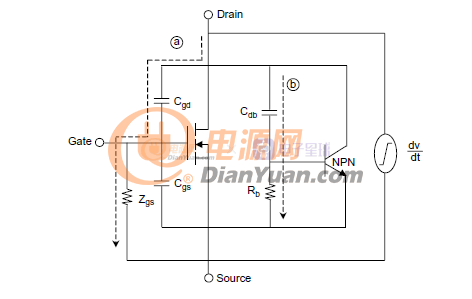

1. 在关断状态,漏极电压的突然增加改变整个漏极和栅极之间的寄生电容,产生位移电流(a)C*dv/dt。如果由于位移电流和栅-源阻抗(Zgs)在栅极和源极之间形成的电压超过Vgs(th),它触发一个假的MOSFET关断。这里,漏极和栅极之间的寄生电容根据电路布线可以等于Cgd或比Cgd大。Zgs是驱动电路的阻抗,可以表示为R、L串联的电路。由于假导通,器件进入一个电流导通状态,在严重的情况下,在器件内形成高的功率耗散且造成毁坏性的失效。下列等式展示Zgs与Vgs间的关系,和在这个模式下dv/dt的性能。

Vgs = ZgsCgd(dv/dt)

(dv/dt) = Vgs(th)/(ZgsCgd)

为了增加dv/dt的性能,应该使用一个低阻抗的栅极驱动电路,且Vgs(th)必须增大。但在一个低阻抗驱动电路中,成本较高且Vgs(th)的增大与Rds(on)的增大有关。当Vgs(th)具有负的温度系数,假导通的可能性随着温度上升而增大。但通常来说,栅极电压不会超过门限电压,高的器件电阻会限制器件电流。因此,由于假导通导致的器件毁坏是罕见的。

2. 在关断状态,一个突然增加的漏极电压改变整个Cdb的电压,而且它形成流过Rb的电流(b)。当Rb的电压超过Vbe(寄生双极性晶体管导通时的射级-基极正向偏置电压,大约为0.7V)时,寄生双极性晶体管导通。当寄生双极性晶体管导通,器件的击穿电压从BVcbo减小到BVceo,它是BVcbo的50%~60%。如果供给一个比BVceo大的漏极电压,器件陷入雪崩击穿。如果这个楼及电流没有外部限制,器件会被二次击穿损坏。下列等式表示在这个模式下dv/dt的性能。 (dv/dt) = Vbe/(RbCdb)从上述等式可以很容易发现dv/dt的性能由器件内部结构决定。对于高dv/dt性能,Rb值必须要小。这个可以通过增加P-body区域的参杂水平和尽量减小N+发射极的长度实现。Rb也会被漏极电压影响,当漏极电压增加,耗尽层扩大且加大Rb值。当温度增加时,流动性减小而Rb增加和Vbe减小,寄生晶体管导通的可能性增大。但当基极和发射极通过源极接触而短接时,Rb值很小。这个只在dv/dt异常大时才会发生。→在假导通时dv/dt可以被外部控制,但在寄生晶体管导通时,dv/dt是由器件的设计决定的。这是这两个模式的区别。

(2)动态dv/dt如果有一个突然的电流中断,例如在高速开关中的钳位电感关断,器件会被并发的应力损坏,这是由寄生电容的高漏极电流、高漏源电压和位移电流造成的。

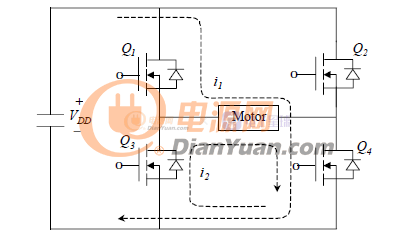

(3)二极管恢复dv/dt这是在特殊应用中dv/dt失效的主要原因,例如电路使用一个体漏二极管。数据收集给出了dv/dt的最大值。超过这个值将会造成由于二极管的过度恢复dv/dt的器件失效。下图展示了一个电机控制电路应用,该应用有二极管恢复dv/dt的问题。

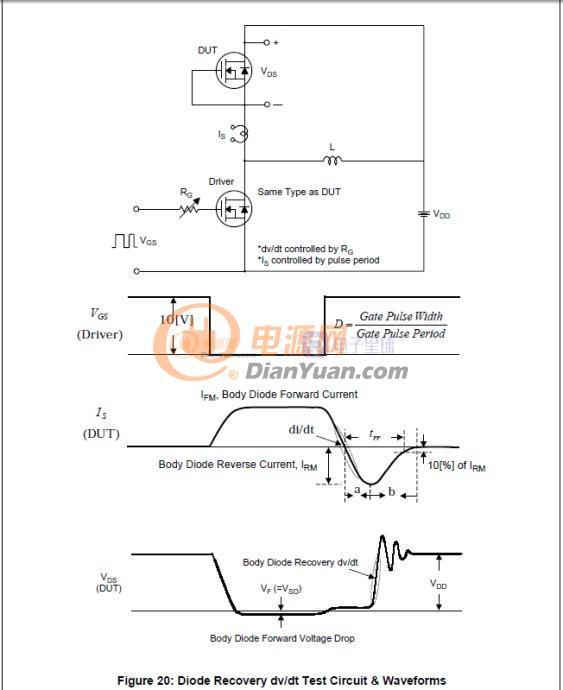

首先Q1和Q4导通,且进入一个电流i1通过的状态。如果Q1关断来控制电机速度则电流i2会流经Q3的寄生二极管(续流二极管)。Q3的寄生二极管进入正向偏置状态,同时由于二极管的特性,少数电荷开始累积。当Q1通道,电流再次变回i1,在Q3的寄生二极管中积累的少数电荷被二极管反向恢复电流移除(如图20a部分)。一旦少数电荷被移除到一个特定水平,体漏二极管的耗尽区扩大且产生更多的反向恢复电流(如图20b部分)。如果这打开了寄生双极性晶体管,则Q3会被损坏。图20展示二极管恢复dv/dt测试电路和波形图。从这个测试,不仅仅可以获得dv/dt,而且可以获得Vsd(二极管正向电压)、trr(反向恢复时间)和Qrr(反向恢复电荷)的数据。测试里,Vdd值必须小于等于BVdss。通常Vdd设定为BVdss的80%,而且驱动器的Vgs脉冲周期必须控制以使Is可以变为连续的漏电流Id。

当Rg减小,di/dt和dv/dt值变大。首先,trr可以通过测量图示中Is部分获得,这里di/dt(从地电势上的50%Ifm的点到地电势下75%Irm的点之间测量)是100[A/us]。Qrr可以用(Irm*trr)/2计算。dv/dt可以从数据手册中在di/dt条件下Vdd的10%~90%之间的点测量。Is(连续源极电流)和Ism(脉冲源极电流)表示源-漏二极管的额定电流,Is = Id(连续漏极电流),Ism = Idm(漏极脉冲电流)。