4) UVLO功能建模

根据datasheet中的描述及相关数据,UVLO是IC的输入欠压保护,这个功能其实对于仿真而言不是必须的,可要可不要的;我在这里给出,只是希望模型功能完整一点,实际仿真时可直接去掉的。

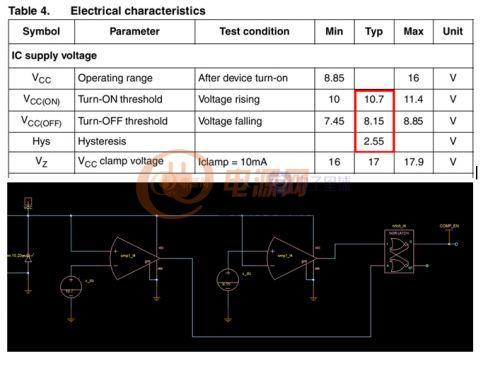

根据datasheet,我们搭建了如下的仿真电路;两个比较器和RS触发器构成了UVLO的滞环,触发器的输出q信号用以控制IC的驱动信号;考虑此模型过于简单,这里就不进行仿真验证了。

5) PFC OK功能建模

此功能比较简单,这里不作讲解,大家看看电路即可。

最近附上IC建模源文件及测试电路,验证时有几点跟大家说明 一下:

#1 文件版本为Saber 2009;

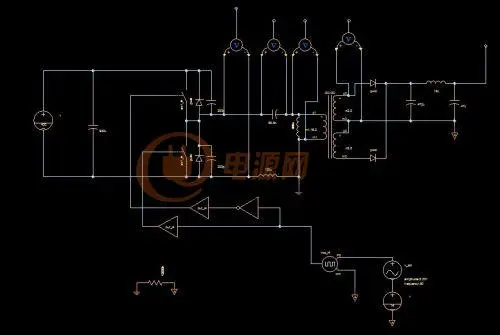

#2 两驱动输出均为数字信号;如果大家想模拟信号,需加一d2a模板;或是直接利用power semiconductor这个数字控制开关作为mosfet;

#3 IC地已默认为GND;如里修改,需对模型进行重新设定;

#4 IC VCC供电压不要直接给一V_DC;由于IC内部有latch电路,直接给V_DC,IC会锁死;需要给一个模拟真实供电电源如V_PWL,即电压由0上升到V_DC并保持。

下面为Saber源文件及测试电路,如有问题还请及时指正,相互学习一下。