之前已经有写过大部分FPGA可支持I/O的标准,可在专题中查看。

FPGA通用I/O

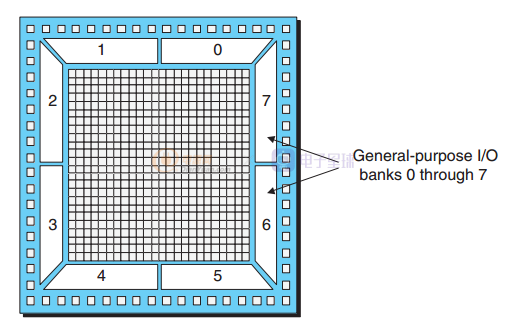

FPGA GENERAL-PURPOSE I/O 这个名称是相对于其他的FPGA的特殊管脚,电源地所称呼的。现在的FPGA封装能够拥有上千甚至更多的管脚。类似地,当涉及到封装内部的硅芯片时,倒装芯片封装策略的出行,允许电源、地、时钟和I/O引脚在芯片表面即可完成。

可配置的I / O的标准

先明确“标准”一词的意义,这里的标准是指的是信号的电气方面,例如它们的逻辑0和逻辑1电压水平。现在我们代入到产品设计工程师的角色,一款产品的工作环境是多种多样的,它可能不需要考虑太低的功耗,但是需要很好的抗干扰性,它也可能需要较高的数据传输,工作环境较好,它也可能需要兼容其他芯片的IO标准。如果按以不变应万变的工作方式来看,这可能变得基本上难以实现且困难的。如果FPGA如上述意义,其I/O的标准是被限定死的,那就得设计出多款标准的FPGA,这对于FPGA厂商来说也是一种灾难。由于上述原因,FPGA的通用I/O被设计成可以配置为接受和生成符合任何需要的标准的信号。当然,这些IO被分成不同的组,每个组可以分别配置不同的IO标准,这在FPGA的特定术语中,被称为“Bank”。如果有8个组的IO,那一般就被称为Bank0-Bank7。

每个Bank的I/O可以分别配置不同的I/O标准。因此,除了允许FPGA与使用多个I/O标准的设备一起工作外,这还允许FPGA实际用于不同I/O标准之间的接口,以及在可能基于特定电气标准的不同协议之间进行转换。

可配置的I/O阻抗

当今的信号设计已经越来越趋于高速,为了解决信号传输方面的问题,例如反射,振铃。传输线之间的阻抗匹配显得极为重要。在可配置阻抗技术出现之前,通常是只用外置电阻,去适配FPGA管脚的阻抗。但是随着FPGA的发展,越来越小的管脚间距,以及越来越多的管脚,这使得外置电阻的方法显得越来越困难。因此,现在的大部分FPGA允许使用内部终端电阻,其值可以由用户配置,以适应不同的电路板环境和I/O标准。

FPGA的电源域

如上文所言,FPGA有多个Bank,支持多个I/O标准,那不同的Bank的电源是怎么分配的?其实,FPGA的电源供电是比较复杂的,一般地,供给FPGA核心电压的叫CORE电压,这个是根据FPGA型号所规定的,比较灵活的就是给各组Bank供电的I/O电压,分别有多个电源管脚分配着各自Bank电压,也就是说,根据这组Bank的I/O电平去分配相应的电压。值得注意的,截止到当今,FPGA的CORE电压,由于晶体管发展技术的限制,大多不能低于1V太多。

下一篇就介绍FPGA的看家绝活,也是很多工程为什么选择FPGA的原因,千兆高速收发器。