逆变器的工作方式和原理相信大家都比较熟悉了,我也是最近几年在电源网逆变论坛的引导才涉足这个圈子的。为什么说这是一个圈子呢?因为它有着和其它开关电源不同的“生活区”。

近几年火爆的LED电源就像生活在雾霾都市里的北京人一样,快节奏工作的同时也在不断创新(减排),基本的拓扑都是APFC+LLC或APFC+QR,随着功率需求不断提高,单级PFC架构的也慢慢消亡,上次还偶然看到了APFC+LCC产品。

一直充实着民用市场的充电器和适配器更是时刻与国际挂钩,适应全电压输入的同时,对效率和功耗的要求也是不断在更新,采用BUCK PFC+LLC+SR的产品也偶尔浮现。

在这些“其它开关电源”行业,近几年出现的新方案拓扑可谓是层出不穷:PSR、交错PFC、BUCK PFC、LCC、LLC……

连载目录:

- 交错控制电路详解

- 输入电压温控详解

- 前级全桥驱动详解

- 前级全桥升压详解

- 后级H桥变流详解

- 后级H桥驱动详解

- 整机辅助电源详解

这几天陆续把这些完成,欢迎大家关注、收藏,不迷路。有问题可以发评论,我会尽量回答大家。

交错控制电路详解

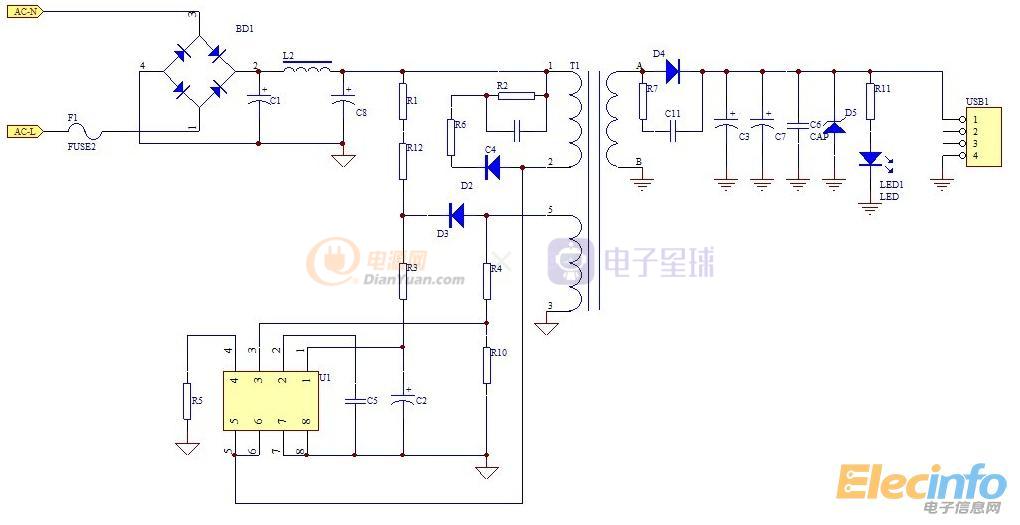

典型的PSR电路

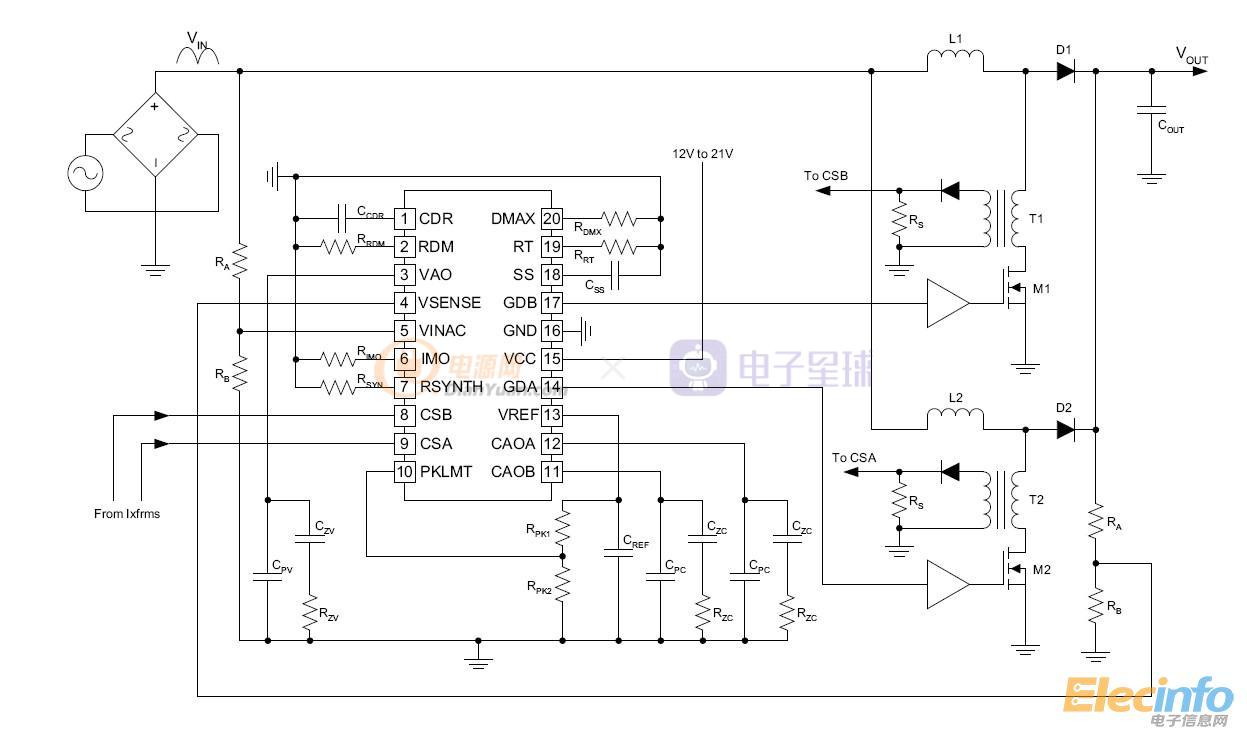

典型的交错PFC电路

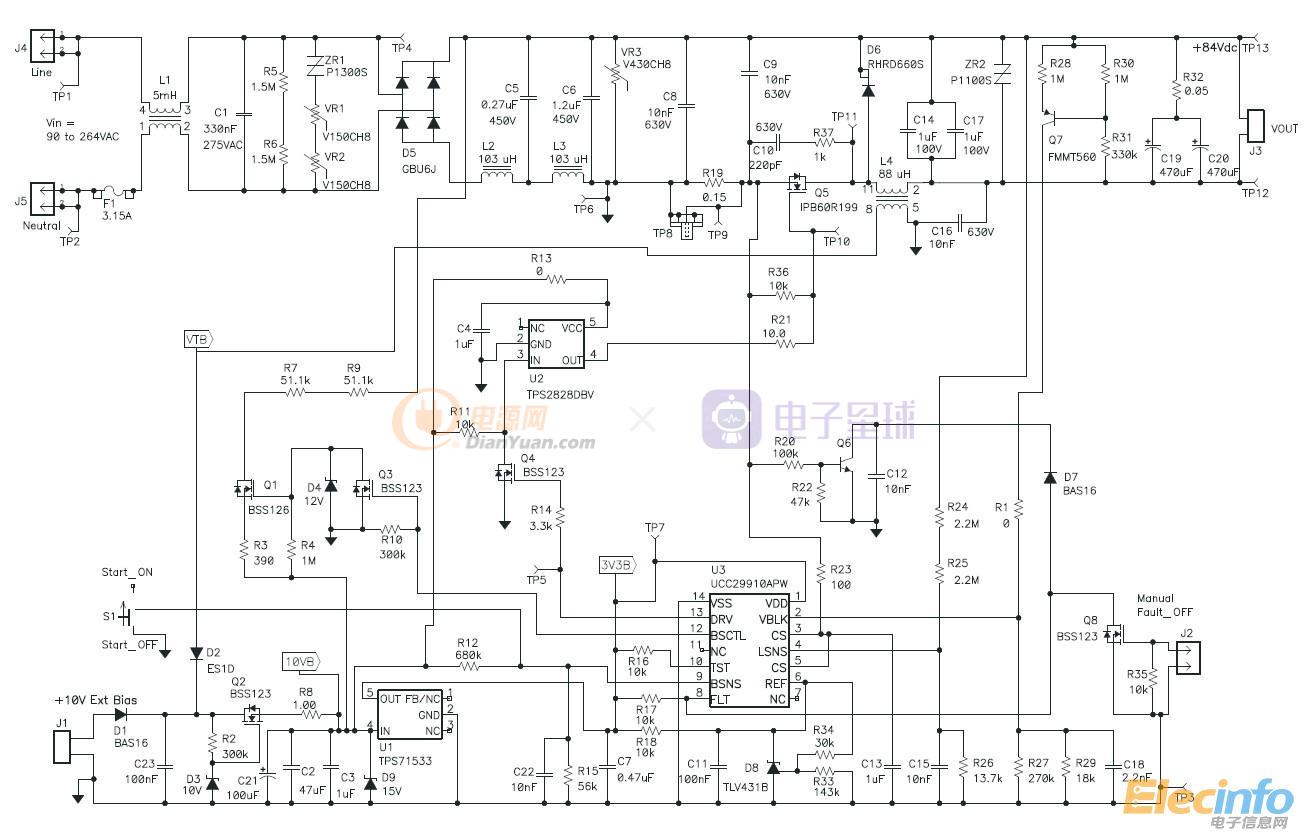

典型的BUCK PFC电路

典型的LLC电路

LCC电路架构图

这些新的拓扑你做过的有多少?

再看看目前的逆变器行业,基本都还是用着比行业工程师平均年龄还老的方案和拓扑,就像生活在深山区里的勤人一样,有着自然的清新空气(风光太阳能市场),有着不必创新而能持续的生活法则。

市场上千篇一律的传统推挽、传统全桥甚至工频方案的逆变器。是什么阻碍了逆变器新技术的发展?

是那几十上百A的电流导致设计上的局限吗?导致电流应力、功率裕量、损耗、偏磁=等设计上的困难?100A左右的电流看起来是不小,但也不至于恐怖吧。

其实我们日常经常接触到这么大电流的产品,只是大家不觉得,电脑的主板CPU供电和显卡的GPU供电电流都是100A+,甚至高达几百A。

目前据说有显卡单卡耗电800W的“电老虎级”专业显卡,按照现在的GPU核心电压1.0V来计算,GPU的供电电流有700+A了\,双卡SLI电流高达1500A+,更恐怖的是普通主板已经支持4路的SLI,显卡耗电流可以达到3000A+。

某品牌主板的37相供电(CPU供电32相交错+CPU内置GPU供电3相交错+VTT供电2相交错。我一直在寻找最适合逆变器的工作拓扑,也做了大量的仿真了和实验。

目前大家常用的多变压器架构还是初级并联次级串联式的推挽架构,这种架构在变压器一致性存在偏差时的影响是不容忽视的,而变压器几乎不可能完全一致。

现在LED电源上用得火爆LLC架构又不适合逆变器输入电瓶端的宽范围电压,需与BOOST配合使用。最后还是想到了电脑CPU和GPU供电电源交错控制,回想起来10年前的电脑主板CPU供电就是3-4相交错式BUCK控制的,现在高端主板的CPU和显卡的GPU供电都达到32甚至64相交错供电了,显卡单卡64相交错,4卡3000A的电流算下来每相也就10A多点了。

让我不明白的是10年前就已经有交错架构的拓扑在应用,虽然BUCK和全桥是有区别,但交错控制原理基本还是一样的,为什么这10多年在电流应力也较大的逆变器行业没有得到广泛的应用呢?交错控制使得再大的电流都不再恐怖了,如果使逆变器可以像显卡组SLI一样,实现直接并联那就完美了。

接下来在交错推挽和交错全桥上也做了些考量和选择,即使是交错式推挽,还是无法避免不对称导致的偏磁,所以准备先拿交错全桥来小试牛刀。

多变压器交错式并联与初级并联次级串联方式的对比,我会写另外一篇文章。

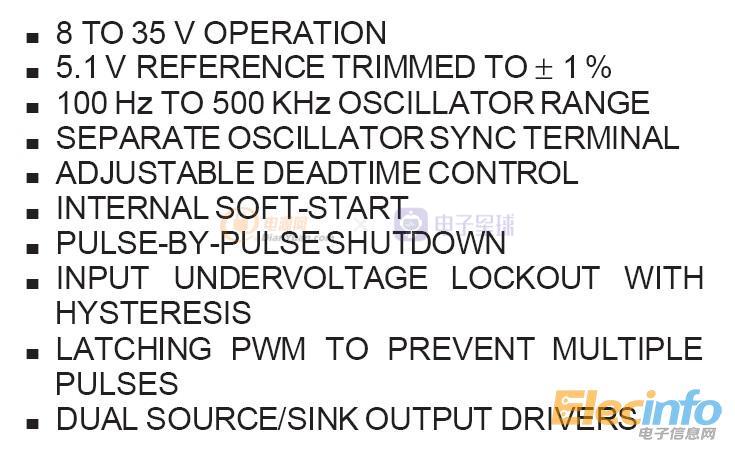

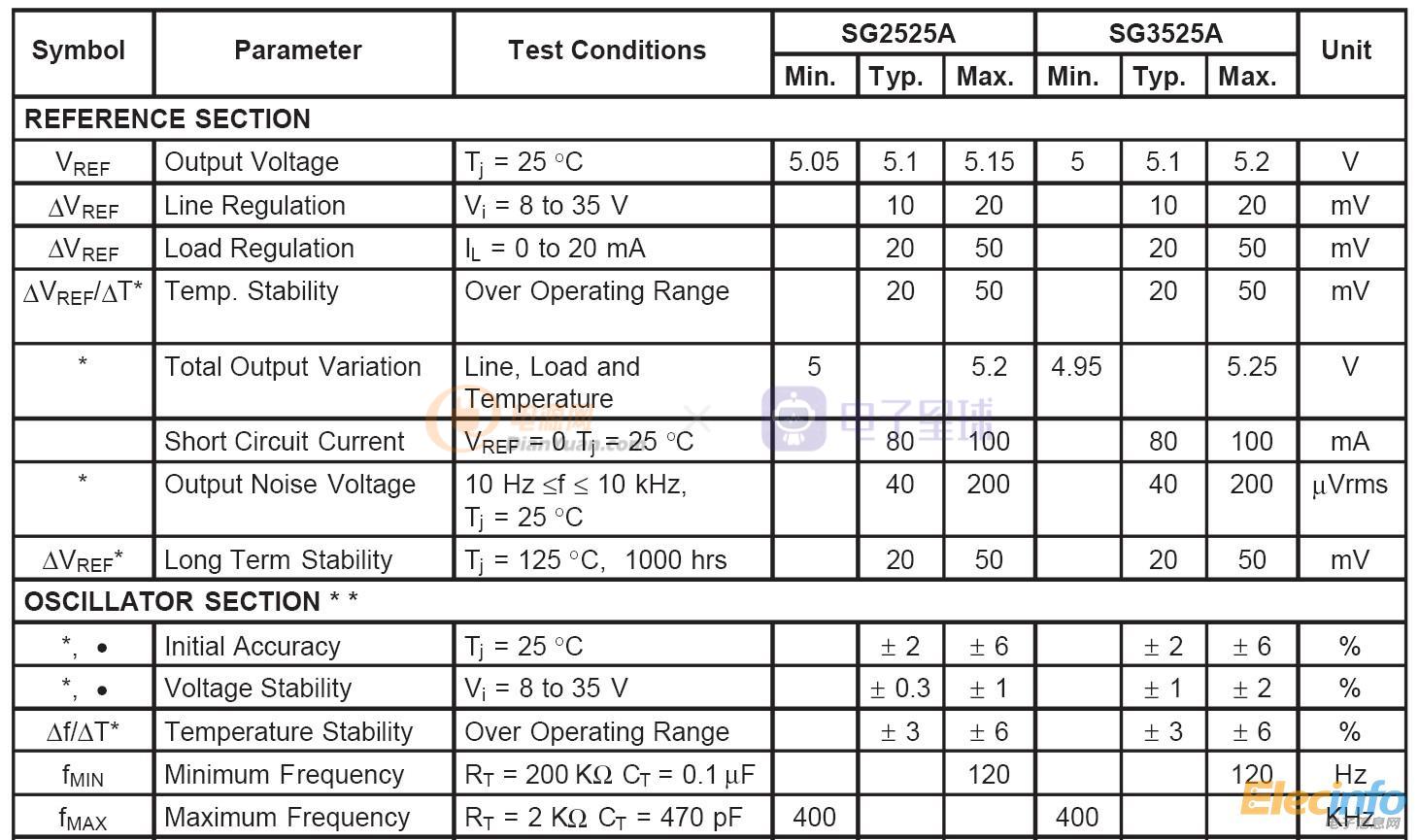

PWM控制IC首选还是大家熟知的SG3525,在这里我选择ST的SG3525A。

相比其他的控制器,它的优点有:

1. 双端最大占空比可以达到98%(实际在30-35K的频率下实测也的确可以达到97~98%之间),这点对开环效率影响还是比较可观的,部分其他品牌的SG3525标称却只有96%。

2. 有同步控制端,可直接级联或交错控制,省去了外置稳定的三角波电路控制的麻烦。

3. 最大工作频率可以达到500KHz。规格书的首页标称的最大工作频率可以达到500KHz,当然实际测试也是可以达到的,只是需要加些外围电路让死区时间为0。在规格书的详细参数中标称却是400KHz,但在交错控制时,同步端的输入信号却又不支持500KHz,所以这个500KHz真心觉得是个忽悠,但这对实现多相级联式交错非常有用,400KHz实现一般的逆变器(30-35KHz 开关频率)4相交错还是没问题的。

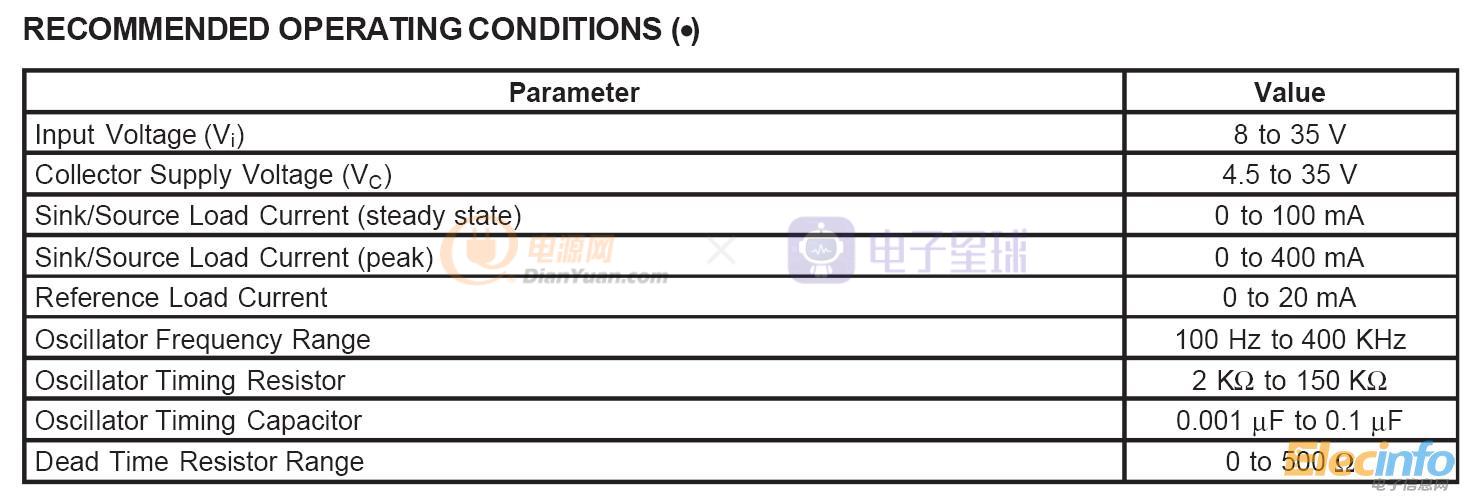

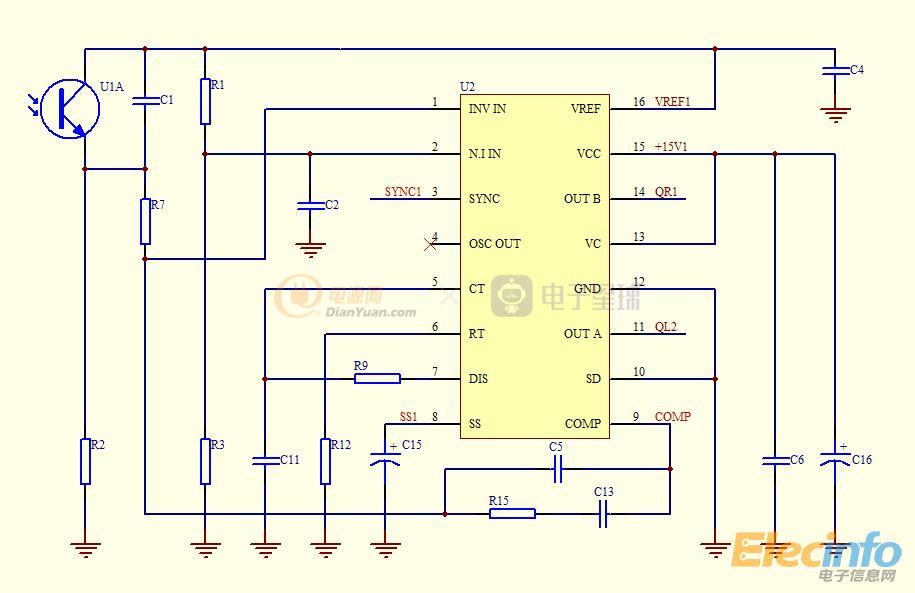

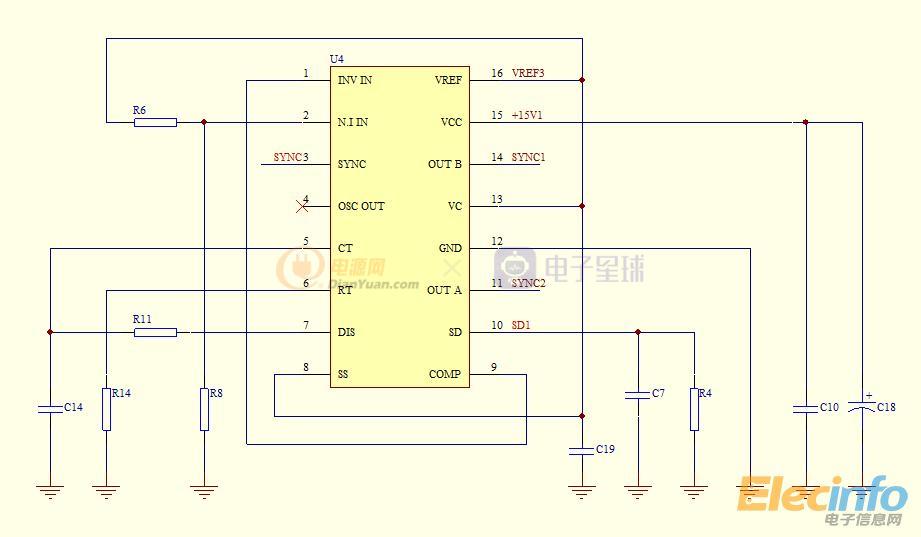

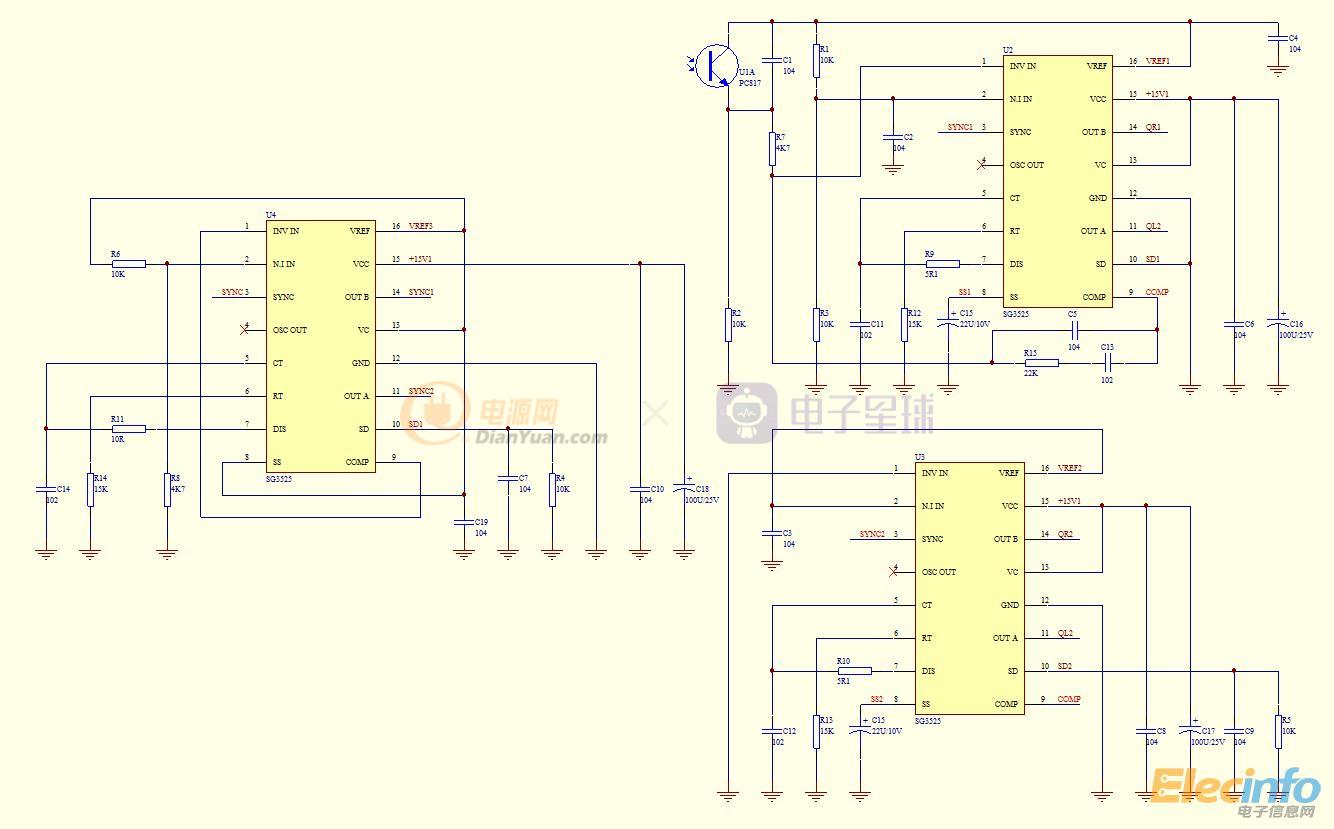

先上交错控制部分的电路图,说说交错的核心。

主路的PWM控制

副路的PWM控制

本质上2路PWM是可以部分主和副的。但为了节省外置运放反馈,利用其中一个PWM控制器内部的运放作为反馈。同时,为了实现在轻载降频的同时关闭其中一路PWM来减小待机功耗,所以在这里就分了主副来区分。

2路PWM的区别:

1. COMP端直接并联

2. SS端分开

3. SD端分开,且主路SD直接屏蔽掉。

4. CT/RT/DIS同样参与开关频率的设置。

5. 主路的内部差分运放实现反馈,副路的内部运放直接屏蔽掉。

一个一个的区别来讲解:

1. COMP端直接并联。

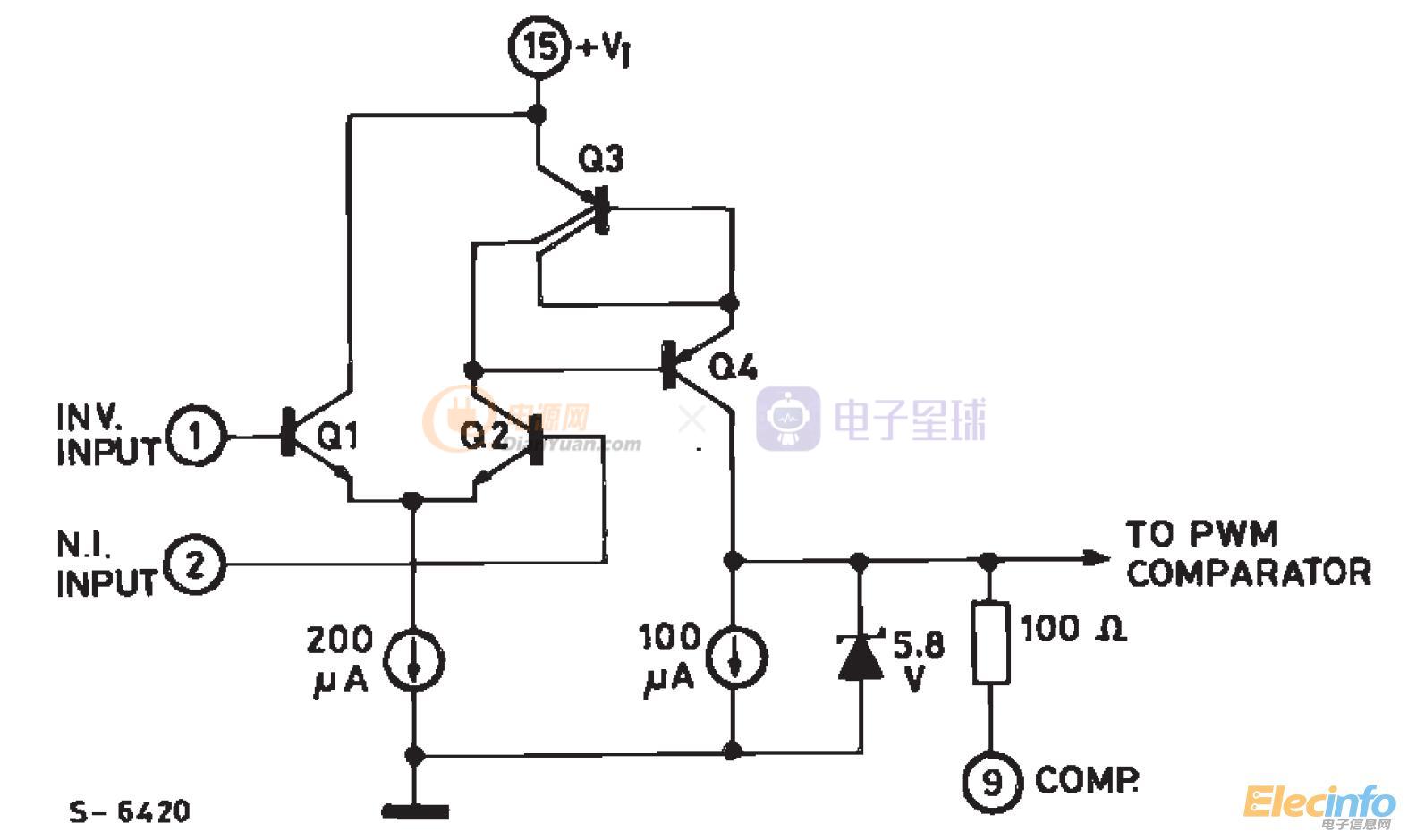

先贴一张SG3525的内部构造图看看COMP端的的区域

从这里看,COMP端是内部差分运放的输出端,由于采用的是主路的内部运放负反馈的方式,所以要让副路的内部运放屏蔽的同时令其输出高电位,通过负反馈下来来实现控制。

再看看COMP端的详细构造:

在COMP端内部,并不是差分运放直接输出到COMP,而是串联了一只100R的电阻。

这个电阻带来的问题是主负路的TO PWM COMPARATOR会出现很小的差异,等效为主路是差分运放直接输出到主路的内部TO PWM COMPARATOR,而副路的则需要通过1个100R的电阻到达并联的COMP端后再通过1个100R的电阻到达内部的TO PWM COMPARATOR,2个100R的电阻上会产生一个小小的压降,实际表现为在闭环状态是主副路的占空比会有很小的差异。但这对准开环架构的逆变器没有任何影响。

当然,如果是做闭环架构,建议还是用外置运放来同时控制2路的COMP端,这样能保持2路的PWM占空比尽量一致(2个3525内部运放本身的误差忽略的情况下)。

2. SS端分开

实际实验在控制3525保护时,直接控制SD端会导致恢复时非常大的电流冲击,从而导致功率MOS瞬间炸管。原因是因为直接关闭SD端后再次开启时3525是直接输出最大占空比的,这个瞬间是不受控的。

所以,我通过关闭SS端来实现保护,再次开启时会进入软启动状态,大大缓解了对功率MOS的电流冲击。在软启动时,即使2路的PWM软启有20%的时序误差影响也不大。

2路分开以后,就可以实现在轻载或空载时关闭其中1路,实现低的待机的同时,再次开启时也是软启动的。

3. SD端分开,且主路SD直接屏蔽掉。

上面已经说了保护是通过SS端来实现的,那么主路就不需要再强制关闭了,所以主路的SD端直接接地屏蔽掉,而副路的SD端需要用来在轻载时强制关闭。

4. CT/RT/DIS同样参与开关频率的设置:

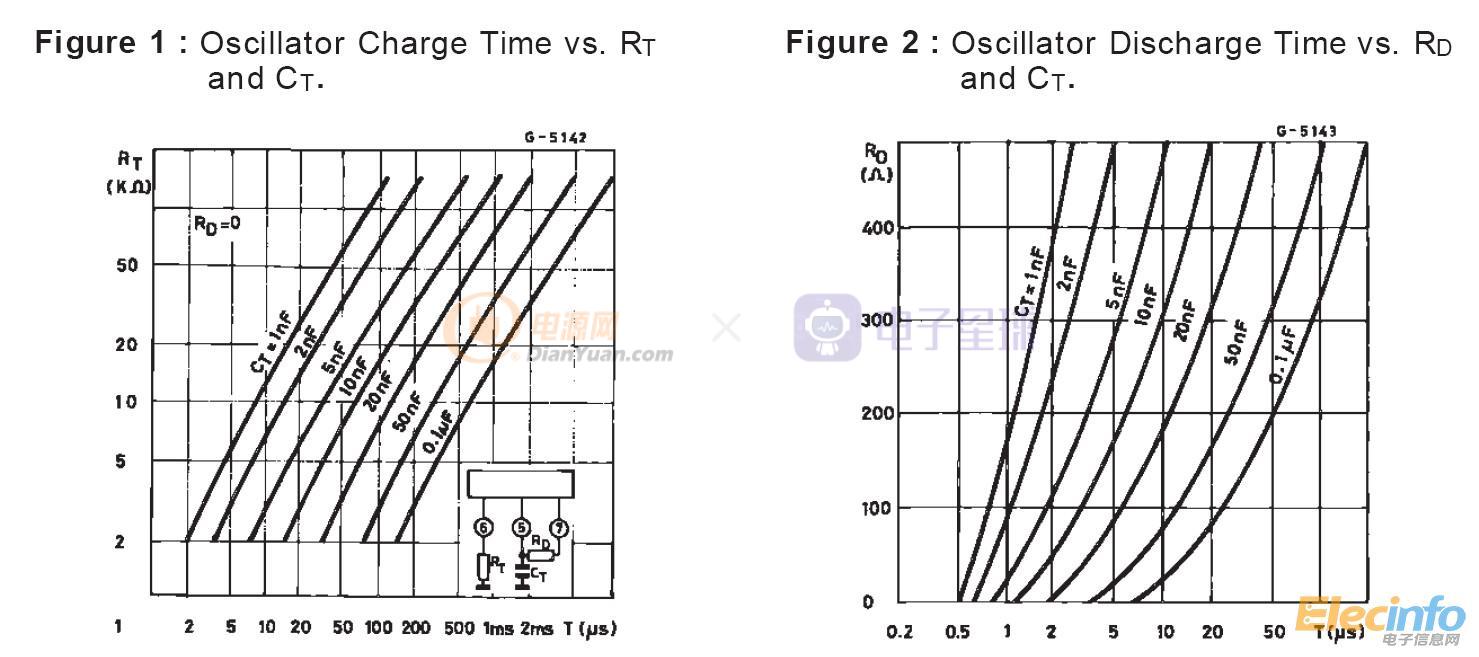

先贴2张CT/RT/RD的曲线

在规格书给出的曲线中,我们可以看出以下几个问题:

在规格书给出的曲线中,我们可以看出以下几个问题:

1. 即使RD=0,死区时间也不为0。

2. 推荐的最小震荡电容CT=1nF。

3. 在CT=1nF,RD=0时,死区时间最短,为0.5uS。

在开环状态下,需要追求最大占空比,所以这里的CT=1nF,RD可以适当选取小点的阻值,这里我用5.1R。

设定的频率由下面的公式计算得来:

由于震荡频率与交错的同步频率有关,所以RT的取值在后面的同步频率的计算中再来计算。

5. 主路的内部差分运放实现反馈,副路的内部运放直接屏蔽掉。

看了第1点这个就应该清楚了吧。

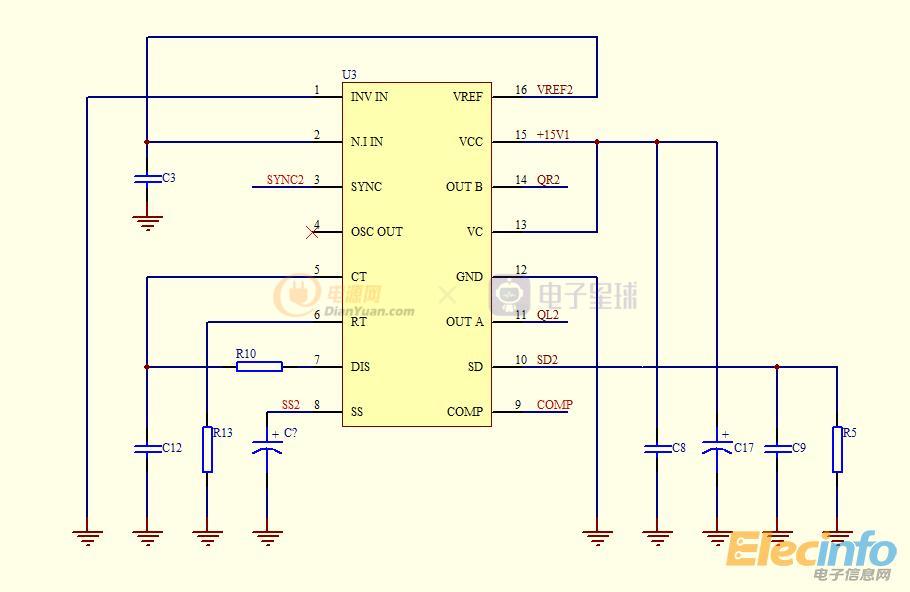

下面再上交错信号源的SG3525电路:

这里有以下几个特点:

1. SD1端可控。

2. 内部差分运放连接为跟随器形式。

3. SYNC端预留。

4. CT/RT/DISS(RD)设置震荡频率。

5. VC端接VREF。

6. OUT A/B输出到主副路的SG3525 SYNC端。

1. SD1用来关闭信号源,关闭后控制PWM的2个SG3525就是同步并联的了,而且开关频率不再受控于信号源,而是主副路SG3525的自身震荡产生的PWM。在轻载时关闭副路的同时关闭交错信号源的SG3525,可以降低开关频率,进一步减小功耗。

2. 内部差分运放连接为跟随器的形式,COMP端的的电压,COMP端的电压决定了OUT A/B端的PWM输出占空比。所以通过设置P2 端的R5和R8就可以控制输出的占空比大小。在此得吐槽一下SG3525的SYNC端对输入信号占空比的要求,真是有点高。

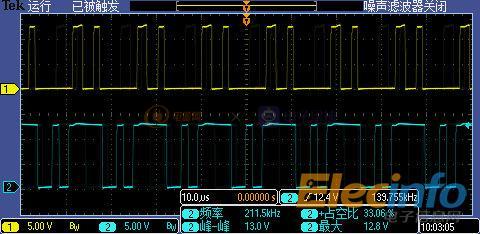

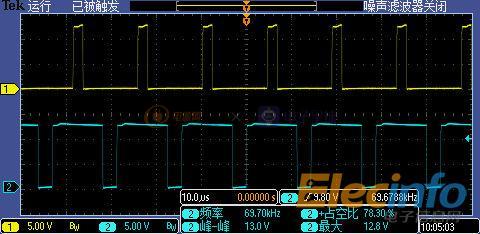

同步端的交错信号占空比太小后就无法同步了,不受控与同步端了;同步端的交错信号占空比太大后,输出的PWM就乱了,如下图:

经过反复的实验得出,要实现同步,同步信号的占空比必须控制在3%~12%之间。

而且在12-13%时会出现混乱,现象如下图:

所以,这里取折中,设置占空比在6-8%,再来看看输出PWM端的波形:

控制主路SG3525的差分运放来减小占空比,波形如下:

再减小。

到此,交错同步的问题得到完美解决。

3. SYNC端预留。

这个是用来实现级联的,也就是说:可以再扩展为4相交错甚至8相交错(8相交错时需要降低开关频率)

4. CT/RT/DISS(RD)设置震荡频率。

这里再来讲讲3个SG3525的震荡频率设置的讲究。

SG3525的同步频率要是被同步IC的震荡频率的1.3倍以上,是输出的开关频率2.6倍以上才能正常稳定的工作。所以要使开关频率在35KHz左右,交错信号源的SG3525的输出频率为70KHz左右,其震荡频率就需要140Khz左右,同时,主副路的SG3525的震荡频率要为同步频率的1/1.3,即53.8KHz左右,这里取50KHz,频率根据59帖的公式计算即可。

高清大图贴上交错控制单元的线路图和参数:

5. VC端接VREF。

因为主副路的SG3525 SYNC端识别的高电平为5V就可以了,所以这里把交错信号源的SG3525的输出供电端接到了自身的基准5.1V上。

6. OUT A/B输出到主副路的SG3525 SYNC端。

交错信号源的输出信号作为主副SG3525的震荡频率,从而控制PWM的输出频率。