升压转换器设计

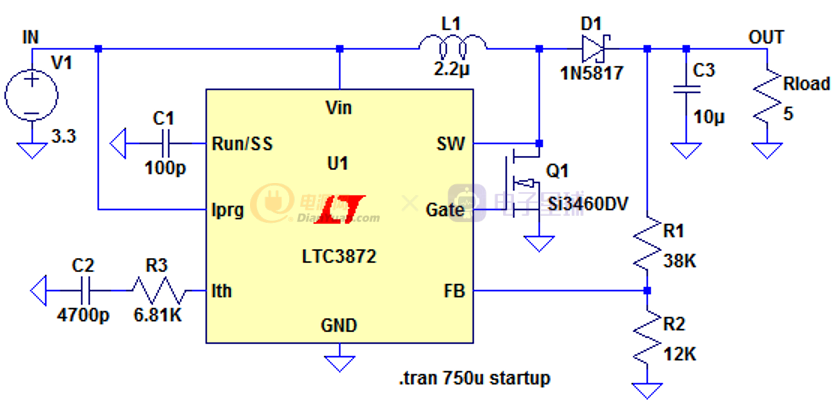

考虑升压转换器的架构,如图 1 所示。

图1

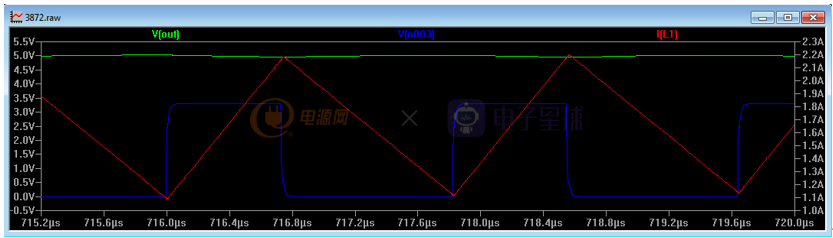

忽略组件 C1、C2、R3。MOSFET Q1 开启,在电感器右侧 L1 和 0V 之间形成短路。因此,在电感两端施加 3.3V 的固定电压,因此其电流将根据

或者

或每秒 150 万安培。因此,如果 MOSFET 在 1us 后关断,则通过电感器的电流将上升 1.5A。

当 MOSFET 关断时,电感器会尝试保持其电流流动。它通过在其端子上产生一个非常类似于电池的电压来实现这一点,其中电流从负极端子流过电池,流到正极端子。

在图 1 的电路中,我们可以看到,为了保持电流流动,电感器右侧的电压必须相对于左侧增加。左侧连接到输入电压(因此不能改变),因此右侧电压增加到高于输入电压并继续这样做,直到某些东西导电。理论上,这个电压会上升到一个无穷大的值,使得电感非常擅长从低电压产生高电压。

在图1中,电感电压增加,直到二极管D1导通,然后电感中的能量流入输出电容器C3,导致C3两端的电压略有增加。值得注意的是,即使在 MOSFET 开始开关之前,也有一条直流路径从输入端通过 L1 和二极管 D1 流入 C3,因此在启动时,C3 两端将有一个电压(等于 Vin – Vdiode)。

当 MOSFET 关断且电感放电时,电感仍按照

除了这次,电感两端的电压等于 Vout – Vin(忽略二极管压降)。

当电感放电时,MOSFET 导通并重新开始该过程。重复此过程会产生从电感到输出电容器的能量脉冲,从而使输出电容器两端的电压上升。在图 1 中,电阻器 R1 和 R2 监视输出电压,当 FB 引脚上的电压达到某个点时,芯片终止对 MOSFET 的驱动,直到输出电容器上的电压下降。

可以在文末下载该电路的 LTspice 模型:LTC3872 升压转换器

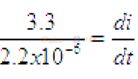

LTspice 仿真结果如图 2 所示。这里我们查看的是输出电压上升到 5V 后运行的部件。

图2

蓝色波形是 MOSFET 的栅极电压。当 FET 开启时,电感器电流(红色)在 739ns 内从 1.09A 上升到 2.18A(这可以在 LTspice 中测量),或者以每秒 147.4 万安培的速率上升,接近我们上面计算的值。这种差异是由于 FET 不提供真正的对地短路,而且在接通时实际上它两端的电压约为 50mV,从而降低了电感两端的电压。

同样,当 FET 关闭时,电流在 1.083us 内从 2.18A 上升到 1.09A。从方程

一旦输出达到稳压,电感两端的电压为 [(5+Vd) - 3.3],其中 Vd 是二极管两端的电压(约 0.5V),因此我们可以计算电流斜坡为

或每秒 100 万安培。在 1.083us 期间,电流下降 1.083A,因此我们的 LTspice 模拟再次非常接近计算值。

有趣的是,di/dt 的值仅由电感值和电感两端的电压决定。控制器 IC 与设置电感斜坡电流无关。

计算占空比(FET 的导通时间与总振荡周期的比率)也很有用。

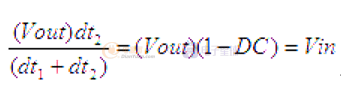

再次从等式

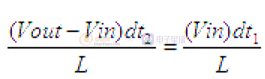

我们可以看到,在斜坡上升期间,电感电流 di 表示为

其中 dt 1是 FET 的导通时间,Vin 是输入电压。

在斜坡下降期间,电感电流表示为

其中 Vout 是输出电压,dt 2 是 FET 的关断时间。为了让生活更轻松,我们忽略了二极管压降。

对于固定输入电压和固定输出电压,di 在斜升和斜降时相同。

因此,等价 di 给出

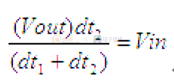

由此我们可以计算

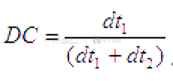

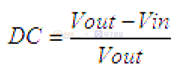

现在,我们的占空比 DC 表示为

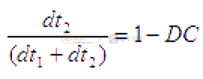

因此

所以

所以从那里我们可以计算出

同样,占空比仅由输入和输出电压设置。电感值不会影响占空比的设置,控制器 IC 也不会。

只要电感中的电流不降至零,上述情况就成立。这称为连续传导模式 (CCM)。如果电感电流降至零,则上述占空比方程不成立,控制器进入断续导通模式 (DCM)。

在 CCM 中,如果负载电流增加,占空比保持不变(在稳定状态下)。电路通过保持占空比恒定对负载电流的增加做出反应,但电感电流的中点(其直流偏移)增加。开关频率和电感纹波电流的幅度保持不变。在图2中,电感电流的中点约为1.65A,纹波幅度为1.1A。如果负载增加,中点电流会增加,但电感纹波电流仍为1.1A。

在升压转换器中,平均输入 电流等于平均电感电流。图 1 的电路产生 5V 输出到 5 欧姆 (1A),因此我们有一个 5W 负载。如果我们假设转换器的效率为 90%,这意味着我们需要输入功率为

输入电压为 3.3V,这意味着电流为 1.68A。我们可以从图 2 中看到,平均输入电流约为 1.68A。

升压转换器设计程序

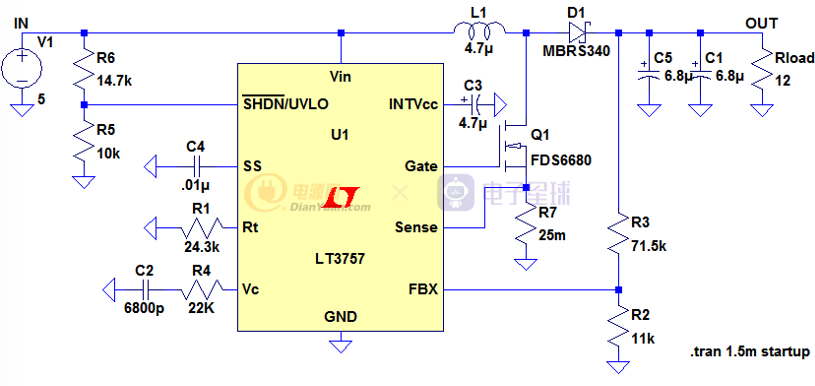

下面是一个使用上述理论的工作示例。它基于通用升压转换器 LT3757(LT3757 数据表在ADI官网下载)。

我们的简介是设计一个升压转换器,将 5V 转换为 12V 并提供 1A 的负载。输出纹波应小于 2%。开关频率需要约为。500kHz。我们可能会施加这个开关频率,以确保 DC/DC 转换器的工作频率与电路中其他敏感电子设备的频率不同。此外,通常更快的开关频率会导致更小的电感器尺寸,但电路中的开关损耗会增加,因此 500kHz 通常是确保良好效率的最佳点,但组件较小。

电感选择

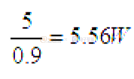

对于 12V/1A 输出,这代表 12W 的负载。数据表的第 1 页显示我们的效率将达到 90% 左右,这意味着我们的输入功率为:

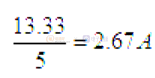

对于 5V 输入,这表示平均输入电流为

电感的最佳纹波电流为输出电流的 40%。对于大多数 DC/DC 转换器来说,这是一个很好的经验法则,代表了小电感器尺寸和低开关损耗之间的权衡。

我们的电感电流为 2.67A,因此对于 40% 的纹波,峰值电流需要为 (2.67 x 1.2 = 3.2A)。我们的最小电感电流需要为 (2.67 x 0.8 = 2.14A)。这导致电流变化为 (3.2 – 2.14 = 1.06A)。

我们知道我们的占空比表示为

这是

500kHz 的开关频率具有 2us 的周期,因此 MOSFET 导通

(此时,值得检查控制器的最小导通时间,看看我们是否符合规范。LT3757 的最小导通时间为 220ns,所以我们没问题)。

我们已经计算出我们的电流需要改变 1.06A,所以我们的电流随时间的变化是

当 MOSFET 导通时,电感两端的电压等于我们的输入电压 (5V),因此我们可以从中计算出电感值

所以我们的电感值计算为 5.47uH。

现在,如果电感中流过太多电流,它所缠绕的铁氧体就会饱和,其电感值会迅速下降。由上式可知,如果电感减小,电流随时间的变化增加,过流的影响会恶化,所以我们必须确保我们选择的电感是额定处理电流的。因此电感的饱和额定值需要超过 3.2A 的峰值电流。3.5A 的饱和额定值就足够了。

Wurth Electronics 有 2 种合适的解决方案(可以使用 Wurth Electronics 元件仿真软件找到):

零件编号值饱和电流

744774047 4.7uH 5.5A

744774068 6.8uH 5A

这些组件中的任何一个几乎没有区别,因此将选择 4.7uH,因为它更接近。

Rsense 计算

检测电阻器馈入控制器内部的 PWM 引擎,并确定可以流过电感器的最大电流。电感电流流过检测电阻,在其两端产生斜坡电压。如果该电压超过 100mV(参见数据表),MOSFET 将关闭以保护周围电路免受过电流影响。

我们在上面计算出我们的峰值电感电流为 3.2A,因此必须选择我们的检测电阻,使该电流不超过 100mV(最坏情况规格)的检测阈值。

为了允许 20% 的裕量,我们假设电流检测跳闸阈值为 80mV。对于 3.2A 的峰值电流,这意味着检测电阻值为 25mOhms。将其放回到 100mV 的数据表规范中,这意味着我们最坏情况下的电感器电流将为 4A,远低于我们电感器的 5.5A 额定值。

MOSFET 选择

MOSFET 需要能够处理峰值电感电流,因此在本设计中,10A 的漏源电流额定值 (Id) 就足够了。漏源电压 (Vds) 需要超过输出电压 + 二极管压降,因此任何高于 20V 的电压都适用于 12V 输出。

MOSFET 的栅源开启电压 (Vgs) 需要小于输入电压,以确保从 Gate 引脚出来的电压能够真正激活 MOSFET。逻辑电平 MOSFET 具有低导通电压,应用广泛,通常非常适合低压 DC/DC 转换器。

上述参数代表了 MOSFET 的最低限度的特性。但是,要获得良好的设计,我们必须确保 MOSFET 中的损耗尽可能低。MOSFET 开关在电路中存在两种损耗:开关损耗和传导损耗。

在 MOSFET 的导通和关断期间,开关损耗是由流经 MOSFET 的电流和 MOSFET 两端的电压(因此在 MOSFET 中产生功率)的同时产生的。对于来自控制器 IC 的给定栅极驱动器,MOSFET 的栅源电容越低,MOSFET 开启的速度就越快。因此,MOSFET 的 Qg 规格很重要,应尽可能低。MOSFET 的 Qg 也会对芯片的散热产生影响,尤其是在芯片的输入电压较高的情况下。

电荷由等式决定:

电荷 (Q) = 电流 (I) x 时间 (s)

由于频率是时间的倒数,我们可以写成

所以我们可以计算流入芯片所需的电流,只是为了给 FET 的栅极电容充电。由于热量是电压和电流的乘积,如果栅极电荷高和/或开关频率高,那么如果输入电压高,芯片中的散热就会很高。

一旦 MOSFET 导通,MOSFET 的漏极和源极端子之间就会出现一个小的直流电阻。这是 MOSFET 的“电阻上的漏极源”或 Rdson。同样,这需要尽可能低。

现在,MOSFET 制造商通过在 Drain 和 Source 之间构建许多并行传导路径来降低 MOSFET 的导通电阻。因此,就像并联电阻一样,导通电阻随着更多的并联路径而下降。然而,在并联连接漏源路径时,负面影响是栅源电容 (Qg) 也并联连接,因此低导通电阻(因此导通损耗低)有时意味着高栅源电容(因此高开关损耗)。因此选择的 MOSFET 应该是这两个特性之间的折衷。此外,大电流 MOSFET 往往采用更大的封装,因此,满足低导通电阻和低 Qg 的理想可能会违反空间要求规范,因此选择过程必须重新开始。工程,一如既往,是一种妥协。

确实看MOSFET厂家的选型表,最好选择导通电阻低(小于10mOhms)的MOSFET,然后过滤这个选择,去掉Qg大于10nC的MOSFET,然后从中选择MOSFET列表中,只要Gate开启电压,Vds和Id就可以满足。首先选择 Vds 介于 20V 和 30V 之间的 MOSFET 可能会排除一些更适合较低电压设计的较高电压 FET。如果失败,请将所有结果下载到电子表格并从那里进行排序。在 MOSFET 网站上进行参数搜索时,我从来没有这么幸运过。

或者,将所有 MOSFET 特性下载到电子表格中,删除不符合 VDS 和 ID 要求的特性,然后添加名为 FOM(品质因数)的列。此列应包含值 RDSON x QG。然后按此列排序并选择 FOM 最低的 FET。这部分将是 RDSON 和 QG 之间的最佳折衷,是顶级 MOSFET 的理想选择。

如果不能满足低导通电阻和低 Qg 的理想,请查看占空比。如果输出电压不比输入电压高多少,那么占空比就会很低,因此 FET 的导通时间在总开关周期中所占的比例很小。因此,低 Qg 更为重要,而低导通电阻则不太重要。同样,高输出电压意味着高占空比,因此低导通电阻比低 Qg 更重要。

Fairchild FDS6680 代表了低导通电阻和低栅极电荷之间的良好折衷,但其 SO8 封装较大,因此可能不适合紧凑型设计。

整流二极管选择

当 MOSFET 关断时,电感电压迅速上升以保持电流流动。许多二极管的反应速度不够快,无法对这种电压变化做出反应,从而导致 MOSFET 的漏极出现大尖峰。这可以(并且确实)破坏 MOSFET。

因此,肖特基二极管应用于所有必须对电感电压进行整流的 DC/DC 转换器设计。超快二极管的响应时间为 10 纳秒,标准整流二极管的响应时间为几微秒,而肖特基二极管的响应时间为几纳秒。与标准整流器 (0.6V) 相比,肖特基二极管的正向压降 (0.3V) 也低得多,因此 VxI 损耗会浪费一半的功率。

选择肖特基二极管时,关键参数是:正向压降(应尽可能低)、正向电流(应大于电感峰值电流)和额定反向电压。当场效应管给电感充电时,肖特基二极管的正极为0V,负极为Vout,因此肖特基二极管的反向电压额定值应大于Vout。

在本设计示例中,MBRS340 是一个不错的选择,它在 3A 峰值电流下具有 40V 的额定反向电压和 0.53V 的正向电压。

输出电容选择

与具有从电感器流入输出电容器的连续电流的降压转换器不同,升压转换器输出电容器必须在电感器充电时(因此与输出断开连接)保持输出电压有效。因此,由于输出电容器的放电,将存在输出纹波的分量。

此外,当电感放电时,输出电容会出现浪涌电流,电容中的任何 ESR(有效串联电阻)也会导致纹波。

因此,输出纹波由 2 个分量组成:电感器充电时输出电容器放电引起的纹波和从电感器进入输出电容器 ESR 的浪涌电流引起的纹波。设计规范规定输出纹波需要小于 2%。对于以下计算,假设 1% 的输出纹波是放电纹波,1% 是 ESR 纹波。

电感充电时输出电容放电引起的纹波由下式决定

其中i是以安培为单位的负载电流,C是以法拉为单位的输出电容,dv/dt是输出电压随时间的变化。

早些时候我们计算出 MOSFET 导通时间为 1.16us。如果我们需要 1% (120mV) 的放电纹波和 1A 的负载电流,这意味着我们需要一个电容为

或 9.66uF。

请注意,当电感充电时,整流二极管中流动的电流为零。当 MOSFET 关断时,二极管电流从 0A 跳到峰值电感电流,因此是峰值电感电流,而不是纹波电流幅度决定了输出纹波的这个分量(与降压转换器中的纹波相比,由纹波电流幅度决定,而不是峰值电感电流)。

ESR 引起的纹波是峰值电感电流和 ESR 的乘积。在我们的示例中,峰值电流为 3.2A。典型的钽电容器的 ESR 约为 70m 欧姆,产生 224mV 的纹波。两个并联的电容器使 ESR 减半,但使电容加倍,因此产生 35m 欧姆的有效 ESR 和 112mV 的 ESR 纹波。

陶瓷电容器的 ESR 低得多(约 10m Ohm),因此如果使用陶瓷输出电容器,ESR 纹波会显着降低。

因此,两个 6.8uF 钽电容器,每个具有 70m Ohm 的 ESR 将产生 112mV 的 ESR 纹波和 85mV 的放电纹波。因此,总纹波为 197mV,小于设计规范的 2% 纹波。

反馈电阻选择为 11k 和 71.5k,以便 12V 输出将反馈点保持在 1.6V。一些工程师将这些电阻值设置得太大,以期节省反馈回路中的浪费电流。然而,这可能会产生负面影响,因为过高的电阻值(超过 500k 欧姆)会导致反馈引脚的内部电容和较大的外部电阻值产生相移,从而导致稳定性差。在低功率设计中(反馈电流很重要),通过提供一个相位超前来抵消输入电容产生的相位滞后,用 100pF 旁路顶部反馈电阻器克服了这个问题。

有关如何设置欠压锁定 (UVLO) 和开关频率的信息,请参阅数据表。

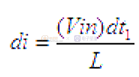

最终的 LTspice 电路如图 3 所示

图3

LTspice 电路可在文末下载: LT3757 升压转换器

本文解释了升压转换器开关模式电源设计的基础知识,适用于大多数升压转换器。有关使用该特定部件进行设计的完整指南,请参阅各个数据表。