大家好,我是广元兄。很高兴和大家分享传输线的相关知识。希望大家点赞,分享。有什么问题加微交流学习,微信号【SI_Basic】。Slogan:一起学习,共同进步!

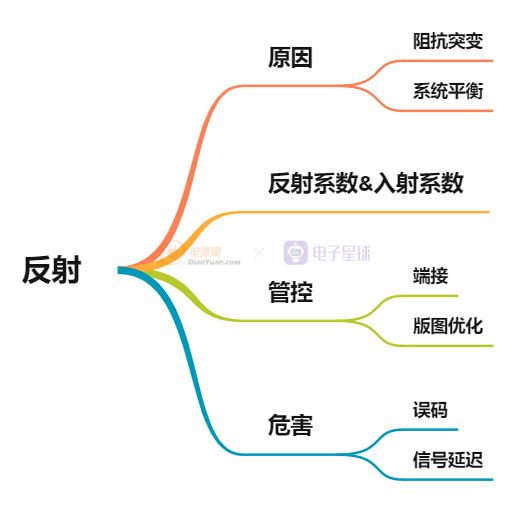

信号完整性方向,传输线问题三大点:反射、串扰、损耗。

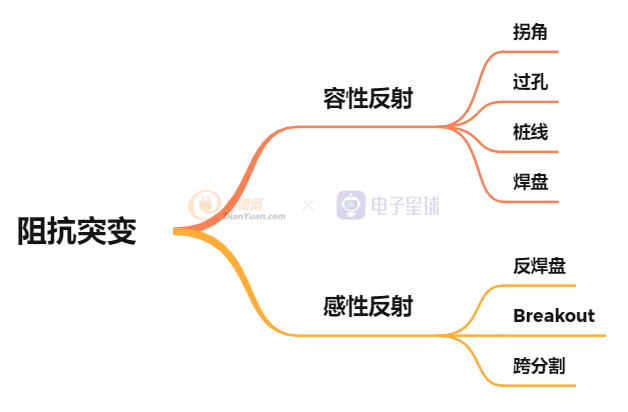

本文讲反射,思维导图如下:

01

反射是不可避免的。

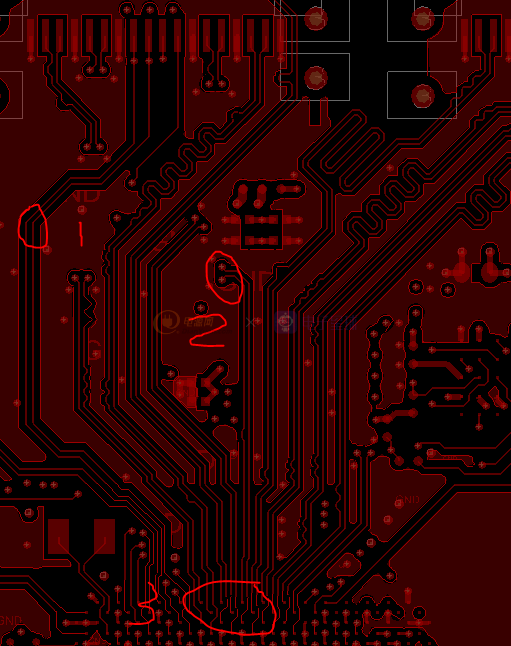

互连链路中瞬时阻抗一旦变化,产生阻抗突变,就会发生反射。下图为日常的版图设计走线:

阻抗突变在版图设计中不可避免,那为什么阻抗突变就会发生反射?

下图红色标记处为突变点,交界处(很短的距离差之内)的电流电压是有差值的,如果这时候没有反射,随着时间的积累,将产生巨大的能量场。

为了维持系统的平衡,交界处必须要发生反射,以此达到电压和电流的连续。

02

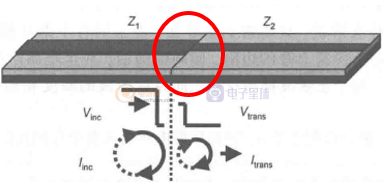

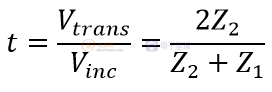

信号传输,阻抗突变处,一部分继续传输,一部分反射回源端,用传输系数和反射系数衡量这两种情况。

入射系数:

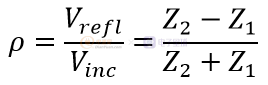

反射系数:

参考反射系数公式,可推出三种极端情况:

1.ρ=0,代表阻抗完全相等,交界处没有反射。

2.ρ=1,代表完全正反射,交界处产生幅值相同相位相同的反射波。开路端电压为两个电压之和。

3.ρ=-1,代表完全负反射,交界处产生幅值相同相位相反的反射波。突变处电压为0。

实际工作中,以此对应传输线端接的三种的情况:开路,短路,匹配。

一般情况,反射系数在(-1,1)范围内,也就是正负反射交替,这便是振铃现象。

视频讲解:反射

03

既然阻抗突变不可避免,都有哪些情况?总结如下:

特别提一下过孔/桩线,随着产品的高速化,很多Stub都做了Backdrill的处理,来控制反射,优化阻抗突变。这里面对高速率产品有需要考虑PCB工艺的误差。

至于什么时候考虑Backdrill,可以参考经验公式,一般PCIe GEN4就需要做背钻处理了。

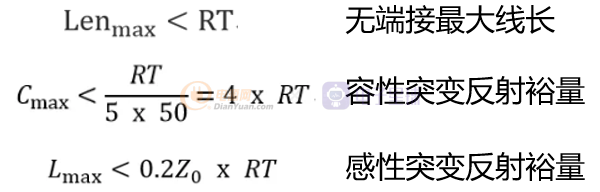

那是不是传输链路中一有阻抗突变是不是就考虑端接?也就是说什么情况需要管控?

参考相关经验公式:

04

其实在设计规范文档,也给出相应的管控方案。比如会给出相应拓扑结构,以及各种拓扑结构端接的阻值,来做阻抗匹配,抑或是从DDR3开始有的ODT功能,通过端接电阻,来吸收能量,抑制反射。

端接的形式有多种:串联端接,并联端接,RC端接,戴维宁端接等。

串并联端接,简单来说,就是串联一个电阻,使源端阻抗和传输信特性阻抗匹配,抑制反射。

戴维宁端接通过上拉或下拉的端接,抑制振铃,但会增加功耗。

RC端接中的电容就是管控功耗,但增加的电容会对信号质量产生影响。

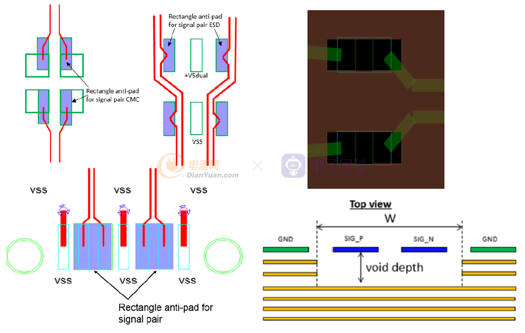

除了电路上的管控,PCB板级中版图设计的优化也可以减小阻抗突变,典型的处理方式就是器件邻平面层进行挖空(Voiding)。

05

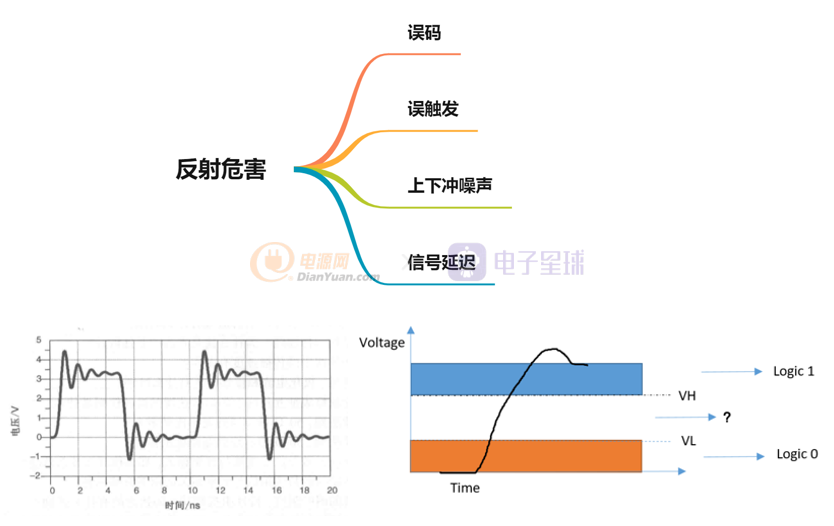

讲到最后,那反射的危害有哪些?

任何对高速信号完整性产生危害的因素,我们都要进行管控,有些危害不可避免,我们所要做的就是优化和保证危害在链路的合理范围之内,不过度设计也不过度试探风险的底线。

其实信号完整性的管控,应该是多方面的,从开始原理图或者芯片端设计,到PCB板级的部分,再到终端测试和验证部分,是整个系统级的管控。