大家好,我是硬件微讲堂。

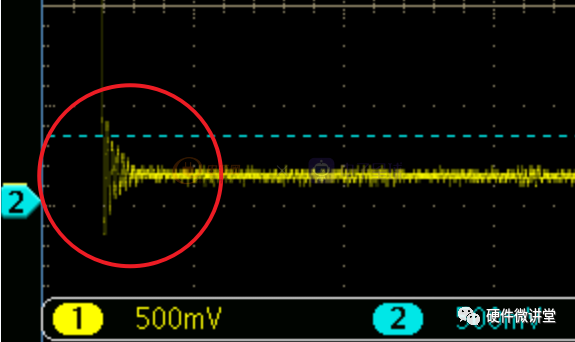

前两天做测试,碰到下图这样的波形。其实,在信号线或者开关波形上,经常会有类似振铃出现,不晓得你有没有思考过为什么。今天我们就在这里聊一聊振铃。

一道面试题

照例,先抛出来一道面试“信号的振铃有没有遇到过?有考虑过为什么吗?” 怎么样?看似随口一说的问题,但往往暗藏玄机。

自我感觉良好的答案

有些小伙伴会觉得:这个问题简单,当然不在话下。信号出现振铃,当然是信号反射,是阻抗不连续导致的!

当然,这个答案绝对没问题,但只能说是中规中矩,并无特色。那么你的得分也不会和别人有什么差别。而面试官凭什么要给你pass呢?

上面是从传输线理论维度出发,估计有个几年研发经验的小伙伴都能想到。如果你能另辟蹊径,从不一样的角度给出不一样的解释,那special offer估计就在向你招手了。

不一样的维度

振铃多出现在数字电路的信号跳变的边沿处,从0到1,从1到0。比如文章开头的波形图片,就是从1到0切换时发生振铃。

那为什么总是在电平切换时发生?

数字信号在电平状态切换时,陡峭的上升沿或下降沿,其中蕴含了非常丰富的频率分量,而且带宽极宽,频率覆盖范围很宽。这个,如果你学过信号与系统 或 研究过傅里叶变换,都会比较清楚。

当然,仅仅是频率范围宽并不会发生振铃。

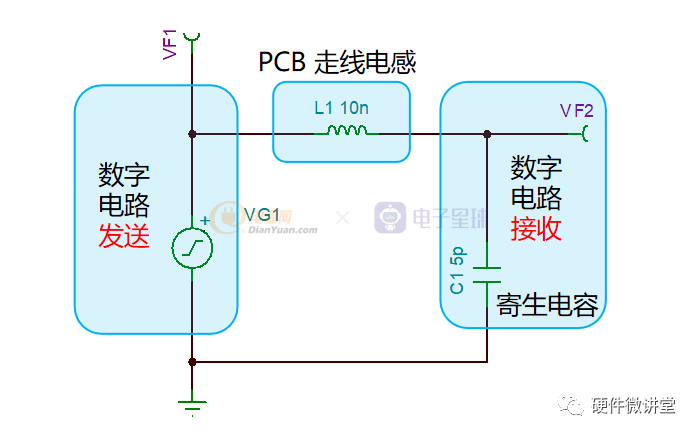

但关键是,数字信号电路都是通过PCB导线、芯片IC、阻容感等电路搭起来的。读过我前面文章的小伙伴应该知道:PCB板上的Layout走线,一般都会有寄生电感,nH级,而芯片端IO管脚也会有寄生电容,pf级。

电路中有了L和C,可能会发生什么?

LC谐振!

发生谐振会怎样?

选频特性,会使谐振点上的频率分量放大,而且是很多倍!再和原来的信号做叠加,就形成了振铃。

只是文字描述,你可能不太信服,那咱们仿真看看哈……

仿真分析

根据经验值,cm的PCB 走线,寄生电感大概为10nH。而芯片点输入端的寄生电容,姑且按5pf来估算(并不是很严谨)。如此,我们把数字电路发送和接收的模型搭建如下图所示。VG1为数字电路发送的激励源,设置为频率2MHz的方波。

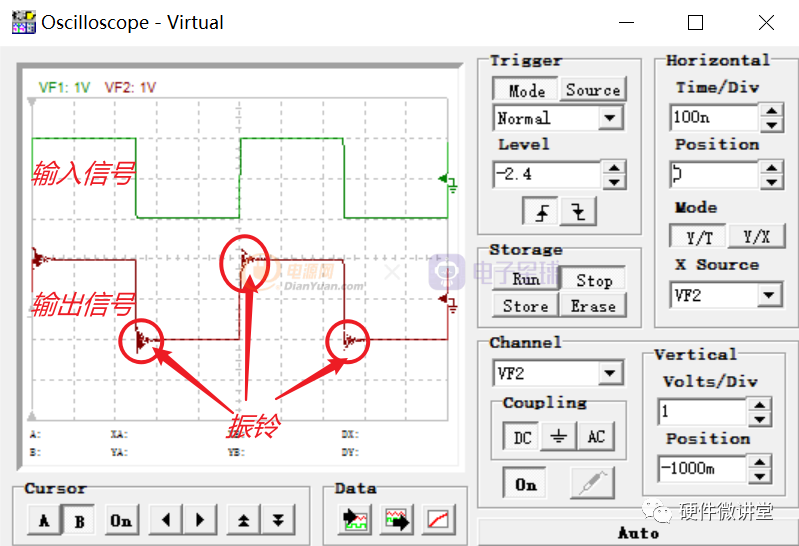

用示波器看下波形,如下图,输出信号画圈的部分,明显可以看出有“振铃”。

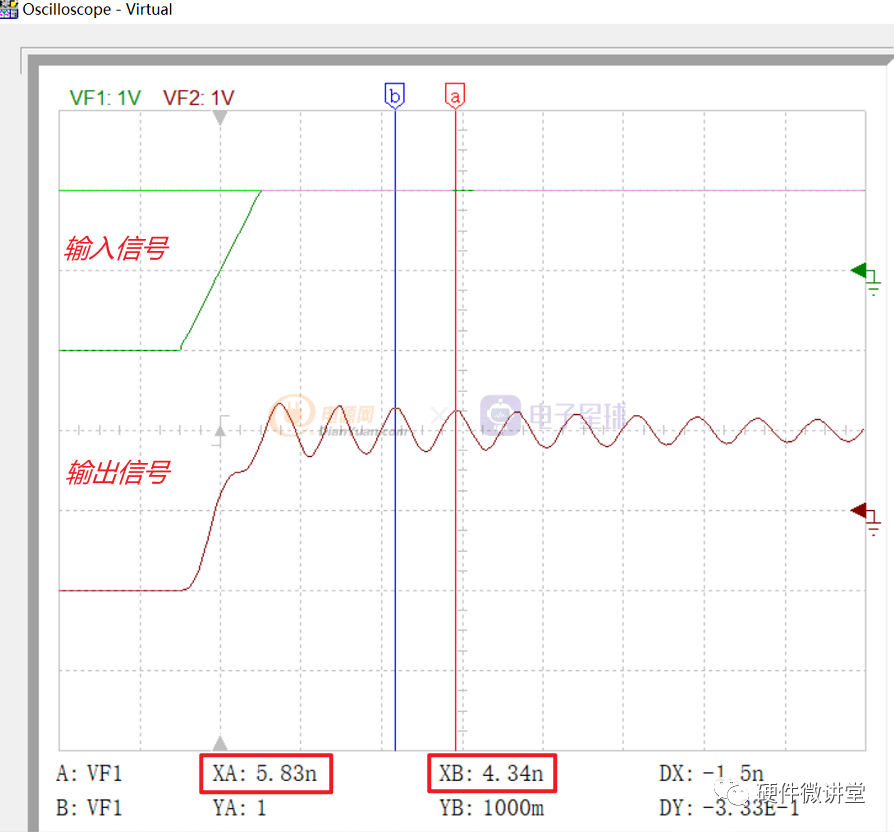

把时基从100ns调整到5ns,波形放大,如下图,可以看到明显的振铃波形。

当然,如果仅仅分析到这里,那只能说是有振铃出现,并没有找到我们想要的原因。浅尝辄止?不是我的调性。继续把波形放大哈…

继续放大波形,可以看到振铃波形呈现为一定周期的阻尼振荡。用光标卡一下时间,Xa=5.83ns,Xb=4.34ns,dX=1.5ns,由此可以计算阻尼振荡的周期f。

f=1/dX=666MHz

666MHz,是什么?不晓得,继续往下分析。

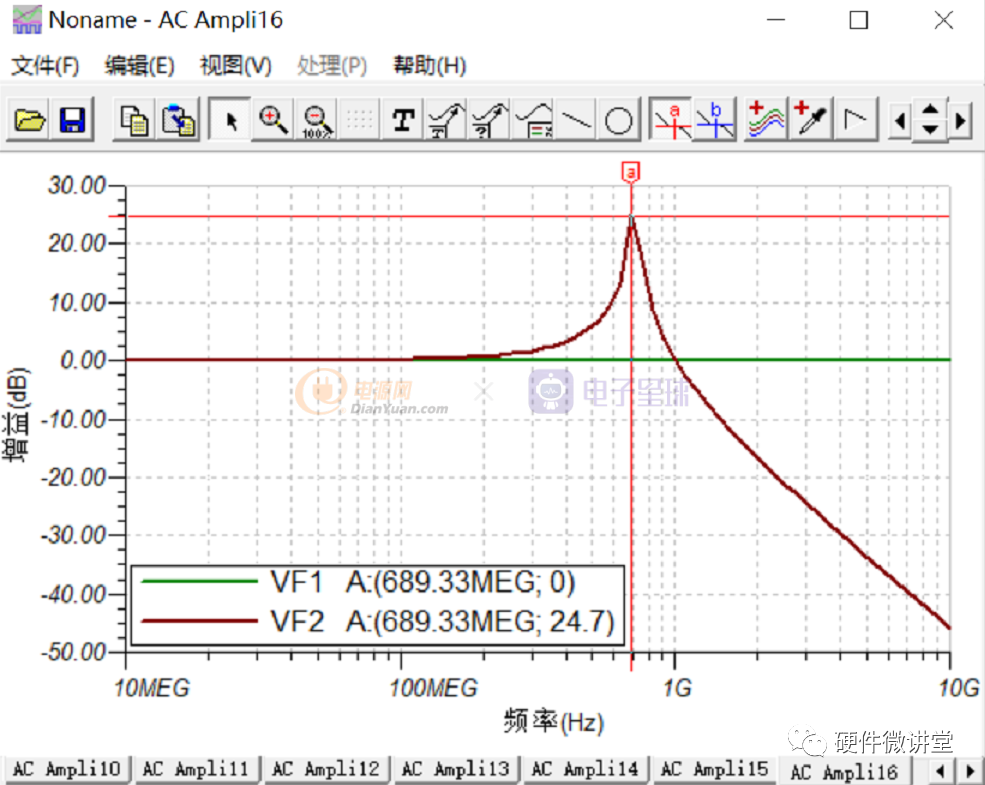

我们用交流分析看下这个电路的频率增益曲线,发现高频处有谐振点,谐振频率为689MHz,接近666MHz!

说明LC有发生串联谐振,并在该电路中充分展示了LC谐振的选频特性,把基频2MHz的666MHz的高次谐波分量选出并进行(将近)24dB的放大,再和原来的基波叠加,在输出信号上体现出振铃波形。

说到这里,再回过头看看前面说的:

①总在信号电平状态切换时发生;

②频率覆盖范围很宽;

③寄生电感和寄生电容;

④LC谐振,

⑤选频放大特性,

把这些都串在一起,理论分析结合仿真数据,这个问题是不是就很清晰了?

总 结

信号出现振铃,为什么?

维度1:从传输线理论维度,信号反射,是阻抗不连续导致的!

维度2:从LC谐振维度,LC有发生串联谐振,LC谐振的选频特性将信号状态切换时的高次谐波频率分量选出并放大,叠加到基波上进而形成振铃。

怎么样?一个简短的问题,给出的回答可浅可深,就看你对这个知识点的理解达到怎样的程度。你学废了么?

关注“硬件微讲堂”,硬件路上不慌张!