对于小于75W的开关电源的供电系统,我们没有强制要求增加PFC电路设计。此时<75W的单激方式的反激设计是系统供电设计最简单实用且实效的方案。

工作于开关状态的单激式设计,其开关电源的电压、电流变化率都很高,产生的干扰强度较大。干扰源主要集中在功率开关管,开关变压器,输出整流二极管等,其干扰频率不高(从几十千赫到十兆赫兹/也有超过十MHZ的),主要的干扰形式是传导干扰和近场干扰为主。

在EMI-传导的高效设计方面我的滤波器设计理论及推荐的共模电感设计可以一步到位,但往往电子工程师对理论研究比较薄弱,同时对成本应对问题,滤波器中的共模电感的参数是用凑合来的(成本最低)。我再将电子工程师朋友们遇到的EMI整改问题根据测试频段对应的干扰源头进行一下追加措施处理!

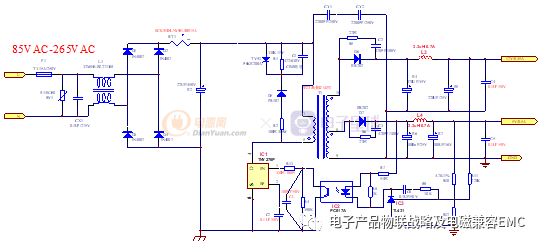

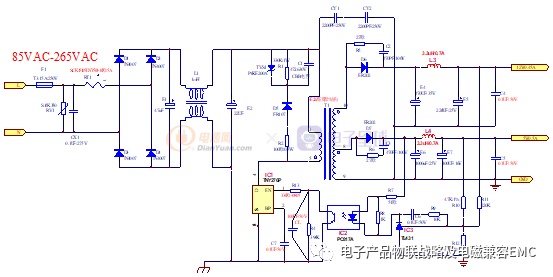

1.<75W中功率的应用设计原理图(通用设计参考)

图1 <75W 功率的较大功率段的通用设计方案

图2 小功率的系统的EMI通用设计方案

图3 小功率<15W的系统供电设计方案

图4 小功率<6W的系统供电设计方案

以上是我研究开关电源以来实施最多4种结构。注意其应用场合有比较大的差异,我有一门课程是来研究电子产品的供电系统设计的,依据产品认证要求不同,如果其结构选择不当,对产品的系统EMC会带来成本及整改的问题!

2.我先推荐大家开关电源EMI在不同频段的经验数据Data

A.<1MHZ,主要以差模干扰为主,可以采用差模干扰抑制的策略

B.1MHZ—5MHZ,主要是差模与共模的混合干扰为主

C.>5MHZ,主要是以共模干扰为主,可以采用共模干扰抑制的策略

D.30MHZ—50MHZ,辐射段大多为 MOS管的高速开关引起

E.50MHZ—100MHZ,辐射段大多为 输出整流二极管的反向恢复电流引起

F.>200MHZ,开关电源的辐射会比较小了;需要分析数字电路,时钟,MCU,CPU/RAM等高频控制信号;可以通过测试曲线的数据来大致判断来源!

3.通过上面的图1-图4说明开关电源EMI的实际整改策略--传导部分

1MHZ以内以差模干扰为主

◆150KHZ-1MHz,以差模为主,1-5MHz,差模和共模共同起作用,5MHz 以后基本上是共模。如图1将X电容增加大1uF,对比测试曲线是否有改善;有明显改善则是差模干扰。在电源线L,N用一大磁环绕上几圈, 干扰降低则是共模干扰。

◆保险过后再增加差模电感;

◆小功率电源可采用π型滤波器处理(建议靠近变压器的电解电容可选用较大些);如图3,图4;前端的π型滤波器,差模电感只负责低频EMI,体积別选太大(屏蔽电感最好)否則幅射不好,必要时可串磁珠,电感上并联电阻;

否则高频会直接通过电感分布电容耦合到前端。

◆测试150KHZ总超标的解决方案:

加大X电容看一下能不能下来,如果下来了说明是差模干扰。如果没有作用那么是共模干扰,或者把电源线L,N用一大磁环绕上数圈, 干扰降低则是共模干扰。

◆将输入高压电解电容改为低内阻参数的电容。

◆将共模电感上并联一个几K到几十K电阻。

◆在PCB布局设计时注意:共模电感和变压器距离不能过近以免互相干扰。

◆交流L,N输入端可以增加两只磁珠。

◆三线输入的将两根进线接地的Y电容容量从2.2nF减小到471或不加。

◆对于π型滤波电路有一个高压电解电容躺倒放在PCB上且靠近变压器时;

如果1MHZ以内的出现测试结果超标,改善方法可将此电容用一个1uF或者说0.1uF电容代替, 将另外一个电容加大。如图4

◆在共模电感前加一个小的几百uH差模电感。

◆对于结构紧凑的电源加大X电容只能解决150KHZ低频段问题,不能解决高频段的干扰,可以在电源线上增加一个铁氧体磁环L,N双线绕制大于3圈以上。

◆在整流桥上并电容,当考虑共模成分时,应该邻角并电容,当考虑差模成分时,应该对角并电容。

◆如果有输入差模电感设计可加大输入端差模电感。

1MHZ---5MHZ差模共模混合

采用输入端并联大容量X电容来滤除差摸干扰并分析出是哪种干扰超标。

在电源线L,N用一大磁环绕上几圈,干扰能降低则是共模干扰。

1.对于差模干扰超标可调整X 电容量,添加差模电感器,调整差模电感量。

2.对于共模干扰超标可添加共模电感,选用合理的电感量来抑制。

3.也可改变整流二极管特性来处理一对快速二极管如FR107一对普通整流二极管1N4007。图4的小功率电源可以推荐使用。

4.绕制变压器时将所有同名端放在一边,同名端在最里层对应开关MOS的D极和输出二极阴极。可降低1.0MHZ-5.0MHZ传导干扰。

5.加大Y电容,可降低传导中段1MHZ-5MHZ干扰。

6.对于无Y电容的充电器开关电源设计EMI在1MHZ-5MHZ超标,如加了Y电容后EM降下来了的话,就可在变压器初次级间多增加几层绝缘胶带或采用增加屏蔽绕组设计措施。

7.在输入端滤波电容上并联小容量高压瓷片或者高压贴片电容。如图1原理方案,在PCB设计时推荐加在变压器高压输入脚与变压器的辅助绕组的地引脚之间。

5M---20MHZ以共摸干扰为主,采用抑制共摸的方法。

1.对于输入有接地的产品,在地线上用一个磁环串绕2-3圈会对10MHZ 以上干扰有较大的衰减作用。

2.可将变压器增加屏蔽绕组的法拉第屏蔽设计;变压器外壳用屏蔽材料铜箔环绕一圈构成一回路加以屏蔽,铜箔形成闭环接初级地。

3.处理后端输出整流二极管的吸收电路和初级侧高压大电解电容并联小电容的设计(电容PCB放置位置是关键)。

4.将开关MOS管D极对地增加一小电容<220pF,注意变压器的初级起始端连接到MOS管D极。

5.将次级的散热片连接的输出地的同时用一个102的Y电容接到初级的高压电解电容的地端, 可降低导干扰。如图1的原理方案设计。

6.优化变压器的设计,控制变压器的漏感大小;调整RCD吸收电路。如图1

对于20--30MHZ

1.调整初次侧间的Y电容位置及参数值

2.在输出端增加一个双线并绕的小共模电感

3.在输出整流二极管两端并联RC吸收电路且调整到合理的参数

4.在变压器与MOSFET之间增加磁珠

5.在变压器的输入电压脚与辅助绕组地引脚增加一个小电容推荐2.2nF

6.可以增大MOS 驱动电路电阻等参数

7.可将开关MOS管D 端对地接一个101的电容;推荐值<220pF

8.在输出端增加共模电感,也可在输出端增加两只大电流的磁珠

开关电源设计后EMI的实际整改策略--辐射部分

30---50MHZ 普遍是MOS 管高速开通关断引起

1.可以采用增大MOS 驱动电阻

2.优化RCD 缓冲吸收电路,吸收二极管并联101-102的电容

3.或者输出线前端串接一个双线并绕的小共模电感

4.在MOSFET 的D-S 脚并联一个小吸收电路电容<220pF

5.在变压器与MOSFET D之间加BEAD CORE

6.在变压器的输入电压引脚与辅助绕组GND增加一个小电容推荐使用2.2nF

7.优化PCB=进行LAYOUT 时大电解电容,变压器,MOS 构成的电路环尽可能的小

8.优化PCB=变压器,输出二极管,输出平波电解电容构成的电路环尽可能的小

相关的细节可参考我的:《开关电源的EMC-分析与设计》

50---100MHZ 普遍是输出整流管反向恢复电流引起

◆可以在输出整流管上串磁珠;

◆调整输出整流管的吸收电路参数;

◆可改变初次级侧跨接Y电容支路的阻抗,如PIN脚处加BEAD-CORE;

增加Y电容-重点注意Y电容的放置位置等

◆也可改变MOSFET,输出整流二极管的本体向空间的辐射

(改变散热器的接地点)。

◆变压器增加屏蔽铜箔抑制向空间辐射-具体方法:变压器外壳用屏蔽材料铜箔环绕一圈构成一回路加以屏蔽,铜箔形成闭环接初级地。

200MHZ 以上开关电源已基本辐射量很小,一般可过EMI 标准。

4.开关电源EMI的对策处理在实际产品中的运用需要结合起来

我将关键的注意事项进行如下说明:EMI处理会事半功倍!

A.产品及设备外部构造的屏蔽处理;

B.产品外部的电缆线处理;

C.产品内部的电缆线处理;

D.PCB布局布线处理;60%的EMC问题都来源于PCB设计!

E.开关电源的振荡频率的选择;

F.开关电源IC型号的选择;IC厂家的选择;IC特性的掌握!

I.磁性材料的频率和带宽的选择;

J.变压器的选型、绕法和设计技术掌握;

K.散热器的接地方式的处理,Y电容外置的应用等。