大家好,我是广元兄。很高兴和大家分享信号完整性的相关知识。希望大家点赞,分享。有什么问题加微交流学习,微信号【SI_Basic】。

Slogan:一起学习,共同进步!

消费类的很多产品,很多公司只给出板厚,层数以及管控阻抗值,叠层的设计都是板厂来进行。随着产品的速率提升,叠层设计不再是PCB板厂的专属,已成为很多公司SI信号完整性工程师日常操作,正如系统的更新,跟上时代是永恒不变的主题。

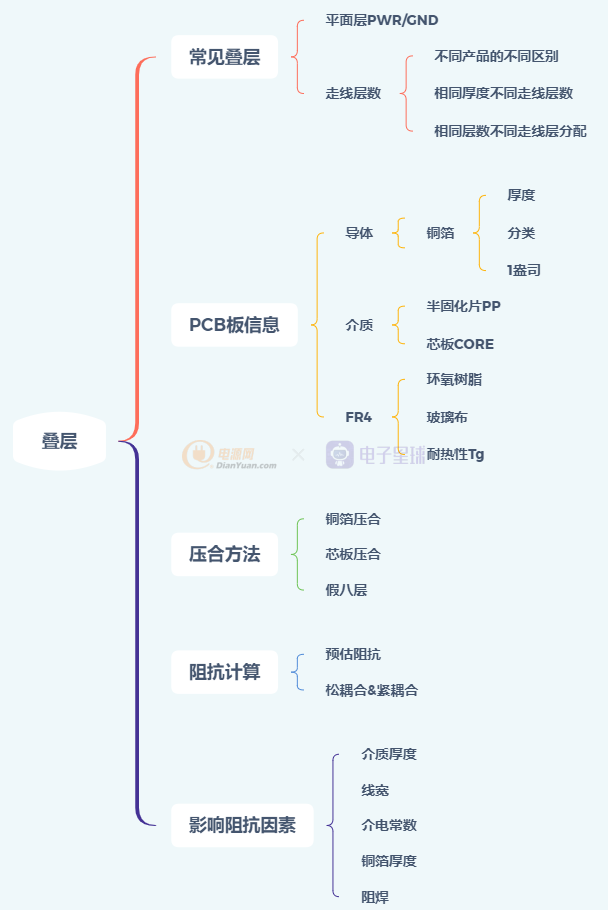

话不多说,上思维导图:

一般情况,叠层设计的考虑三大因素:

1.总厚度(产品的复用&机构设计的要求)

2.层数的确定(信号层,电源平面层&地平面层)

3.对称性(PCB生产中易于管控)

01.常见叠层

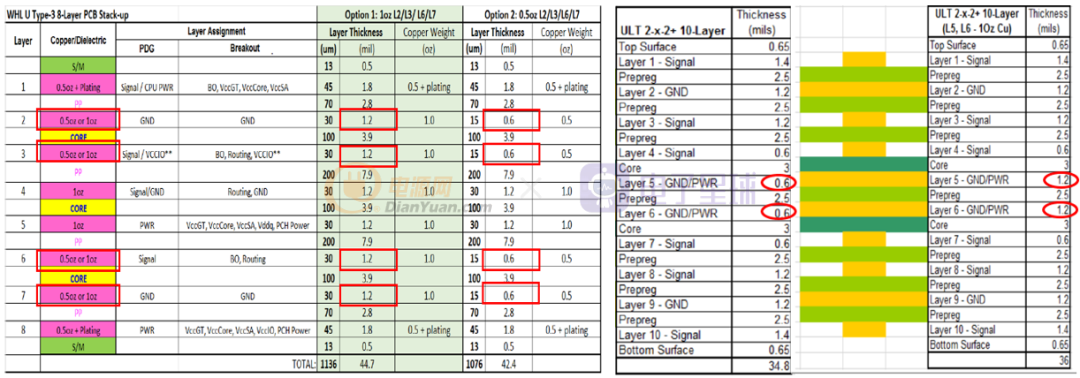

下图为Intel给出的某类产品的叠层设计建议。不管是8层还是10层,一般只会对电源平面层或PP做些微调。

从信号完整性角度来说,一般选用的叠层设计如下:

每个走线层都有GND参考平面层,来保证信号回流路径的完整性,从而保证信号的完整性。

产品是多种多样的,面对各式各样的产品,同样的厚度和总层数,走线层层数的区别是叠层最大的变数。

上图是Intel针对不同产品,给出同样4L走线层,而产生的不同的叠层设计。

标准从来就不是一个,认知才是。

02.PCB板信息

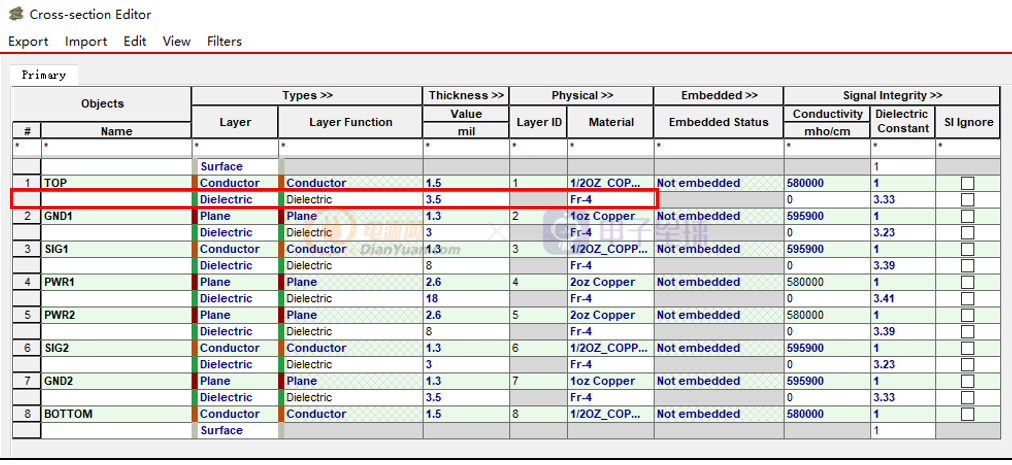

下图为我们日常工作中常用的Allegro版图软件查看设计中的叠层(Cross-section)信息:

先从叠层中Conductor讲起,Conductor代表导体层,用于信号传输。

印制电路板(PCB)中不仅仅有信号线,图形中的Plane(电源和地层)也基本都是由铜箔蚀刻得到的,也就是说,电路板中信号层、电源层和地平面层都使用铜箔作为导体来传递相关信号。Thinkness的1.5mil代表铜箔厚度,相对应后面Material部分中出现1/2 OZ+plating。

拓展知识点:

1.盎司(OZ)本身是一个重量单位。1OZ ≈28.35g。在PCB行业中,盎司是用单位面积的重量来表示铜箔的平均厚度。1OZ意思是重量1OZ的铜均匀平铺在1平方英尺(FT2)的面积上所达到的厚度。根据公式推出:

2.英制和公制的转换

1mil≈25.4um,1mm≈39.37 mil

搞清楚上面的知识点,回到原来的1.5 mil 处,算出来是17.5 um,和1.5 mil ≈38.1 um 是不是不相符。这里面牵扯到1/2 oz + Plating PCB 工艺的问题,以通孔(PTH)为例,压合完成后,需要对通孔镀铜,这个Plating就是做这样的事情,同时对面铜也做了电镀,所以厚度就增加了。当然,PCB厂家的不同,工艺也不一样,对应后面的厚度值也不一样。其实,上面截图中Solder mask 也是如此。

对叠层影响最大的就是铜箔厚度。常规的铜箔厚度有1/2oz、1oz、2oz 等,当然也有更厚的,一般电源类产品使用的铜箔比较厚,因为要承载电流。

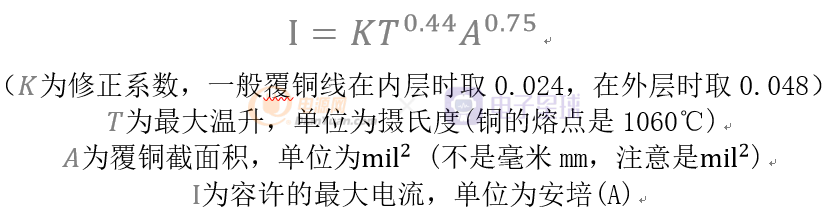

讲到载流,有这样经验公式:

实际应用中,常用经验值:1OZ铜箔40 mil宽度通流1A。

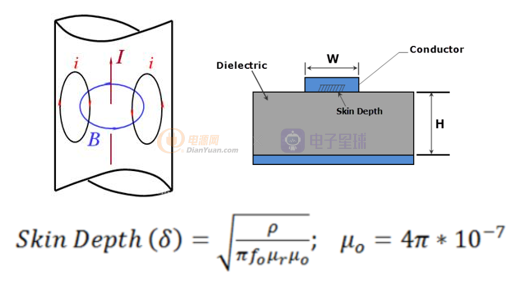

其实,铜箔的选择,除了厚度,还有一个粗糙度的因素。粗糙度考虑点是针对于高速信号而言,损耗分为介质损耗和导体损耗。铜箔粗糙度说的是导体损耗。平常我们看到的铜箔都是光滑的,而实际的印刷电路板(PCB)在压合过程中,为了提高铜箔和介质之间的附着力,有时候会做粗化处理,这时候铜箔就不是光滑的了。那不是光滑的,又会有什么影响?这里就衍生出一个趋肤效应的概念。

交变电流通过导线时,电流在导线横截面上的分布是不均匀的,导体表面的电流密度大于中心的密度,且交变电流的频率越高,这种趋势越明显,该现象称为趋肤效应(Skin effect)

通俗点讲,就是内部力量将导体内部电流挤到了导体表面。

本质上,“趋肤效应”一词用于描述电流在导体内的分布方式随频率及材料特性的变化。从上面公式来看,信号频率越高,导体内的电荷分布越趋向于导体表面处。无论是单纯线缆、同轴电缆、微带还是天线导体,所有导体中均存在这一现象。

由于趋肤深度为频率以及导体电阻率和磁导率相互作用的结果,因此不同导体材料的射频损耗随频率变化的特征不同。一般情况下,镍的损耗最严重,而铜和金的损耗要小得多。

回到前面,铜箔的粗糙度增大,由于趋肤效应的影响,信号沿着铜牙传输,对于在表面附近传播的电流而言,一个极其粗糙和不平整的表面相当于增加了其传播路径的长度,因此此类表面将导致更大的电阻性损耗。

铜箔的粗糙度不同,也有分类,这里不做展开。除了铜箔,叠层设计中还有介质:

介质分为PP(半固化片)和芯板(CORE)。

Dielectric就是叠层里的半固化片( Preimpregnated, PP ),芯板(CORE)就是半固化片双面包铜。

我们的PCB(印制电路板)多层板其实就是Core与Prepreg压合而成的。说到PCB,必须说说FR-4,需要注意的是FR-4不是一种材料的名称,它是一种材料等级,准确地说是一种耐热材料的等级。FR-4等级材料有很多的种类,一般印刷电路板(PCB)所用的FR-4等级材料是由环氧树脂加上填充剂(Filler)以及玻璃纤维所做出的复合材料。

FR-4的分类,分类有很多种方式,这边给出常见的两种:

玻璃布分类(106,1080,2113,3313等);

损耗级别分类(低损耗板材,中损耗板材,普通损耗板材等)。

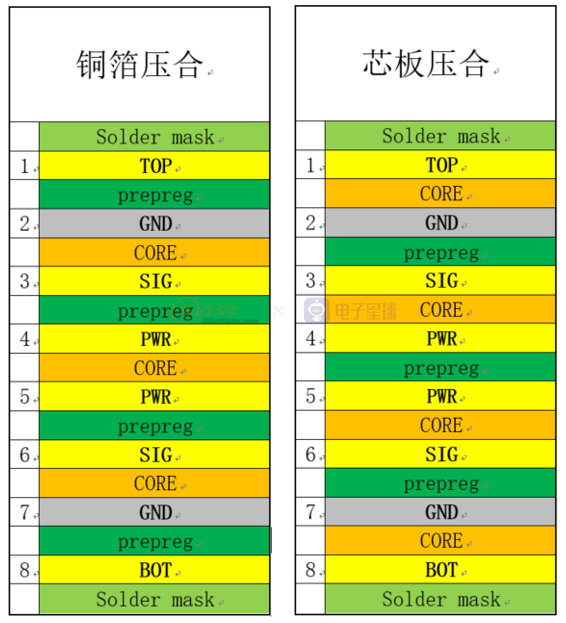

03.压合方法

叠层设计中常见的有两种方法:铜箔压合和芯板压合。至于这两者的区别,直接上图:

在实际工作过程中,成本的因素,铜箔压合更为常用。

这里穿插讲一下假八层 (实际是真六层板)。

有些产品六层板的板厚比较厚,比如2 mm,在叠层的设计上,会导致3、4层之间的厚度比较高,会超过3张7628半固化片的厚度。同时,工艺管控的问题,PP最多叠3张。这时候的解决方式是:通常会用没有铜皮的芯板或把芯板两面的铜箔蚀刻掉,加在3、4层之间来辅助达到预期的层叠厚度。用类似于八层的叠层设计做出六层板。

04.阻抗计算

叠层的铜箔及介质的选择和阻抗有很大的关系。实际工作中,用阻抗的计算工具Polar,算出我们需要的阻抗对应的线宽线距,一般计算40Ω,50Ω单端阻抗,(85Ω,90Ω,100Ω)差分阻抗线宽线距计算的相关参数信息可以参考板材厂商给的datasheet。需要注意的是这里面阻抗值是估算,因为PERPERG和CORE的厚度实际上是压合后的厚度。

这里面讲一下松耦合和紧耦合的问题。直接上图:

比较上面两个线宽线距,对应的阻抗都是差分85Ω。

紧耦合线宽会细一点,信号传输速率越高,从趋肤效应上来说,导体损耗就会越大。这时候,估计有的人会说,那实际PCB设计差分走线中,我们就选松耦合。

其实给出松耦合和紧耦合,只是让大家有概念。实际的工作中,这个问题,没有任何探讨,走线密度不同会引起层数是否增加,层数是否增加就会引起成本的变化。

你觉得那点损耗跟成本比,算什么?

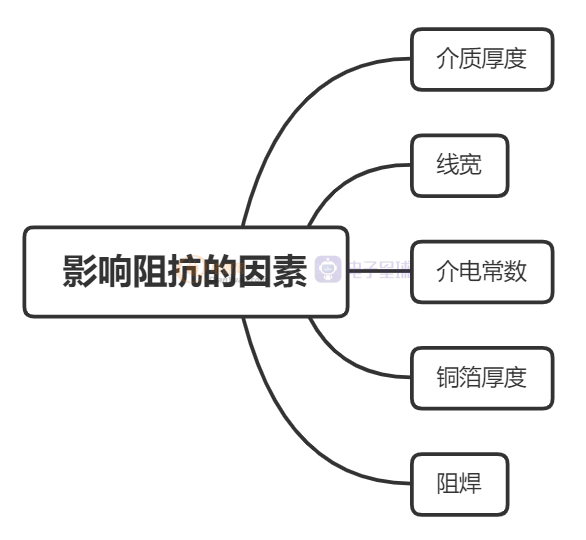

05.影响阻抗的因素

实际工作中,因为产品的产量及日程,会给几家PCB板厂来做,各家制程的问题,阻抗的匹配需要中和调整,来满足各家PCB板厂。所以,需要了解影响阻抗的因素有哪些:

以上的因素中,介质厚度的影响最大。所以,PCB板厂一般是微调介质厚度来管控阻抗。

06.总结

信号完整性工程师会根据经验或产品要求,结合以上知识点,给出一个叠层设计。各个板厂拿到叠层设计,也会根据自身制程能力,调整相关材料或厚度,给出相应的叠层设计。因为叠层厚度有公差(+/-10%),一般来说,是完全能涵盖各家的制程,管控好阻抗和相关指标的要求。